IIC总线解析

IIC简介:

IIC 即Inter-Integrated Circuit(集成电路总线),这种总线类型是由飞利浦半导体公司在八十年代初设计出来的,主要是用来连接整体电路(ICS) ,IIC是一种多向控制总线,也就是说多个芯片可以连接到同一总线结构下,同时每个芯片都可以作为实时数据传输的控制源。这种方式简化了信号传输总线接口。

IIC的主要构成只有两个双向的信号线,一个是数据线SDA,一个是时钟线SCL。

IIC主要特点:

具有多机功能,该模块既可以做主设备也可以做为从设备

IIC主设备功能,主要产生时钟,产生起始信号和停止信号

IIC从设备功能,可编程的IIC地址检测,停止位检测

支持不同速率的通讯速度,标准速度(最高速度100kHZ),快速(最高400kHZ)

IIC通信过程:

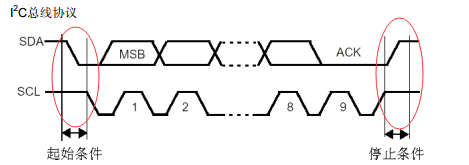

主模式时,IIC的接口启动数据传输并且产生时钟信号。串行数据传输总是以其实条件开始并以停止条件借宿。起始条件和停止条件都是在主模式下由软件产生控制的。

从模式时,IIC接口能识别它自己的地址(7位或者10位)和在数据总线广播的地址(好比每个人都有不同的身份ID,叫到哪个哪个就发生应答),同时软件能够控制开启或者禁止广播呼叫地址的识别。

数据和地址按照8位每个字节来传输,高位在前。跟在起始条件后的1或者2个字节是地址(7位模式为1个自己,10位模式为2个字节)。地址只能主模式发送。在一个字节传输的8个时钟后的第九个时钟期间,从模式接收后必须回一个ACK给发送器,这样才进行数据传输。

提醒:在IIC空闲时候,SDA ,SCL 都是保持高电平。

起始信号:在时钟SCL保持高电平,然后SDA数据线是从高电平变为低电平表示起始信号;

停止信号:在时钟SCL保持高电平,然后SDA数据线是从低电平变为高电平表示停止信号;

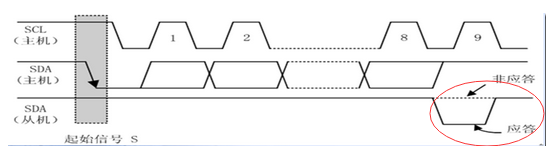

应答信号:主机发送完一个8为数据后,会等待从机的回答一个ACK信号就是SDA将会拉低。

每一个字节必须保证是8位长度。数据传送时,先传送最高位(MSB),每一个被传送的字节后面都必须跟随一位应答位(即一帧共有9位)。如果一段时间内没有收到从机的应答信号,则自动认为从机已正确接收到数据。

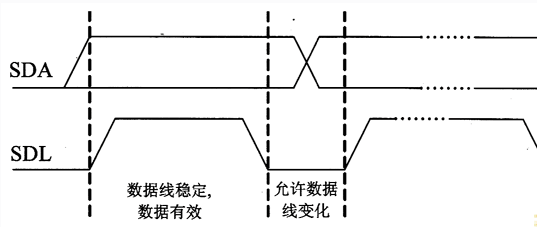

在 IIC总线进行数据传送时,时钟信号为高电平期间,数据线上的数据必须保持稳定,只有在时钟线上的信号为低电平期间,数据线上的高电平或低电平状态才允许变化,否者找成数据发送失败。

下面说一下IIC的读写过程,这里的以都以主的角度来说。

以AT24C02与2440连接IIC通信,AT24C02为从,2440为主。

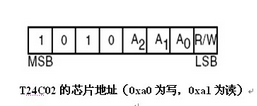

AT24C系列EEPROM芯片的固定部分为1010,A2,A1,A0引脚接高低电平后得到确定的3位编码,形成7位编码即为该器件的地址码。

最后一位R/W表示是要读还是要写 ,0为写入,1为读出

IIC读

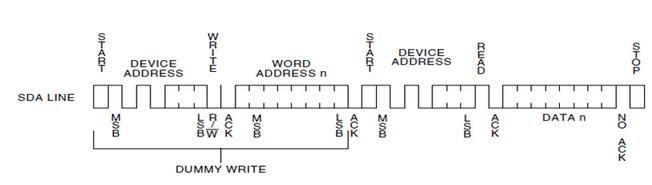

单片机先发送该器件的7位地址码和写方向位“0”(“伪写”),发送完后释放SDA线并在SCL线上产生第9个时钟信号。被选中的存储器器件在确认是自己的地址后,在SDA线上产生一个应答信号作为回应。

然后,再发一个字节的要读出器件的存储区的首地址,收到应答后,单片机要重复一次起始信号并发出器件地址和读方向位(“1”),收到器件应答后就可以读出数据字节,每读出一个字节,单片机都要回复应答信号。当最后一个字节数据读完后,单片机应返回以“非应答”(高电平),并发出终止信号以结束读出操作。

随机读

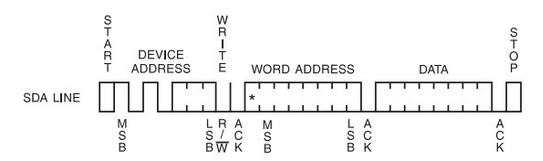

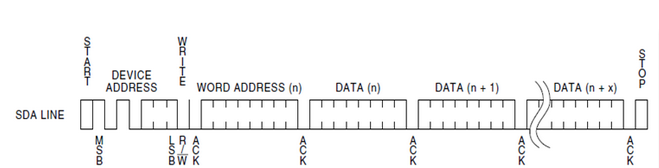

IIC写入

单片机进行写操作时,首先发送该器件的7位地址码和写方向位”0”(共8位,即一个字节),发送完后释放SDA线并在SCL线上产生第9个时钟信号。被选中的存储器器件在确认是自己的地址后,在SDA线上产生一个应答信号作为响应,单片机收到应答后就可以传送数据了。传送数据时,单片机首先发送一个字节的被写入存储器的首地址,收到存储器器件的应答后,单片机就逐个发送数据字节,但每发送一个字节后都要等待应答。AT24C系列片内地址在接收到每一个数据字节地址后自动加1,在芯片的“一次装载字节数”限度内,只需输入首地址。装载字节数超过芯片的“一次装载字节数”时,数据地址将“上卷”,前面的数据将被覆盖。

字节写入

页写入

本文部分参考其他书籍,没有说明出处,请见谅!

浙公网安备 33010602011771号

浙公网安备 33010602011771号