P4-verilog实现mips单周期CPU

最近对学习的掌控可能出现了问题,左支右绌,p2挂了,p2、p3、p4、p5每周在计组花的连续时间少了很多,学习到的东西也少了很多,流水线都还没真正开始写,和别人比落后了一大截,随笔自然就荒废了,我得尽快调整状态,下决心只要学不死,就往死里学,尽快迎头赶上鸭!!

由于p4断断续续做的,现在临考前来总结一下p4,顺便恢复一下记忆,对Verilog命名规范、p4设计CPU技巧、实现细节等等进行初步总结,如有不对烦请指正。

一、Verilog设计单周期CPU流程

由于p3和理论部分我们已经掌握了单周期CPU的理论知识,也对CPU的实现有形象化的认识。我们要做的就是“翻译”一遍。

我主要是先设计CPU文档,再用Verilog描述CPU。

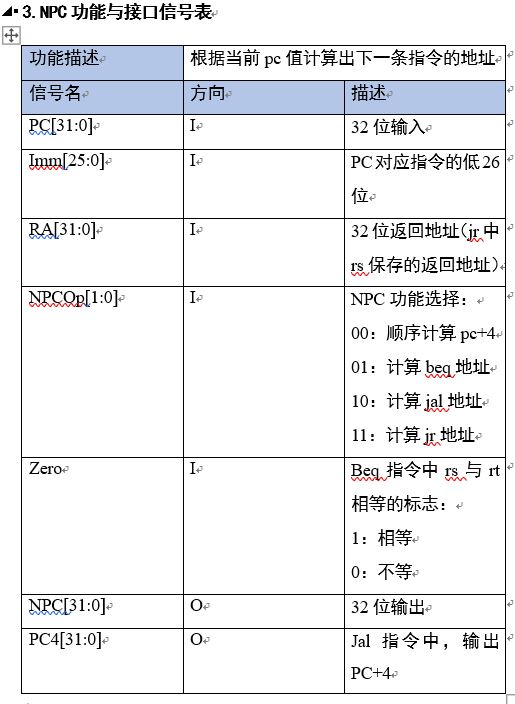

1.画出各个部件的端口及功能定义表,定义各个基础部件的端口,描述部件的功能。在这里我们不需要考虑部件功能的实现细节,只需要遵循高内聚低耦合的特点划分部件,将各个部件的功能描述清楚就可以了。

关于部件的划分,在这里我主要遵循高小鹏老师的《计算机组成与实现》,单独设计了NPC组合逻辑部件,将求beq,jal等跳转指令的地址都放到这里来,我认为在设计单周期CPU时会显得更加清晰,不容易出错。

关于各个部件的命名规范,我稍后再提。

大概表头设计如下:

2.设计各条指令的数据通路,同时修正扩展第一步中相应模块的端口和功能。

在这里其实理论上可以建一个以指令为列各个部件端口为行的表格,但我最初是在word里画的,所以把他拆分成了各个部件。

表头列出单个部件的信号端口(输入端)和驱动源(其他部件的输出端),各条指令,我称之为数据综合表:

由图所示,表头设计好了,需要的做的只是按照每一条指令数据通路进行填空而已,在这个过程中,如果需要对部件端口功能进行修改扩展则及时修改扩展。

填表的过程就相当于在logisim中连线,这样就不要照着图就能设计出Verilog描述的CPU了。

注意:端口名称需要严格按照之前表格里的名称来写,方便后面verilog的描述。

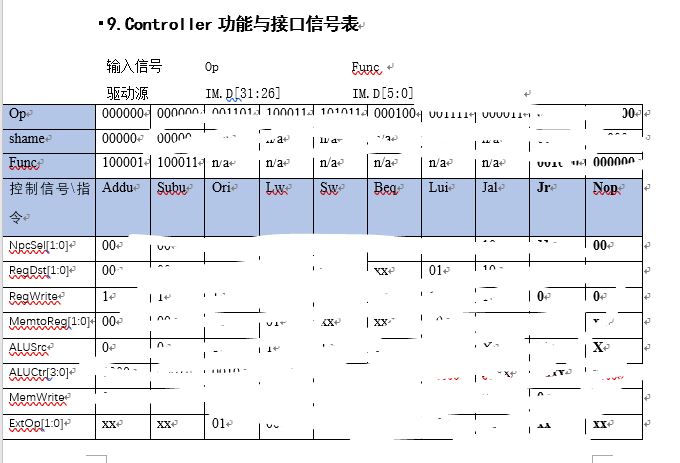

3.综合数据通路 初步构建Controller

如上表所示,综合数据通路的过程就是添加多路选择器以及描述控制器的过程。

四、构建Controller端口与功能表

直接上图,关注表头:

端口定义也可从图中获得。

4.利用上述端口与功能定义表使用Verilog描述各个部件和多路选择器(包括controller)

注意:实验中reset需要对所有时序部件(包括GRF DM PC进行同步复位,不包括IM);

理解:将CPU看成大型的有限状态机,复位代表保存的状态全部清零。

5.描述数据通路

利用设计的数据通路综合表,就能知道端口之间的连接关系。

用Verilog描述时,由于需要模块实例化,不同部件端口不能直接相连,必须使用wire型作为媒介,命名规范之后提。

6.测试程序

二、描述Controller的方法

我是采用assign赋值、和或逻辑,

或逻辑就是或门;和逻辑可以利用三目运算符从而代替直接描述logisim中的门级描述,避免出错。

例如 assign subu=(Op==6'b000000&&Func==6'b100011)?1:0;

至于if-else和case语句我觉得并没有更简单,宏定义我就想不到了,评论区可以指正完善我的思考题orz。

我的P4 Verilog的命名规范(尝试总结,试行版)大概率P5要修改

1.各部件端口定义与功能表

杜绝单纯的I O 等毫无意义千篇一律的设置。

在填写表格时,可以PC.DO 部件名+.+端口名

DO DI WD RD Addr 只要在表格中写清楚就好·····注意大小写

2.在写数据通路时,wire和各个部件的输出端口同名,从而确保CPU连接的正确性

PC.DO -> PCDO去掉.

特殊情况下须标注

3.多路选择器按顺序命名Mux1 Mux2 Mux3 实例化时改为M1 M2 M3

好像没有要强调的啊。。。。啊先这样吧

加油鸭!

浙公网安备 33010602011771号

浙公网安备 33010602011771号