组原2

PPT汇总 存储器的bank一般译成存储体

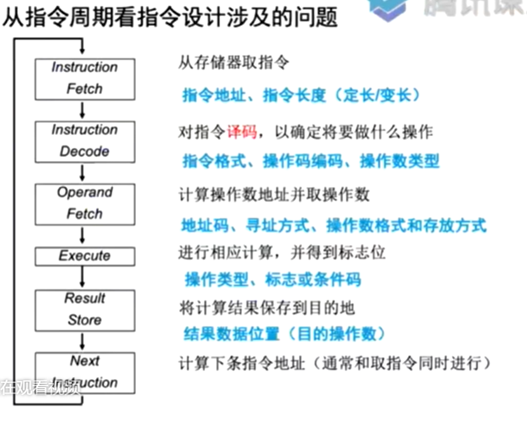

第四章 指令系统

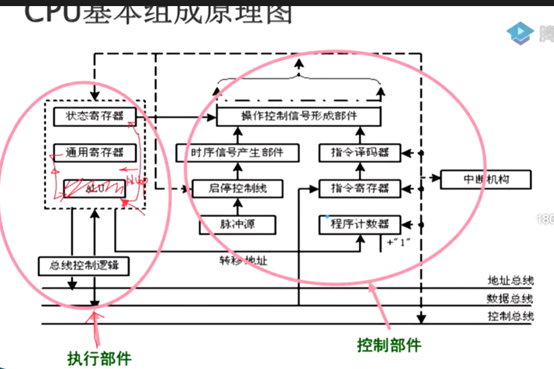

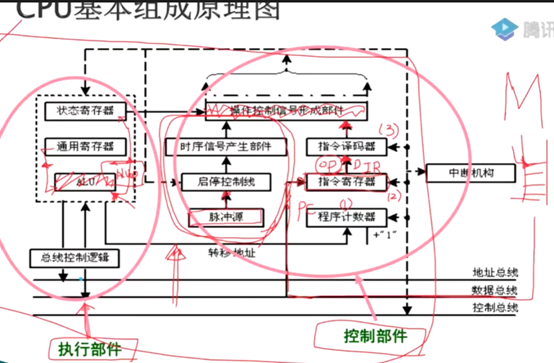

CPU

寄存器的内部结构

MIPS2

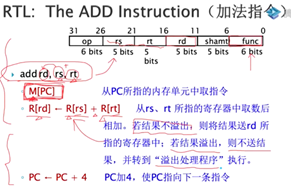

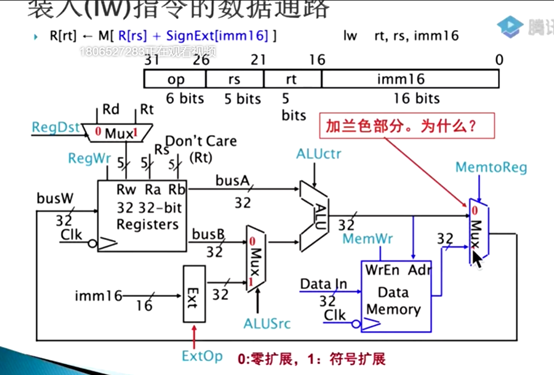

用rtl语言描述对内存进行访问,前面用M进行标记,同理R[]是指对寄存器进行访问。

M[PC]是指从pc所指向的内存单元去取数据/指令

Pc里面存放的是地址值

Pc里面存放的是地址值

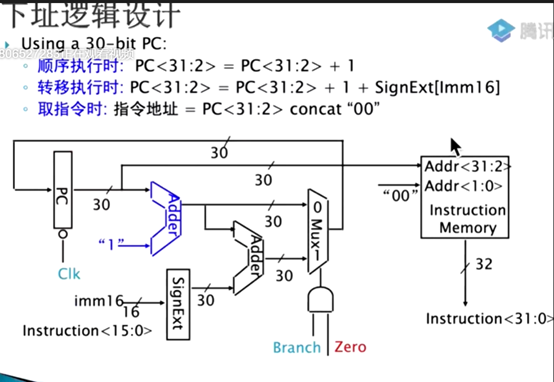

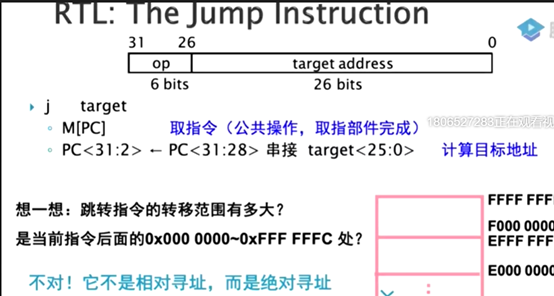

无条件转移指令

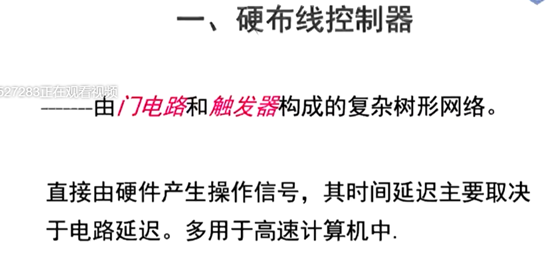

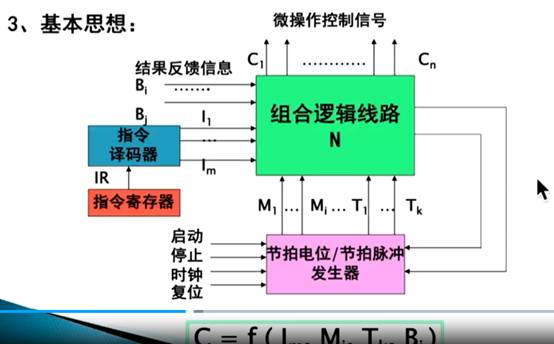

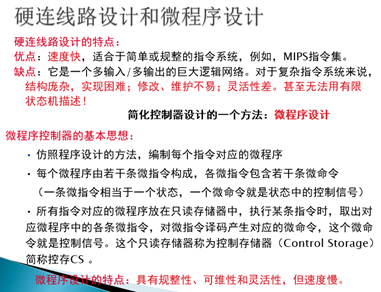

控制器

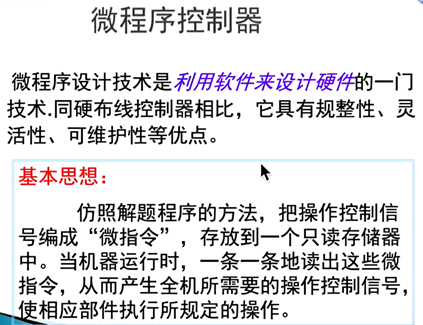

微程序控制器

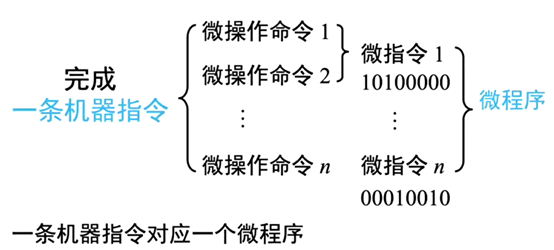

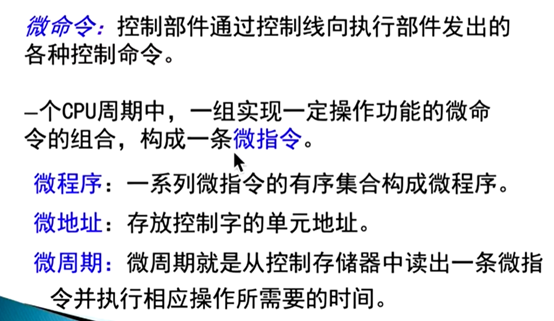

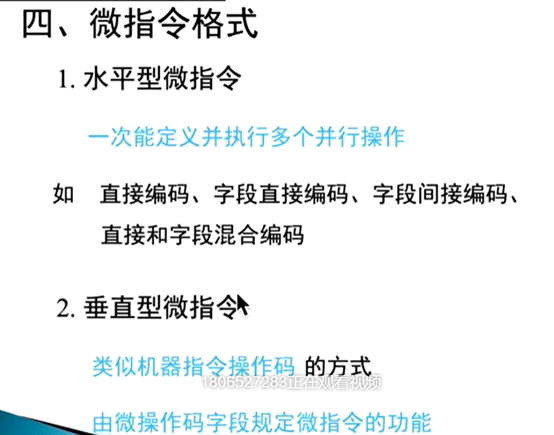

【关系:一条机器指令对应一个微程序,而一个微程序由若干条微指令构成,一个微指令由若干个微操作命令组成。】都是存在ROM中的。

---所以将这种控制器设计方式方式称为存储逻辑

微操作是执行部件接受命令后进行的操作,微操作在执行部件中是最基本的操作。分为相容性微操作【同时或在同一个CPU周期内可以并行执行的操作】和相斥性微操作。

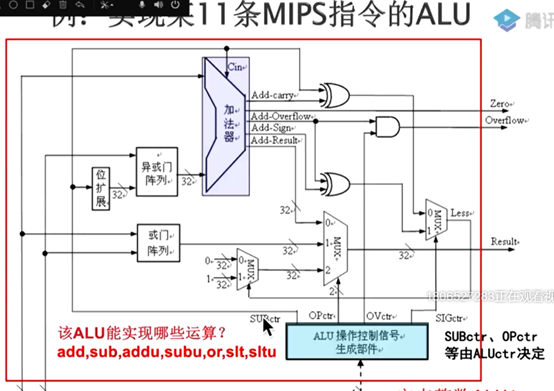

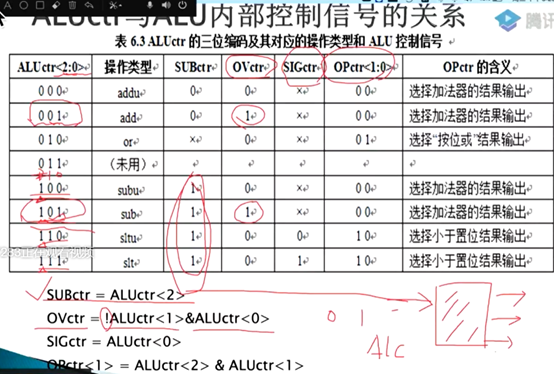

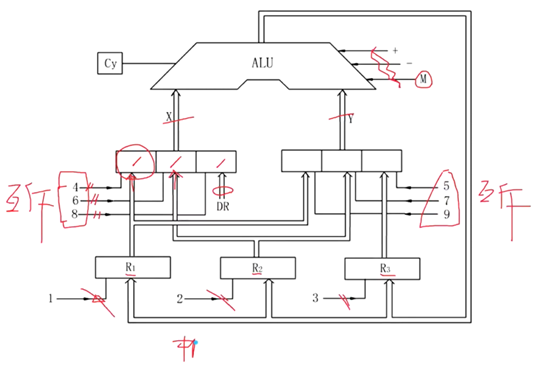

这是一个运算器(ALU)啊 +-M那线条画成那样,是说明他们是三个控制信号;

ALU输出之后回到R1R2R3,旁边的1,2,3都是写使能端。时钟信号没画,因为大家都在一个时钟内,ALU的输入是X,Y,分别有三块输入(egX:R1,R2,DR)以及三块输入控制信号(eg4,6,8)(决定X/Y的输入是否是这个来源)4,6,8当然是互斥微操作 而1,2,3是相容性微操作 +-是相斥性微操作

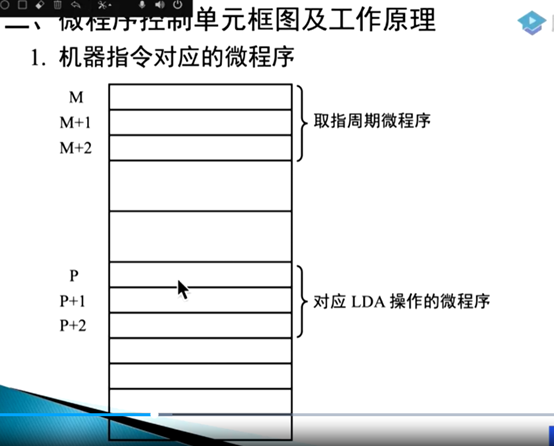

(事先存储好,需要的时候取出来)所有指令对应的微程序可以全都确定下来,存放到ROM里去,当指令集确定好,ROM的内容也就确定了

微指令在ROM中的位置就是微地址【左侧】

一行一行的是微指令

一条机器指令对应一个微程序,由n条微指令构成 微程序都存放在一个ROM里

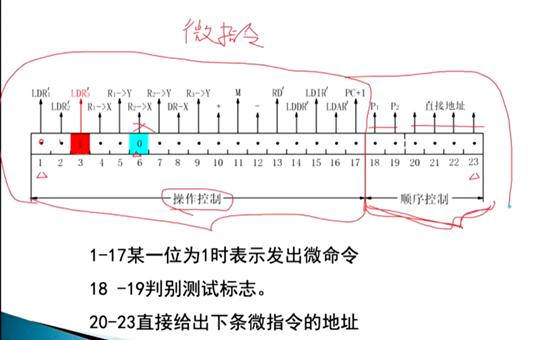

这是一条包含23位的微指令,操作控制字段其实就是微命令 微命令取出来之后其实就可以直接或者间接去形成控制信号,微命令的每一位都对应着数据通路的一个操作信号

当不满足测试条件时,直接根据后面四位的地址去访问相应的ROM

如果满足条件,就去修改这个直接地址,得到下一条微指令的地址去访问rom【这是一条全水平型微指令:微操作直接对应控制信号】

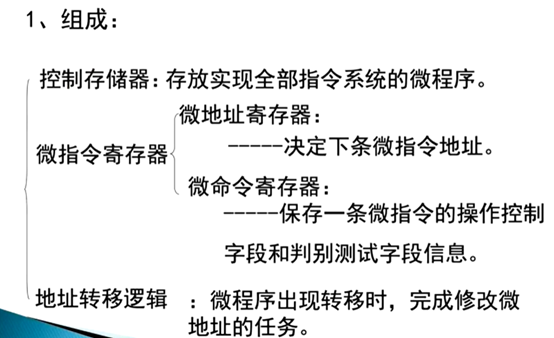

微程序控制器的组成

ROM【控制存储器 存放指令】 取出来的微指令,有个地方能存放它:【微指令寄存器】

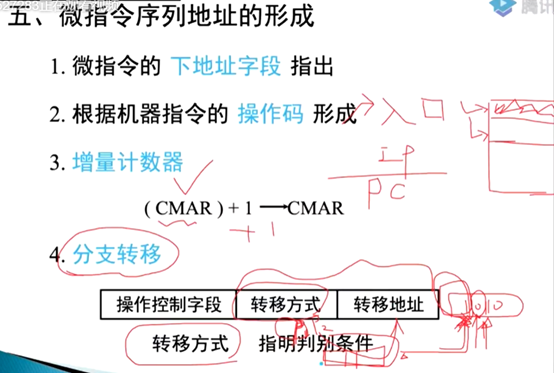

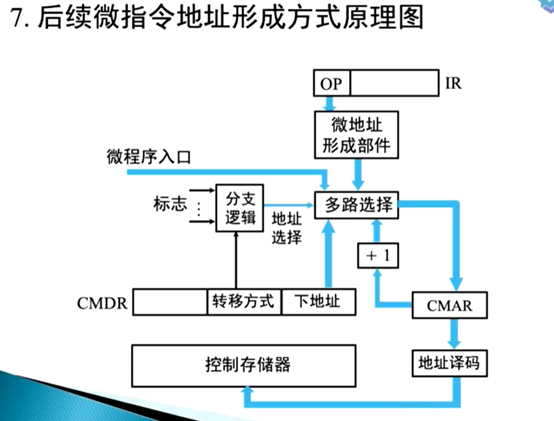

微地址寄存器和地址转移逻辑一定相连,在地址转移逻辑计算出正确的地址值就会送到微地址存储器,微地址寄存器再去访问控制存储器去取指令

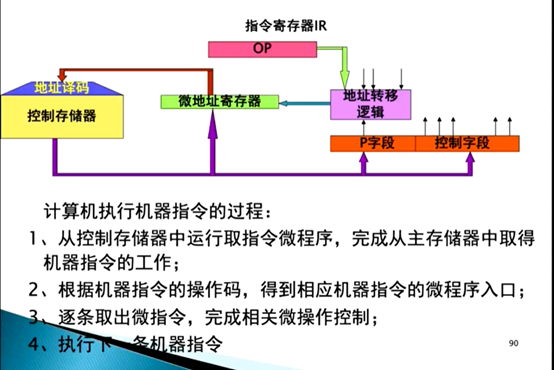

微程序控制器工作的过程

机器指令,当前执行时所需要的控制信号,由微程序实现,从指令寄存器IR中取出指令并译码

操作码送到地址转移逻辑,得到在控存[控制存储器/存储各个微指令的,由地址对应]中的一个入口地址,把入口地址送往微地址寄存器保存,再由他去访问控存,在控存找到入口处的第一条微指令,取出指令,送往微指令寄存器(红色部分)

P字段和控制字段:微指令寄存器 形成相应的控制信号 和下一条微指令的地址

直到这个微程序所有的微指令全都执行完,那么这个机器指令就实现liao

两条微指令的实现之间有时间差,有先后顺序

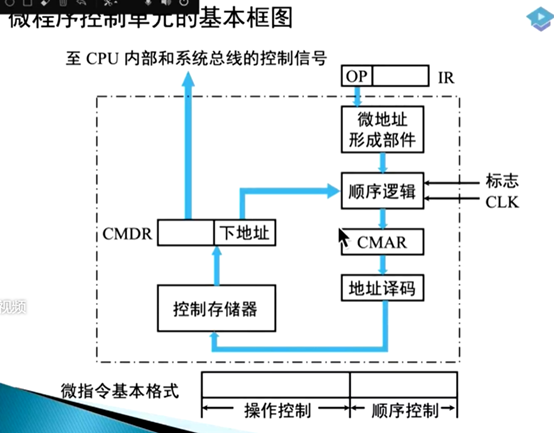

将操作码字段送往微地址形成部件,顺序逻辑[下址逻辑]根据上面送过来的地址值以及一些状态标志位,来产生下一条微指令的地址[maybe转移]或者是要访问的微指令的地址【一开始时入口地址无需转移直接送往CMAR】

MAR:存放地址的 C:控存 所以之后将地址译码,得到地址,在控存中查找找到相应的微指令,微指令的微命令字段就是操作信号,后面的顺序控制字段就是下一条微指令的地址

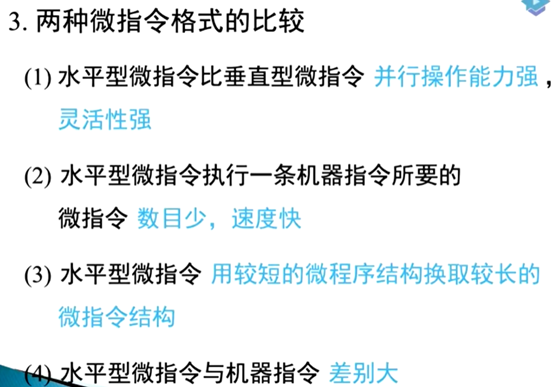

微程序的入口地址,只有这个是通过机器指令的操作码形成的 后续的微指令则不是这种方法【增量计数器或者分支转移方法】

微程序的入口地址,只有这个是通过机器指令的操作码形成的 后续的微指令则不是这种方法【增量计数器或者分支转移方法】

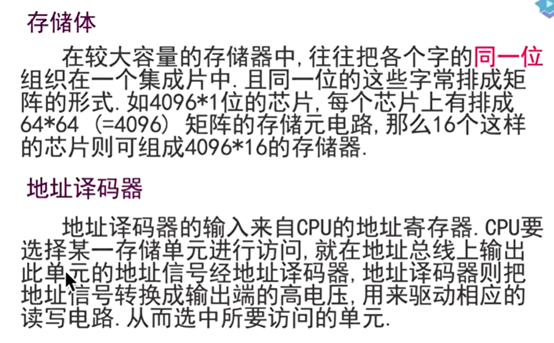

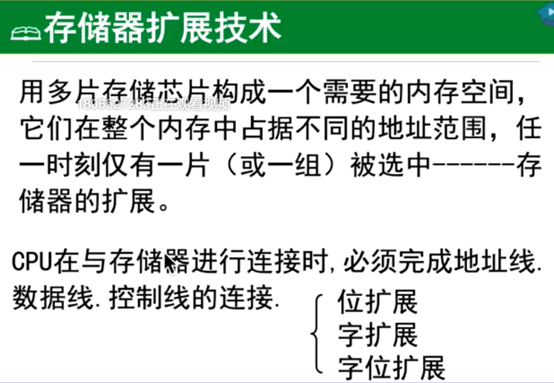

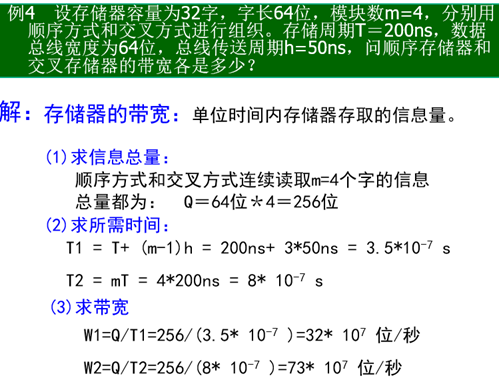

存储系统1

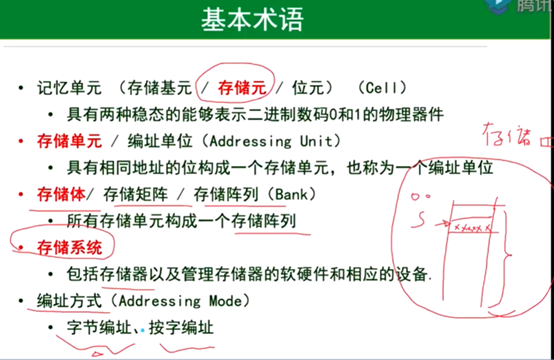

一排是一个存储单元,一个存储单元由多个存储元构成

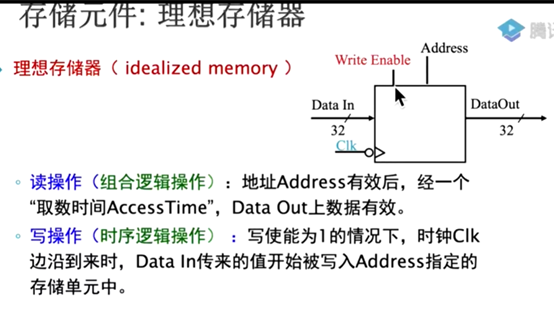

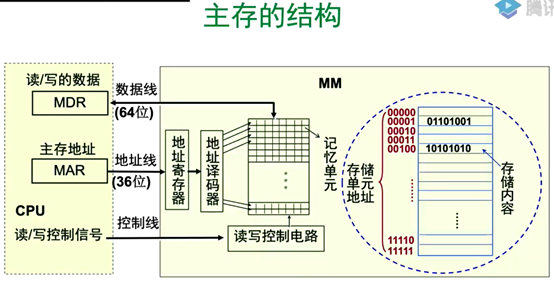

CPU访问内存时的两个寄存器:MAR[地址],MDR[指令或者数据]/寄存器自然是在CPU中

MDR定义:

全称memory data register主存数据寄存器。

MAR定义:

全称memory address register主存地址知寄存器。

MDR 和MAR作用:

计算机中的主存数据寄存器(MDR),与主存地址道寄存器(MAR)帮助完成CPU和主存储器之间的通信,MAR用来保存数据被传输到的位置的地址或者数据来源位置的地址。MDR保存要被写入地址单元或者从地址单元读出的数据。

CPU和主存之间的访问过程【MAR MDR必须画】

CPU和主存之间的访问过程【MAR MDR必须画】

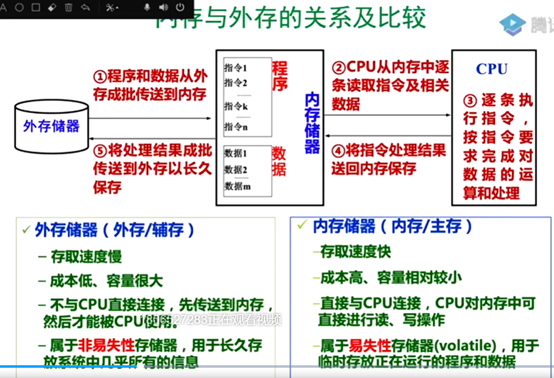

内存中存放的是指令和数据,CPU在执行指令时会去访问内存【CPU就是干取指令执行指令的事情】,地址线36位,能得到2^36种搭配,从而通过驱动线指向不同的地址存储单元。

这2^36都是物理地址,相当于一个个房子,但房子的具体大小是不确定的,所以通过指令得到地址到达房子后【记忆单元】,可以取出数据,再送回到CPU中【64位也是合理的】

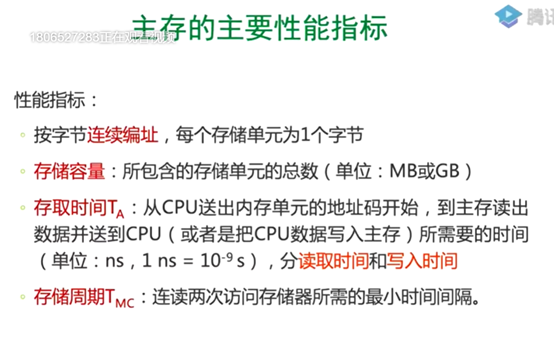

Tmc>=Ta

Tmc>=Ta

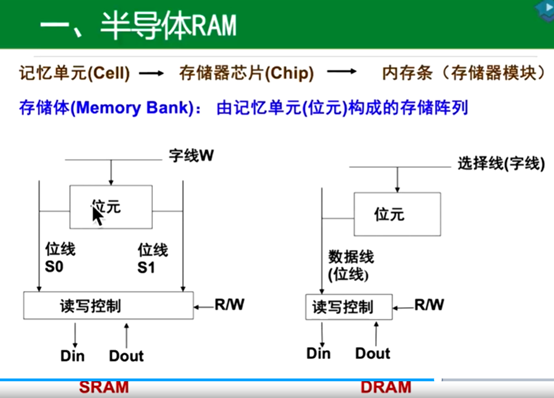

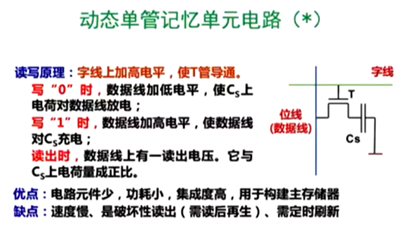

这是一个记忆单元[位元],里面是一位0/1信号;R/W:读写控制信号 SRAM:要访问一个单元首先要选中它,所以字线跟地址信号有关[联系上上面的驱动线了,地址寄存器 地址译码器 过来的就是这]

位线有两个是因为看低电平还是高电平有效

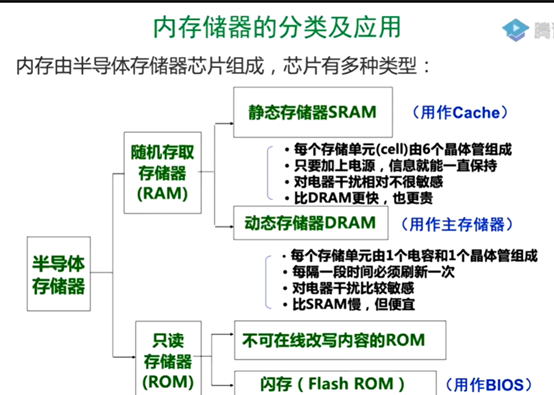

DRAM相比SRAM所用器件少一些,芯片面积小一些,所以相同面积上DRAM的位元就多一些,存储信息量更大

mos晶体管不考

mos晶体管不考

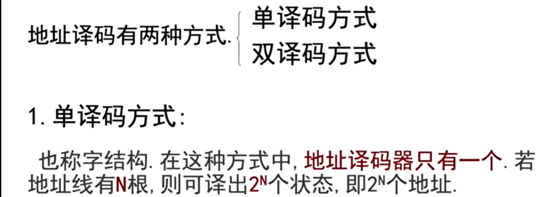

要正常的访问一个存储器还需要辅助电路的

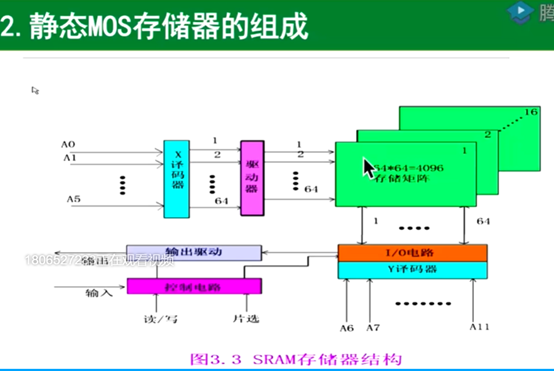

绿色的是记忆单元,很多个cell排列成矩阵形式

对地址进行译码:访问时分为行和列 A0-A5送往行译码器 A6-A11送往列译码器,同时译码:双译码

选中了一个cell,通过i/o电路再输出【X译码器选中就选中了一行 64个存储单元,需要驱动器帮忙带起来】

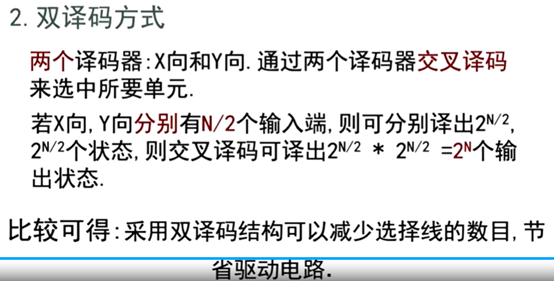

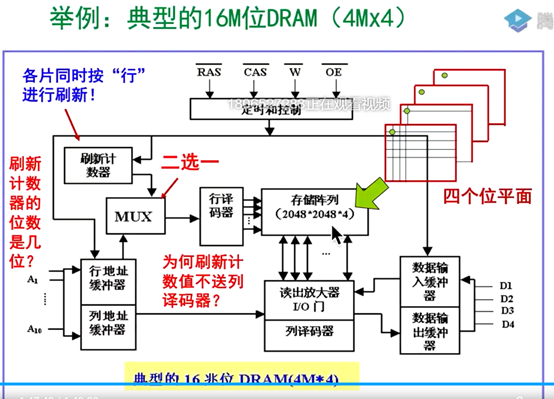

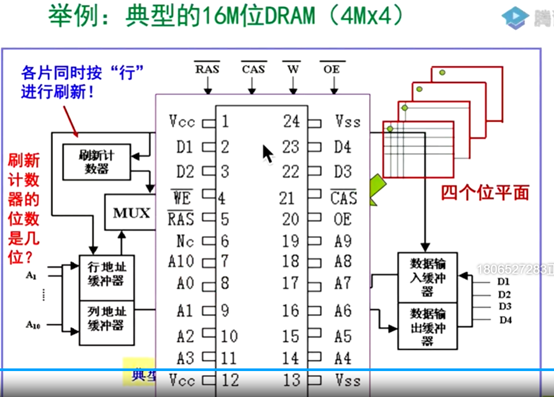

16M是指容量,可以存放这么多的二进制位 4MX4: 前面表示字数/地址数 后面表示这个地址的存储单元的位数 M:兆

存储单元排列成了11行11列,交叉处是由4个cell构成的存储单元

CPU给的地址信号是22位的,在输入到DRAM时不是一次性输入的,为了节省芯片的面积,把地址信号进行了分时复用。22位地址分两批进去,译码器就可以缩小一点,11就可,

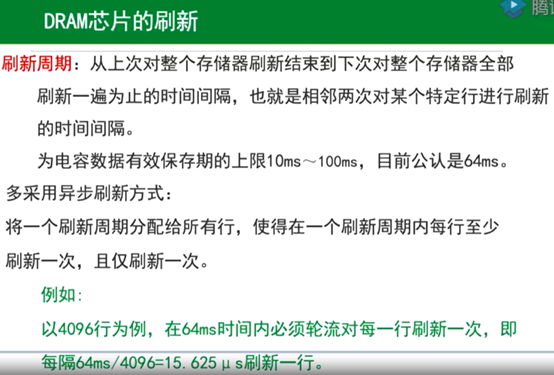

各片同时按“行”进行刷新,刷新(类似读的操作but)的时候没有数据的输出

在一个周期内刷新多少次,取决于它的行数,和它的内部存储阵列有关,2048行,总共刷新2048次,

刷新计数器的位数是11位,

刷新计数器不送列译码器:因为一次刷新一行所以无需送列译码器

芯片,对外就是引脚:

存储系统2

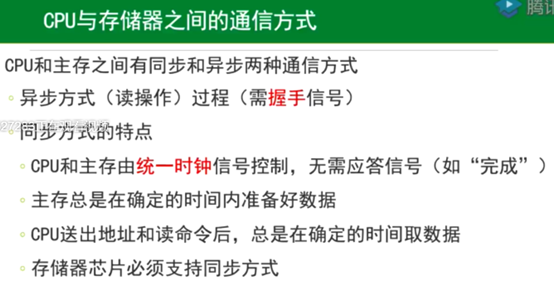

现在用到的主存都是动态的存储器芯片

现在用到的主存都是动态的存储器芯片

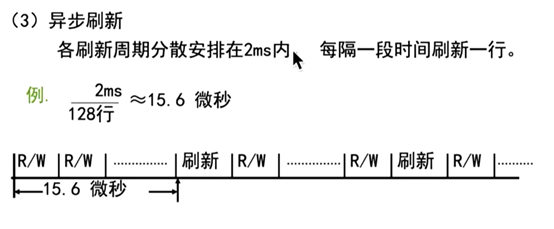

如果同时有刷新和读写请求,先响应:刷新操作的优先级别要比读写操作的级别要高【不及时响应刷新的话信息会丢失】

刷新时按行进行刷新,不需要选中相应的列,只需要行地址,一次刷新一行,

如果要求答案取整,取15,否则时间不够,刷新不完,有的信息会泄露

如果要求答案取整,取15,否则时间不够,刷新不完,有的信息会泄露

\

\

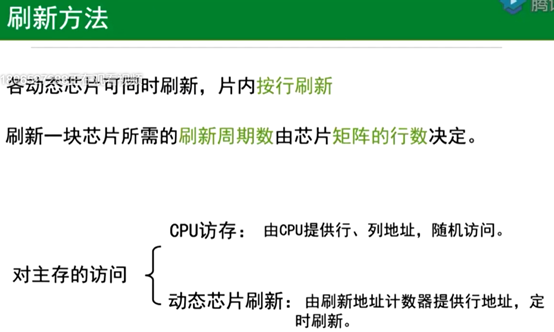

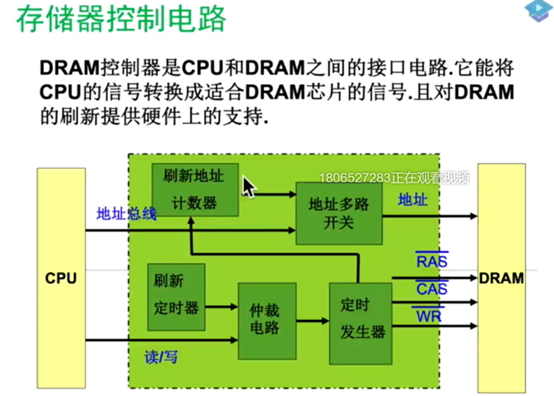

存储器控制器

刷新地址计数器提供行地址, CPU要访问主存的话,要给出主存地址

既有来自CPU的访存请求也有来自内部的刷新请求,由仲裁电路决定相应哪个请求

我们采用异步刷新的方法,刷新时的行地址什么时候提供,隔一段时间提出刷新请求,由定时器定时提供刷新要求

刷新操作对CPU是透明的,中央处理器对主存就是读写,不会发出刷新信号,是在存储器控制电路里面完成的

DRAM的地址有可能来自CPU也有可能是刷新命令的行地址,由RAS[行选中信号]CAS[列选中信号]等来控制。读还是写:WR非[写有效信号]来控制

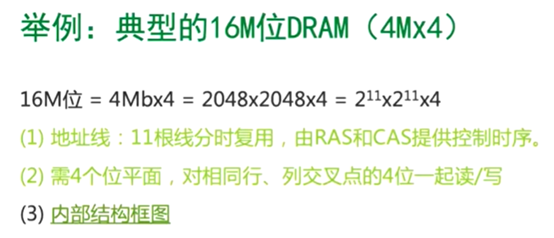

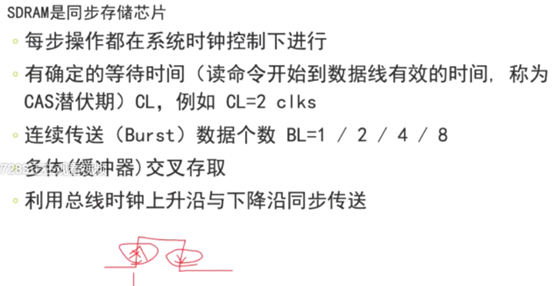

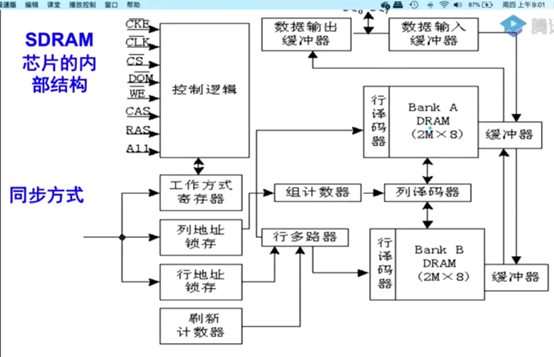

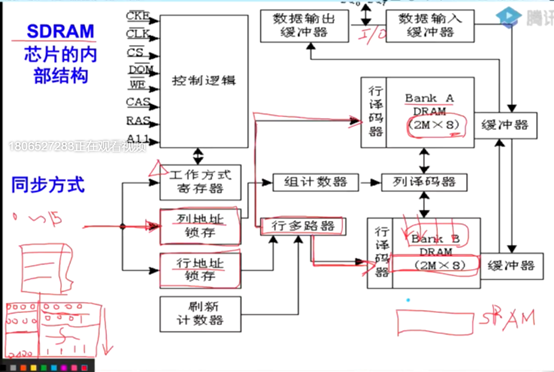

核心器件:记忆单元bankA B【由行多路器可得AB可以同时访问】,存储容量2MX8:字数×字长,存放了2兆数据,每个字是8位

锁存器一般进行数据的保存

工作方式寄存器可以对一次读取的数据长度进行限制【突发式读取 数据块】

突发式读取:高位的行地址不变,低位的列地址变化,就可以得到相应的连续的数据

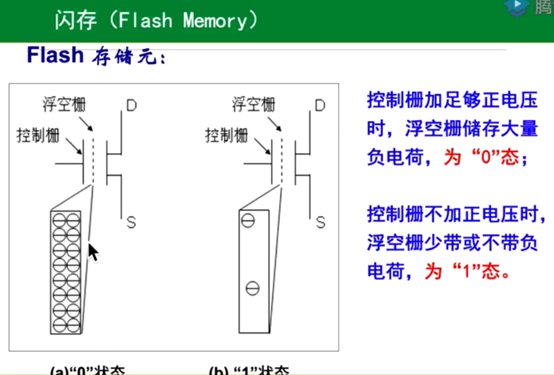

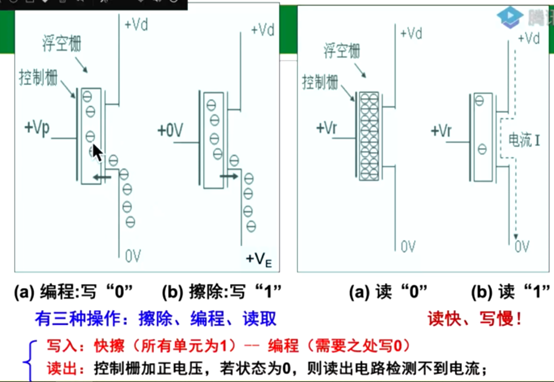

控制栅上加高电压,那里会聚集很多电子,就是零状态,加低电压就是1状态

!!!!!!!!!!!!!!!重点

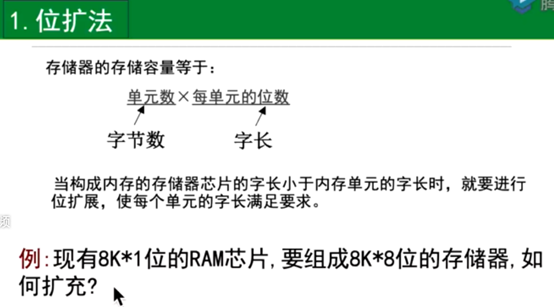

8k×1:有8k个字,每个字长1位;字节数也是芯片的地址空间大小;访问芯片的地址线至少是13位的,跟芯片进行数据交换,数据引脚1位

位扩扩的是后面这个因子:字长

需要8个芯片同时工作,提供8位的数据---在此之前8个芯片的地址信号必须得是相同的,【要选中同一个的相应位置】,这样CPU给一个13位地址,对8个芯片都是有效的【地址线共用】,同时译码,选中同一个位置[当然不同芯片同一位置],通过数据总线[至少8位了]对数据进行交换,

控制线:r/w‘:读写信号:共用,同时读写一个数据一位,和CPU端的访存信号连接

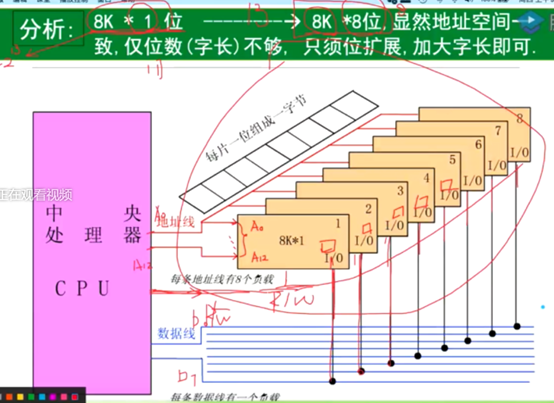

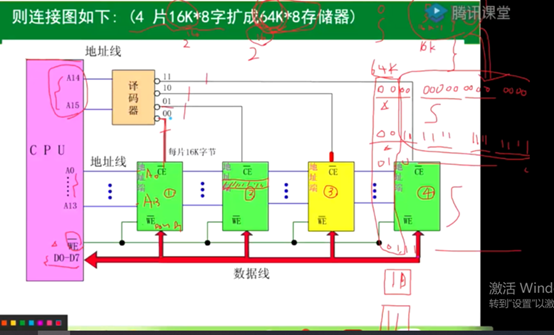

CPU要64k×8的,所以不管内存怎么扩展,他就给16位地址和8位的数据

而每个芯片是16k×8:地址线都是0-15位,数据都是8位

同一时刻只能有一个芯片工作:一号芯片地址0-16k-1【0000 0000 0000 0000-0011 1111 1111 1111】,由此往下推,2号芯片是【0100 0000 0000 0000-0111 1111 1111 1111】,3号10,4号11,第十四位任意变换

当CPU给出16位地址时,根据最高两位迅速判定在哪个芯片,再根据后面的14位决定是哪个位置

片选信号是重点,其他的地址信号数据信号和控制信号都是共用的

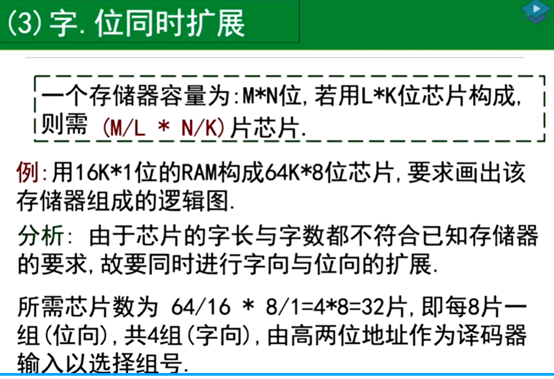

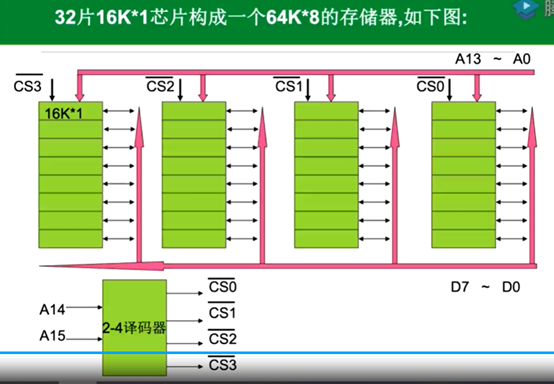

每一组是位扩,组与组之间是字扩【位扩这里 由一位扩展成8位 就是要注意往下叠然后一起输出 之后复制粘贴就可以了 注意总线控制信号啥的】

【字扩就是注意片选信号 当不好画的时候单拎出来也是可以的】

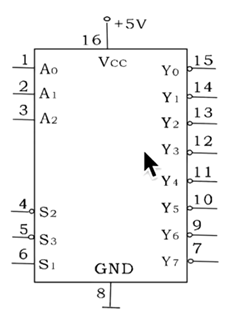

存储器的bank一般译成存储体 隔壁3-8译码器 注意456是控制信号

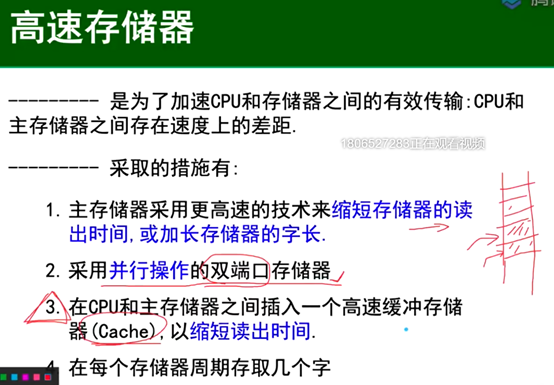

高速存储器

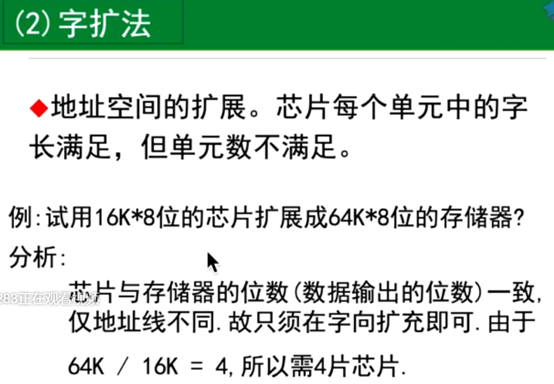

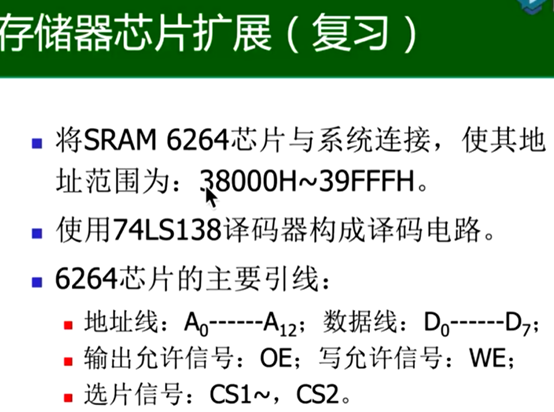

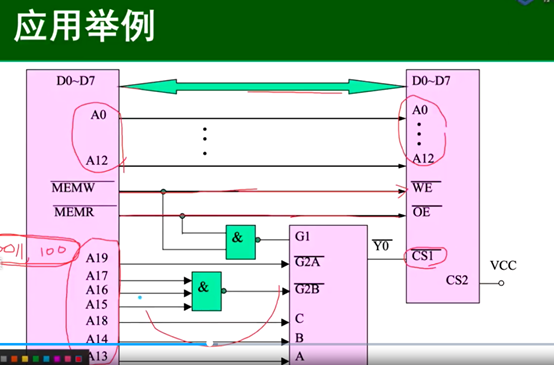

指定地址空间的芯片扩展问题

容量:2^13的地址空间【8k】:8k×8

要求扩展的地址空间多大:39fff-38000+1 !!! =20000H=2^13:8k 【没说所以认为位长还是8】

所需容量大小等于了芯片容量大小,所以只需要1片芯片即可

确定的地址,对地址线的连接有要求

38000h: 0011 1000 0000 0000 0000 20位

39fffh:0011 1001 1111 1111 1111

高七位地址固定为0011 100 剩下的13位地址任意变化

因为无需芯片拓展,所以上面的数据线地址线都是直接横着一条线过去的 ,重点是下面的译码器

要求无论采取何种方式,a19-a13要变成0011 100的样子【转换成最后的片选信号cs1’】,图示采用了译码器+两个与非门 or直接门电路

memw’/memr’:两个访问存储器的控制信号

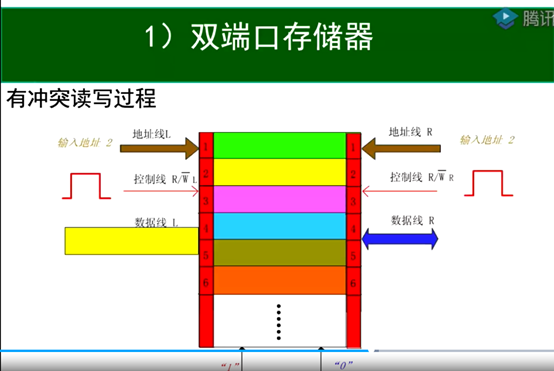

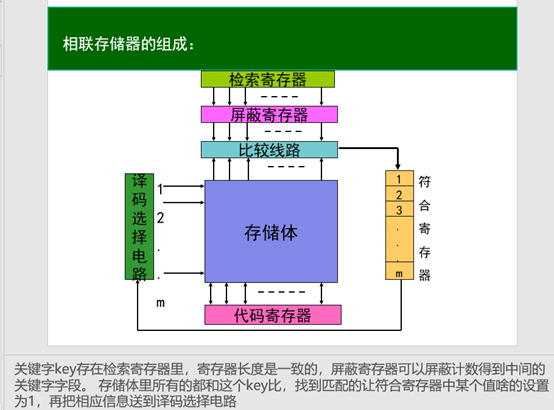

双端口存储器:有两套读写控制电路。并行操作,各自有一个busy信号,如果发生冲突时有仲裁电路进行判定,优先性稍低的电路busy信号置为0,表示该电路现在忙,不操作某冲突区【得等】特点:一个存储器具有两组相互独立的读写控制电路。可进行并行的独立操作

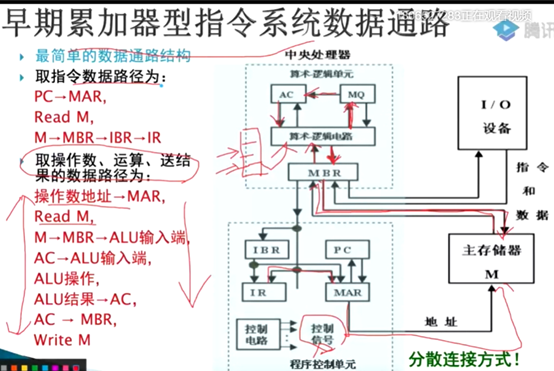

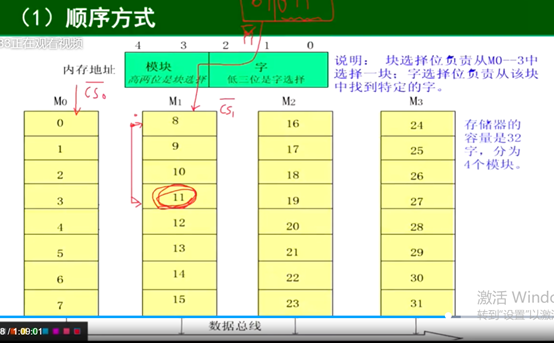

传统的存储器:一个存储周期只能访问一个单元,内部存储单元的地址是连续的,地址都是顺序编号的,称之为顺序编址【给存储单元分配地址称为编址】

多模块存储器:编号不连续,地址交叉

一个二进制的数, /4,余数就是它本身的低两位,所以分成高三位和低两位,eg找11【01011】:010就是2,找到11【4】第四块的第3个对应的11了

以上,这里的012都是地址编号【交叉编址人家存储的时候也是存完1就去2号地址的】【还按地址顺序存,只是地址不挨在一起】

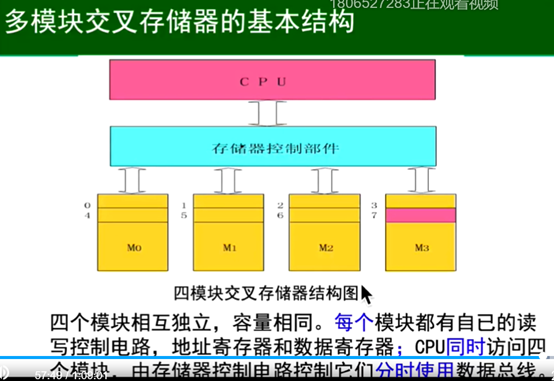

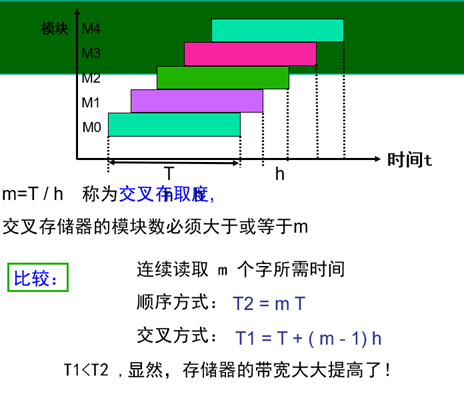

比如你想访问0123这四块连续地址,连续编址选定了1号芯片【也只能选择一个】,那也只能用4个存储周期,而交叉编址则可以一次性选中4个芯片一起读

But数据总线是公共的一次只能一个数占用,所以4个字只能依次传送 【通常一个芯片对应一套读写控制电路】

可以并行读写但是只能以流水方式传送。【分时使用数据总线】

交叉编址 这个当初困扰好久

读写时间是指从启动一次存储操作到完成该操作所需的时间。 读出周期是指CPU向主存发出有效读命令和地址开始,到将所选的数据读出来所用的时间。写入周期就是CPU向主存发出读命令知和有效地址,知道将该数据读出所用的时间。存取周期道又称为读写周期或访内周期。是指主存进行一次完整版的读写操作所用的时间。继连续两次访问存储器间所权经历的最短时间【存储周期】

相关内容

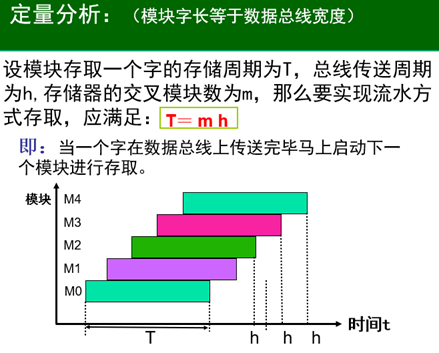

“满负荷工作,同时启动m个模块读取出m个字,在一个存储周期内全部传送完毕“

交叉编址的话,T时间出来了m个字,把这m字依次送出去花了mh时间,当T=MH时,表示一个存储周期的时间运送完了4个字

a) 如何解释实现了满负荷工作?交叉来的话就是2T时间内,读了M字送出去M字

连续编址则是T+H时间内,读了1个送出去1个,T和H有什么联系嘛?

b) 同时启动M个模块,书上讲是“每隔1/M个存储周期启动一个体”:一个意思

c) 这里的总线传送周期是指把数据送出去还是把模块的地址送进来呢?:传送数据

https://blog.csdn.net/nuo_shar/article/details/79048019

以实际数据为例,这样比较容易理解,比如说某个存储体的有2个存储芯片,每个芯片的存储周期为100ns,如果你去读数据,如果你的数据按照这种放置方法,先放第一个芯片,放满后再放第2个芯片(顺序方式)。那么你读数据的过程就是这样:

读0位置数据,等100ns,读1位置数据,等100ns读2位置数据。很容易理解。

但如果你换个方式来放,比如说我0位置是1号芯片起始,1位置是2号芯片起始位置,2位置是1号芯片第2个单元,3位置是2号芯片的第2个单元这样交叉来编址。再回忆存储周期的概念:其实从芯片中把数据读到缓冲区,再从缓冲区读到CPU,这个读的过程非常短,仅仅是个脉冲就可以解决的问题,但由于芯片的物理属性,你读一个芯片后,必须间隔一段时间才能去读。采用交叉编址后,你的读过程就像这样:

读0位置数据到缓冲区,40ns后,CPU取走了数据。这时1号芯片的100ns的周期还没过,不能去读,但幸运的是我们读的不是1号芯片,而是2号芯片,这样,我们就把2号芯片的数据读到缓冲区。过了40ns后,CPU取走数据,此时过去了80ns,我们只需再等20ns就可以继续去读3号位置数据,这样速度就比以前快了很多。

1、一个4体并行低位交叉存储器,每个模块的容量是64K×32位,存取周期为200ns,在以下说法中,( )是正确的。

A. 在200ns内,存储器能向CPU提供256位二进制信息

B. 在200ns内,存储器能向CPU提供128位二进制信息

C. 在50ns内,每个模块能向CPU提供32位二进制信息

D. 都不对

解:对CPU来说,它可以在一个存取周期内连续访问4个模块,32位×4=128位。本题答案为B。

3、采用4体并行低位交叉存储器,每个模块的容量是32K×16位,存取周期为400ns,在以下说法中, 是正确的。

A. 在0.1µs内,存储器能向CPU提供26位二进制信息

B. 在0.1µs内,存储器能向CPU提供16位二进制信息

C. 在0.4µs内,存储器能向CPU提供26位二进制信息

D. 都不对

解:400ns=0.4µs,16位×4=64位=26位。本题答案为C。

5. 一个四体并行的低位交叉编址存储器,每个存储体的存取周期为200ns,总线传输周期为50ns,则连续读取10个存储字需时( )。

A.2000ns

B.600ns

C.650ns

D.300ns

正确答案

C

答案解析

四体并行的低位交叉存储器连续读取10个存储字时,读第一个存储字需要一个完整的存取周期,即200ns,接下来每个存储字的读取只需一个总线传输周期50ns,故共需时200+50×(10-1)=650ns。【满负荷工作】

总线传输周期 是指它过了多少秒就来读数“40ns后,CPU取走了数据”

例题

例题

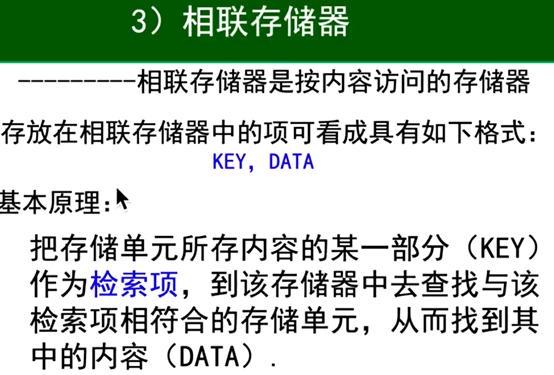

前面的存储器都是按地址存取,这个是按内容

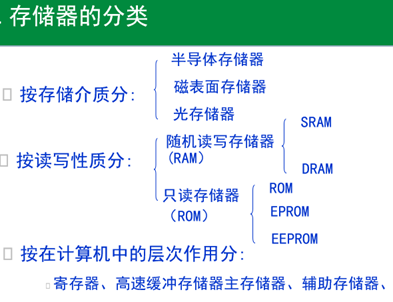

SRAM:静态存储器 DRAM:动态存储器

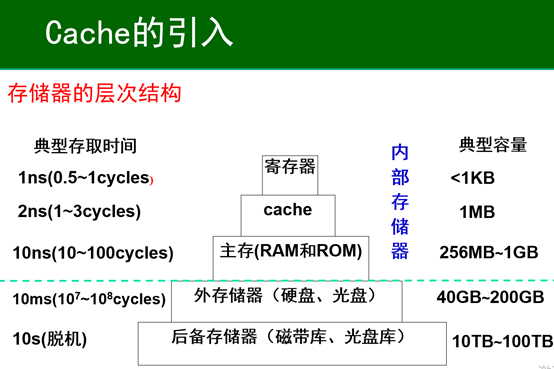

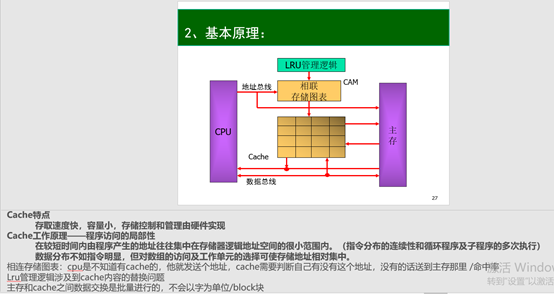

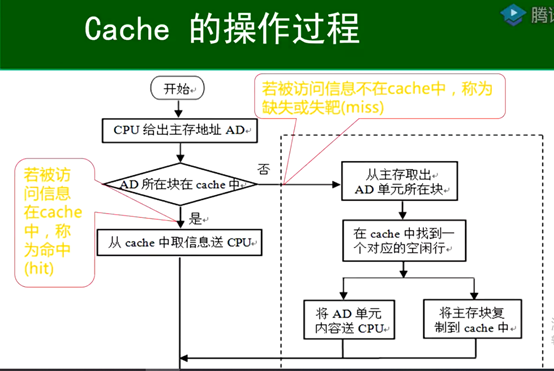

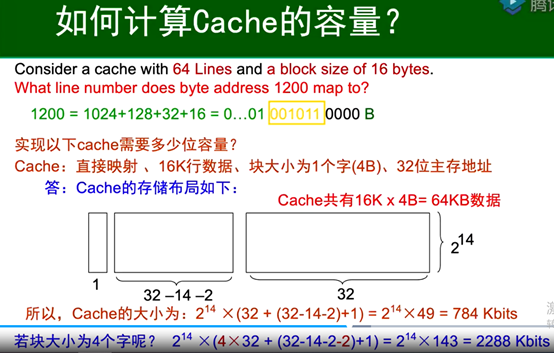

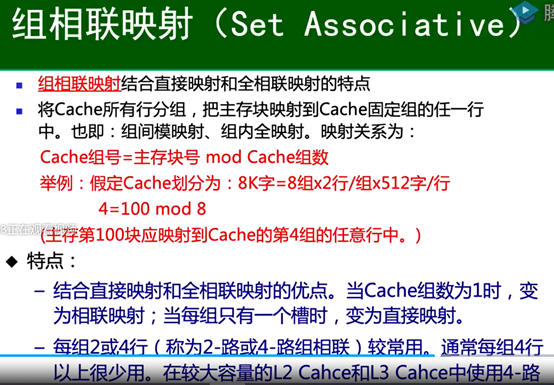

Cache

程序访问的局部性原理

程序访问的局部性原理

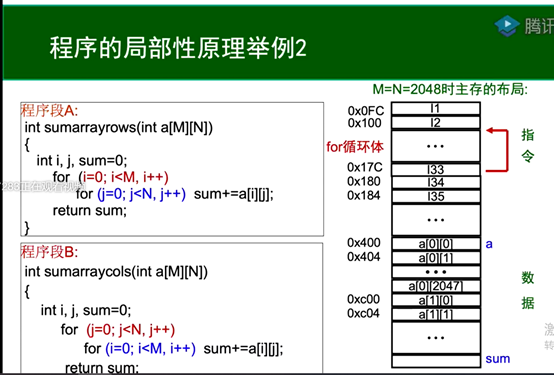

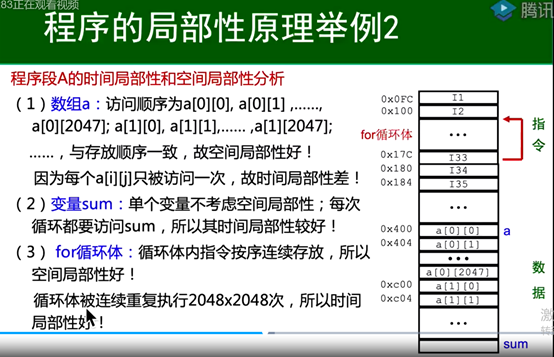

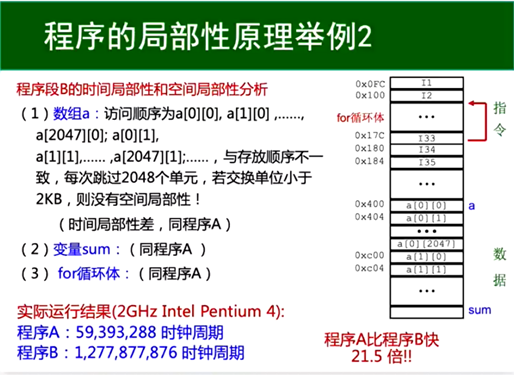

双重循环,小心当前的硬件平台采取的存储方式是以行优先还是列优先 C语言的话按行优先 程序B的话则是按列优先存放

地址不连续导致数据的空间局部性差 【两个程序的指令的时间空间局部性是一样的:时间局部性和空间局部性较好 sum:单个数据不考虑空间局部性】

数组的时间局部性不怎么样

数组的时间局部性不怎么样

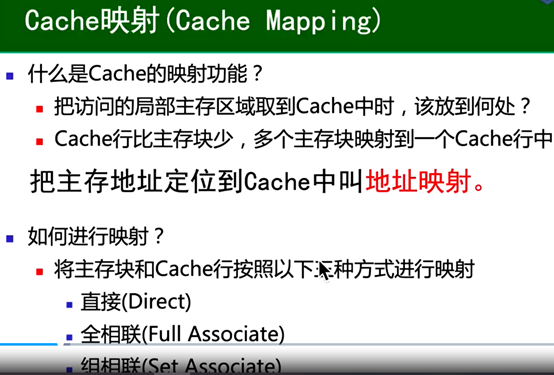

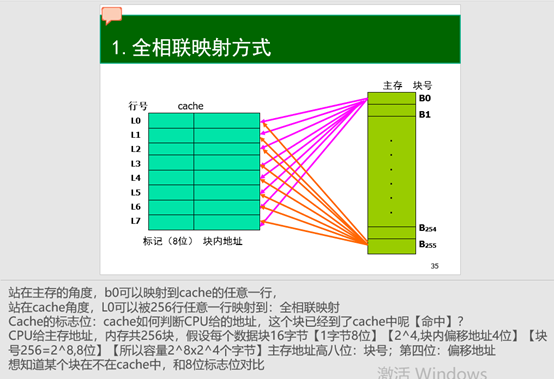

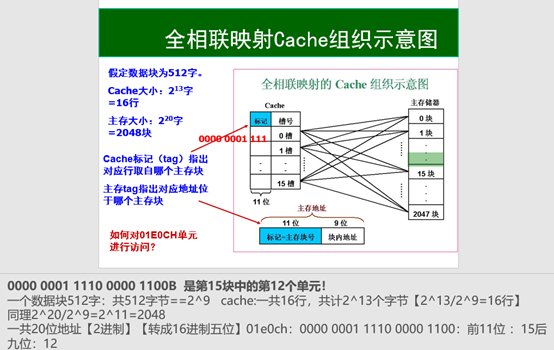

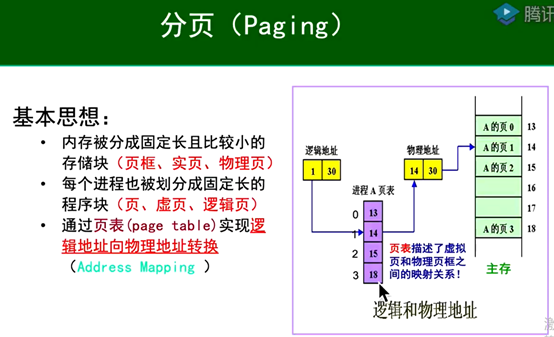

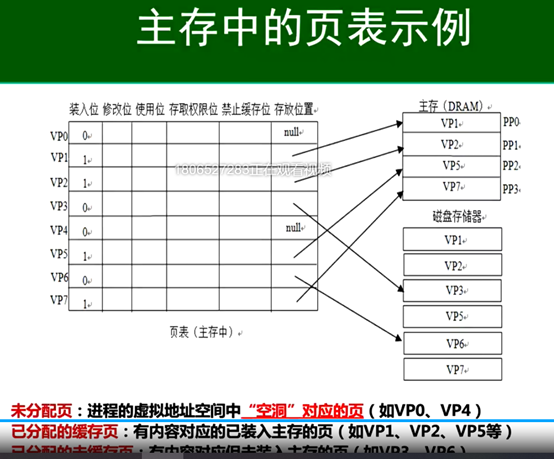

指令最开始给的是虚拟地址,转换成主存地址 主存被分成若干大小相同的块,称为主存块(Block)

Cache也被分成相同大小的块,称为Cache行(line)或槽(Slot)。

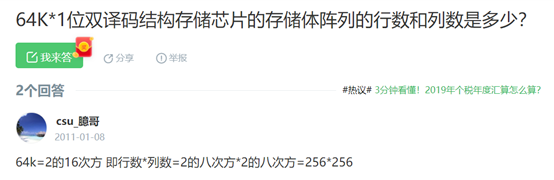

5.刷新问题—判断行

还是“因为64K×1的存储矩阵是由四个128×128的矩阵构成。所以128行” ?

在已知芯片的容量情况下,该如何判断行列数呢?是根据自己的积累还是利用2的幂进行计算呢(则行数==列数?)?后者题目要么会直接给,要么就自己假设

如果给的数2^x 这个x不是偶数,无法拆成两对的话,就行地址长一点(行列差1。。)

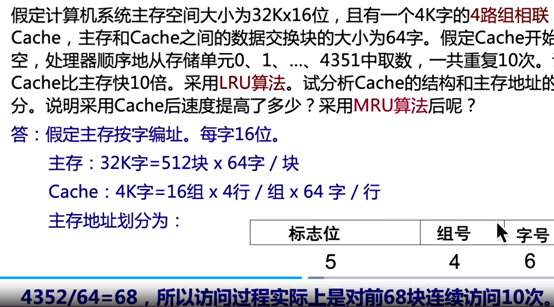

0-4351在内存哪些块内:4352/65=68一共68块 这个题作业本上有详细解答

【不考虑单位换算嘛,一存储单元存放一个字节,64字=128字节,一块存放128,应该4352/128?】

数据长度和地址混在一起了 不存在单位换算

:这里一个字16位,32kx16:这个芯片有32k个字,每个字16位

块则是64字,每个字也是16位呀【cache是copy 块是从内存拿到cache的 】

所以一个存储单位就放一个字 【存储单位长度就是存放的数据长度】

具体不要求:

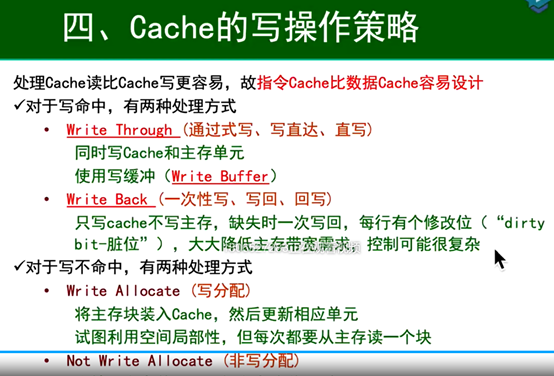

Write Back:先只写cache 当cache内容缺似时,统一写回到主存

Write Back:先只写cache 当cache内容缺似时,统一写回到主存

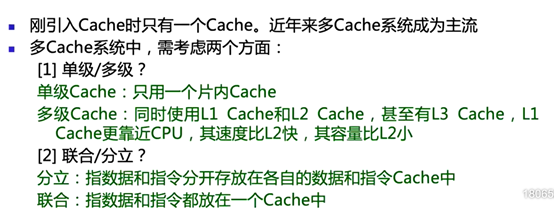

L1cache/片内cache:是在cpu内 分立 命中时间比命中率更重要

片外/L2:在CPU外 联合

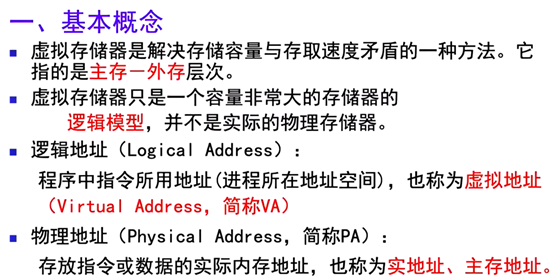

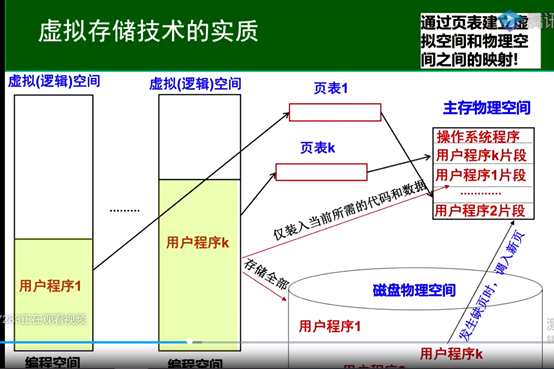

虚拟存储器

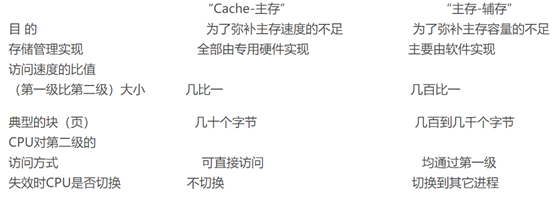

“Cache-主存”和“主存和辅存”的区别

“cache-主存”指 在 CPU 和主存之间增加一级速度快、但容量较小且每位价格较高的高速缓冲存储Cache)。借助于辅助软硬件,它与主存构成一个有机的整体,以弥补主存速度的不足。这个层次的工作主要由硬件实现。

主存-辅存”层次的目的是为了弥补主存容量的不足。它是在主存外面增加一个容量更大、每位价格更低、但速度更慢的存储器(称为辅存,一般是硬盘)。它们依靠辅助软硬件的作用,构成一个整体。“主存-辅存”层次常被用来实现虚拟存储器,向编程人员提供大量的程序空间。

区分内存、外存、主存、辅存等

对一般计算机而言,主存=内存 指计算机中的内存条;外存=辅存 如:硬盘、U盘、光盘及软盘等。

主存储器又称内存储器(简称内存)。

内存又称主存,是CPU能直接寻址的存储空间,它的特点是存取速率快。内存是电脑中主要部件,它是相对于外存来说。

内存一般采用半导体存储单元,包括随机存储器(RAM)、只读存储器(ROM)和高级缓存(Cache)。

随机存储器(RAM):(Random Access Memory)我们不仅可以从中读取数据,而且还可以写入数据。但是机器电源关闭时,它中数据就会丢失。内存条(SIMM)就是把RAM集成块集中在一小块电路板上。

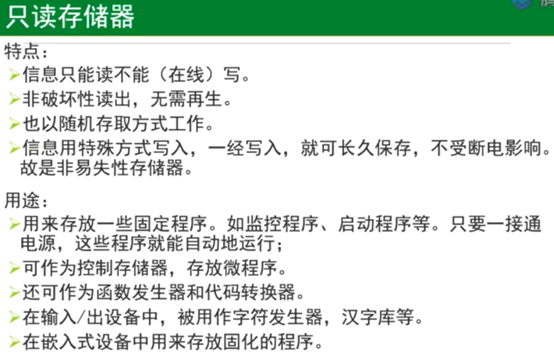

只读存储器(ROM):(Read Only Memory)它是把数据或程序永久保存在其中,不能更改,只能读取。即使机器断电,数据也不会丢失。

高级缓存(Cache):它是介于CPU与内存之间,常用有一级缓存(L1)、二级缓存(L2)、三级缓存(L3)(一般存在于Intel系列)。它的读写速度比 内存还快,当CPU在内存中读取或写入数据时,数据会被保存在高级缓冲存储器中,当下次访问该数据时,CPU直接读取高级缓冲存储器,而不是更慢的内存。

辅助存储器又称外存储器(简称外存)。它是指除CPU缓存和计算机内存以外的存储器。

磁盘和内存:

程序运行时,内存和磁盘的作用及相互关系。

计算机在运行程序时,必须将磁盘中的内容加载到内存中,不加载是不能运行程序的。

在内存中有一部分数据存的是磁盘的缓存,这样做可以加速磁盘访问速度。就跟我们开发程序中使用的缓存作用一样。

虚拟内存:

虚拟内存,是指把磁盘中的一部分作为假想的内存使用,windows通过分页式虚拟内存机制:即在不考虑程序构造的情况下将程序按照一定大小的页进行划分,并以页为单位在内存和磁盘间进行置换。一般来说自己计算机的实际内存大小即为当前页文件的大小。这个是可以在电脑中进行设定的。

物理内存是 相对于虚拟内存而言的。物理内存指通过物理内存条而获得的内存空间,而虚拟内存则是指将硬盘的一块区域划分来作为内存。

虚拟内存与物理内存的联系与区别

操作系统有虚拟内存与物理内存的概念

地址空间

地址空间包括物理空间以及虚拟空间。 https://baike.baidu.com/item/%E5%9C%B0%E5%9D%80%E7%A9%BA%E9%97%B4

虚拟地址是Windows程序时运行在386保护模式下,这样程序访问存储器所使用的逻辑地址称为虚拟地址

与物理地址相对

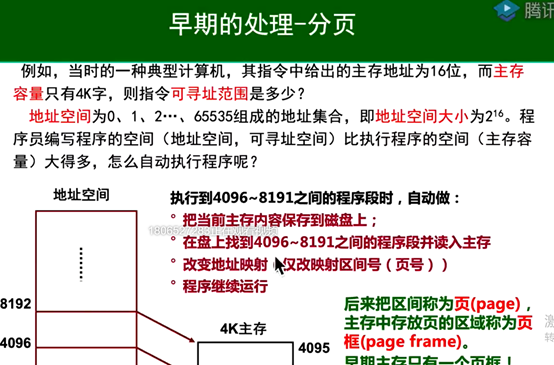

指令大小是4个4k 执行一个4k进到内存 再出来换下一个进去

指令大小是4个4k 执行一个4k进到内存 再出来换下一个进去

我们写好的程序麻的一开始都是存放在硬磁盘上,双击exe执行时,硬磁盘和操作系统把代码和数据装入主存的物理地址空间

即虚拟空间分为若干个页面,物理空间分成若干个页框,往里调

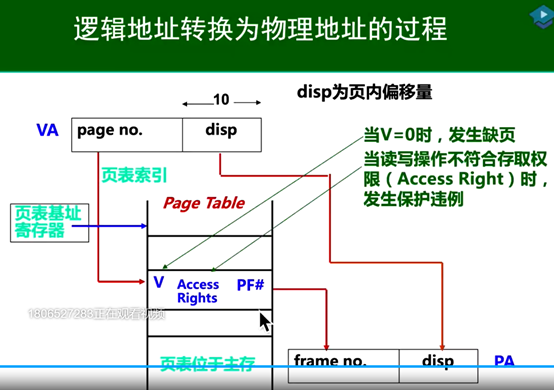

Disp:偏移地址空间 直接拿过来拼接即可

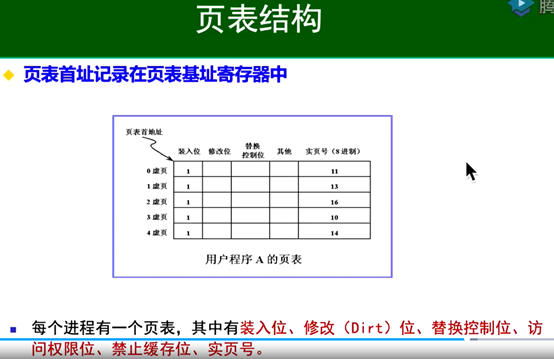

Va:虚拟地址 pageno:去页表通过页面号查对应的记录 找到PF:实页号【物理地址的实页号】

浙公网安备 33010602011771号

浙公网安备 33010602011771号