【FPGA学习】根据datasheet编写Verilog驱动(PCF8574 IO扩展板练习)

在之间的博客中已经讲了如何阅读一本datasheet并编写Verilog驱动代码,而在这篇博客中就加以应用,为PCF8574 IO扩展板编写驱动并观察效果,至于为什么选择这个,一方面是因为这个芯片功能简单,可以作为初次实践的练习对象;另一方面是如果你使用过正点原子的阿波罗开发板的话,你就会看到上面的很多信号都连在这个扩展芯片上面的,因此编写驱动也对使用STM32有好处

有了上一篇的基础,我们就对datasheet和板子的分析做个简短些,重点在于驱动代码的编写和效果的验证

参考:

FPGA零基础学习:IIC协议驱动设计

I2C - 集成电路之间的同步、半双工数据传输

I2C Master

在编写代码前的分析

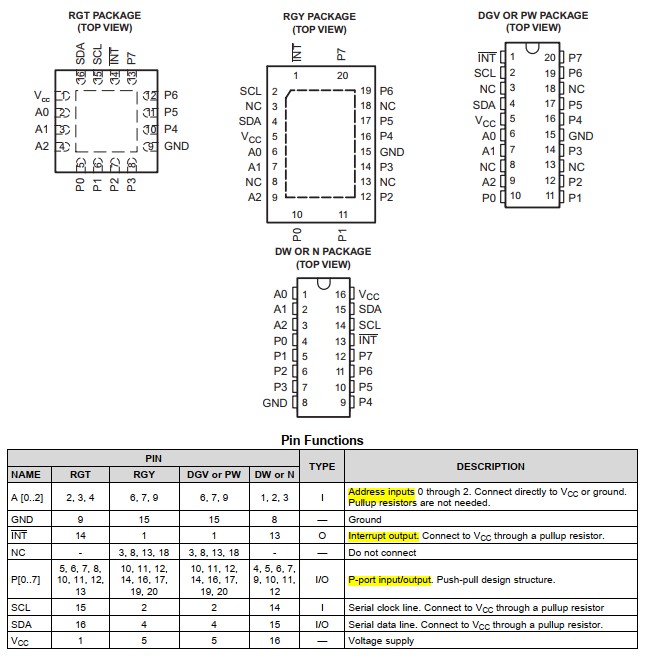

先看看芯片的引脚:

可以看到芯片有多种封装形式,不过功能都是一样的

- A[2:0]:地址输入

- INT:中断输出,当在输入模式下输入引脚有上升沿或下降沿时中断发生

- P[7:0]:P端口输入输出

- SCL,SDA:IIC时钟线和数据线

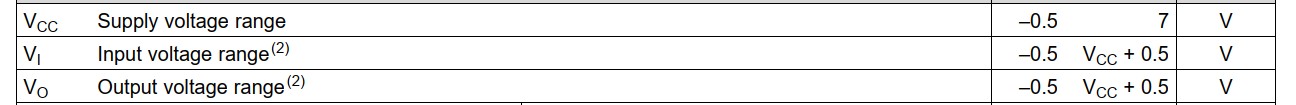

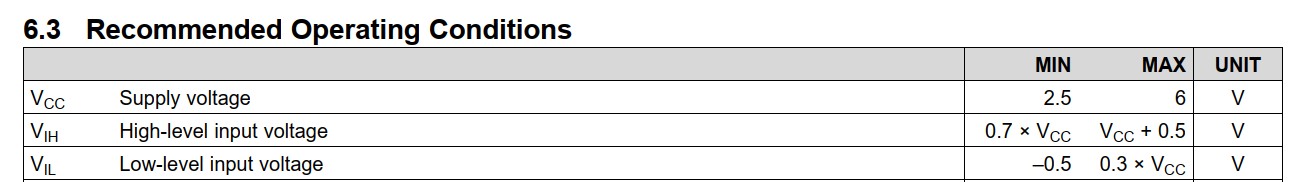

其次看一下一些参数,在使用中要注意一下:

一些供电参数,接Vcc的时候要注意一下

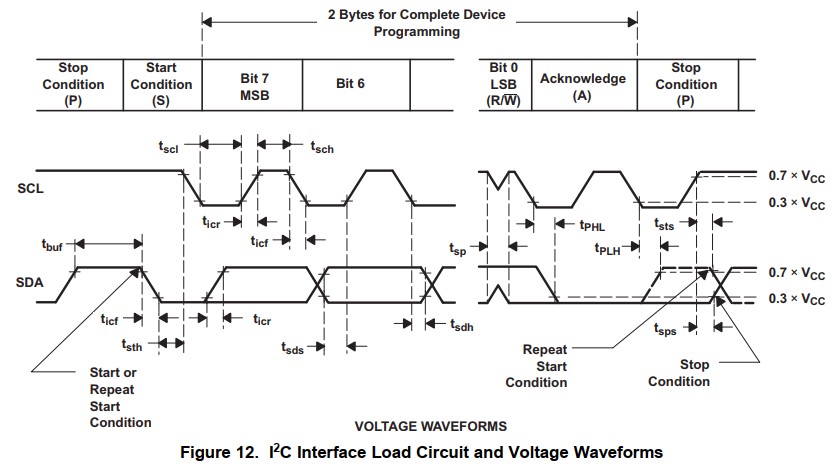

然后看一下时序图,编写驱动就是要参考这个:

最后看一下芯片的功能实现:

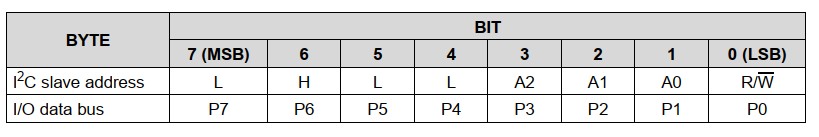

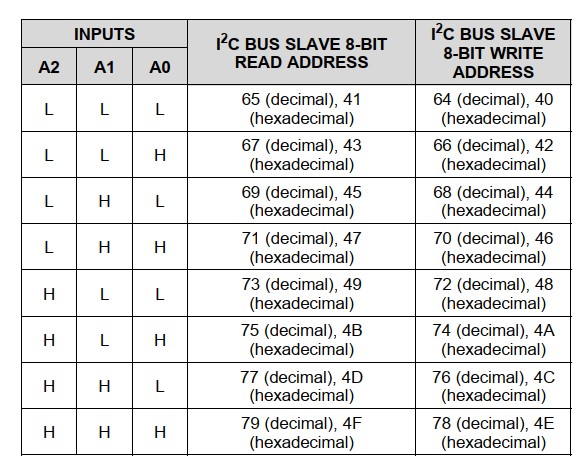

可以看到IIC的地址是由A[2:0]决定的,我们所采用的模块中是通过跳线帽来决定A[2:0]的高低电平的:

编写Verilog驱动

Verilog驱动代码编写如下:

程序的状态转移图如下:

逻辑分析仪的使用

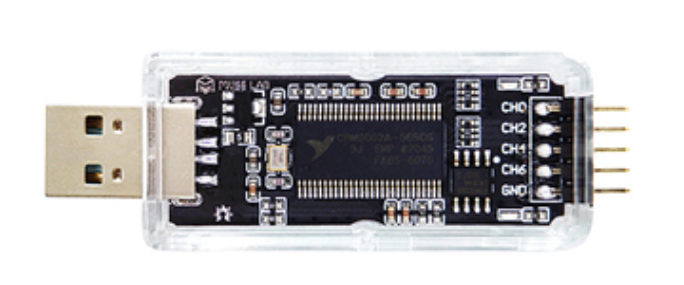

逻辑分析仪可以用来分析时序,这里就介绍一下我使用的逻辑分析仪,并对上文中的编写的代码进行时序分析

我使用的逻辑分析仪是NanoDLA逻辑分析仪,比较便宜的同时可以分析一些基本时序,适用于初学者:

- 最高24MHz采样率

- 8通道可同时采样

- 支持输入电压[-0.5v,5.25v],其中低电平为[-0.5v,0.8v],高电平为[2v,5.25v]

本文作者:Destiny_zxx

本文链接:https://www.cnblogs.com/yuhengz/p/15997458.html

版权声明:本作品采用知识共享署名-非商业性使用-禁止演绎 2.5 中国大陆许可协议进行许可。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 阿里最新开源QwQ-32B,效果媲美deepseek-r1满血版,部署成本又又又降低了!

· 开源Multi-agent AI智能体框架aevatar.ai,欢迎大家贡献代码

· Manus重磅发布:全球首款通用AI代理技术深度解析与实战指南

· 被坑几百块钱后,我竟然真的恢复了删除的微信聊天记录!

· AI技术革命,工作效率10个最佳AI工具