FPGA采集系统

采用FPGA技术,将CMOS摄像头(LVDS接口)的视频数据经过采集、存储、帧率转换及格式转换,最终通过USB2.0接口显示在电脑屏幕上。

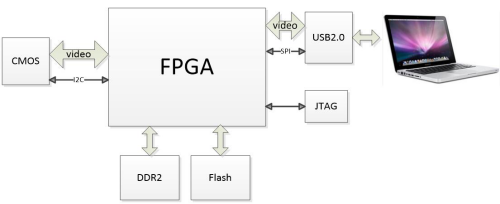

硬件系统框图:

CMOS采用一款全局曝光芯片,FPGA采用ALTERA公司的CYCLONE IV,FLASH采用EPCS64,DDR2采用Hynix公司的1Gb内存条,USB2.0采用Cypress公司的68013芯片。

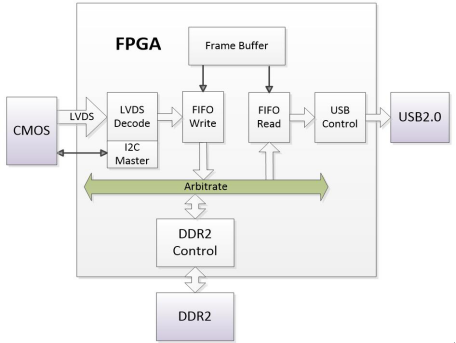

FPGA各部分逻辑模块如下图所示:

LVDS Decode,解码CMOS摄像头视频数据;

I2C Master,配置CMOS芯片;

DDR2 Control,配置与控制DDR2芯片组,实现读写仲裁;

FIFO Write,将采集到的视频数据跨时钟域地写进DDR2中;

FIFO Read,将DDR2中的数据跨时钟域地读出给后续图像处理模块;

Frame Buffer,负责FIFO Write和FIFO Read的调度,实现帧率转换;

USB Control,接受USB PHY的请求,通过FIFO Read向DDR2索取数据,并自定义打包发送给USB PHY芯片。

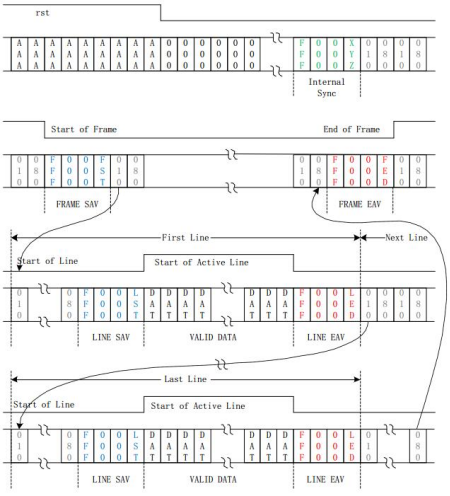

LVDS解码

摄像头芯片提供差分串行接口(LVDS),支持1/2/4个Data lane来传输图像8/10/12 bit数据。这里以4个data lane,同步信号内嵌的模式为例,介绍其传输时序。

FPGA如何实现算法:

用FPGA实现算法,简单理解就像用C语言实现算法一样。不过FPGA用硬件描述语言,如verilog等。可以根据算法先用C实现,然后再用verilog实现。C和verilog有种一一对应的关系。综合之后有需要可以进行布局,约束和优化等。因为FPGA可以并行执行,所以实现算法要比CPU类型的器件(如DSP、MCU等)有优势。

FPGA设计流程(FPGA板子的开发):

FPGA设计流程是利用EDA开发软件和编程工具对FPGA芯片进行开发的过程。FPGA的设计流程如上图所示:包括设计定义、代码实现、功能仿真、逻辑综合、前仿真、布局布线、后仿真和板级调试等步骤!

1.设计定义

设计定义阶段主要进行方案验证、系统设计和FPGA芯片选型等准备工作。根据任务要求,评估系统的指标和复杂度,对工作速度和芯片本身的资源、成本等方面进行权衡,选择合理的设计方案和合适的器件类型。

这个阶段往往会花费大量的时间,这个阶段之后一般已经完成了系统建模,功能划分,模块划分以及设计文档的撰写等工作。

2.代码实现

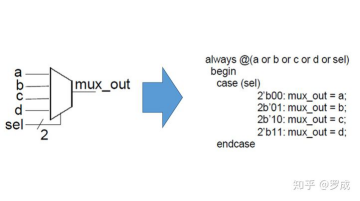

代码实现阶段是将划分好的各功能模块用硬件描述语言表达出来,常用的硬件描述语言有Verilog HDL和VHDL。下面是一个四选一电路的代码实现过程:

四选一电路的代码实现过程

常用的代码编辑器软件有notepad++和UltralEdit等,它们支持几乎所有主流编程语言的高亮显示、代码补全、自定义快捷键等功能,外观漂亮、功能强大,扩展性强,具有丰富的插件包,极大的提高工作效率。

3.功能仿真

功能仿真是在编译之前对用户所设计的电路进行逻辑功能验证,此时的仿真没有延迟信息,仅对初步的功能进行检测。

4.逻辑综合

逻辑综合的概念是:将高级抽象层次的语言描述转化成较低层次的电路结构。也就是说将硬件描述语言描述的电路逻辑转化成与门、或门、非门、触发器等基本逻辑单元的互连关系,也就是我们常说的门级网表。

综合的概念很重要,利用Verilog做电路设计时我们总是强调可综合的概念,可综合就是我们的这段代码可以被翻译成门级电路,不可综合就是代码不能被翻译成与之对应的门级电路。

综合是创造性的转化过程,它不但能翻译我们的电路,还能够优化我们的电路,比如去除电路描述中冗余的电路结构,或者复用功能相同的电路结构。

5.前仿真

前仿真也叫做综合后仿真,仿真时,把综合生成的标准延时文件反标注到综合仿真模型中去。

因为综合后只能体现基本的逻辑门之间的互连关系,并不是实物电路,没有连线长度信息,所以前仿真只能评估门延时带来的影响,不能估计路径延时,前仿真结果和布线后实际情况还有一定的差距,并不十分准确。

目前的综合工具较为成熟,一般的设计可以省略这一步。但如果布局布线后发现电路功能与设计意图不符,就需要回溯到前仿真来确定问题所在。

6.布局布线

综合后生成的门级网表只是表示了门与门之间虚拟的连接关系,并没有规定每个门的位置以及连线长度等。布局布线就是一个将门级网表中的门的位置以及连线信息确定下来的过程。

综合后生成的门级网表只是虚拟的连接关系,并没有反应到实物上去。布局布线有时也叫作实现与布局布线,布局布线将逻辑网表中的门级连接关系配置到FPGA芯片内部的固有硬件结构上。布局布线过程将每一个门实际配置到固定位置的可编程逻辑块(CLB)中。

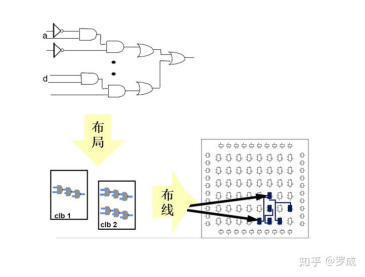

布局布线过程

在解释布局布线之前,我们先回顾一下FPGA的结构,我们知道FPGA可重复编程的基础是拥有巨量的可配置逻辑块(CLB)、丰富的布线资源以及其他资源

①布局

布局的过程就是将门级网表中的每一个门“安置”到CLB中的过程,这个过程是一个映射的过程。

②布线

布线是利用FPGA中丰富的布线资源将CLB根据逻辑关系连接在一起的过程。

逻辑门的映射位置不是随意的,是FPGA设计软件经过算法计算后精心排列的一般的布局布线策略是占用最少的CLB并且连线尽量短,也就是面积和速度最优。

布局布线策略有两种:速度优先和面积优先,往往不能同时达到两者皆最优,所以布局布线时需要在速度最优和面积最优之间做出选择。

一般的布局布线策略是占用最少的CLB并且连线尽量短,也就是面积和速度最优。

布局布线策略有两种:速度优先和面积优先,往往不能同时达到两者皆最优,所以布局布线时需要在速度最优和面积最优之间做出选择。

布局布线后就可以进行静态时序分析了,静态时序分析的方法是在布局布线后的实际电路中寻找寄存器和寄存器之间的最长路径延迟,通过最大延迟可以得出系统最大时钟速率。静态时序分析也是EDA工具自动完成,延迟路径信息可以在生成的时序报告中分析。时序分析的概念以后的教程中也会细讲。

7.后仿真

后仿真也称为时序仿真,是将布局布线的延时信息反标注到设计网表中来检测有无时序违规。经过布局布线后,门与门之间的连线长度也确定了,所以后仿真包含的延迟信息最全,也最精确,能更好的反映芯片的额实际工作情况。

功能仿真:无延迟信息;

前仿真:只有门级的延迟;

后仿真:门级延迟和连线延迟;

8.板级调试

我们的FPGA设计不能只在电脑上跑仿真,最终还是要在电路板上应用起来的,设计的最后一步就是板级测试了,将EDA软件产生的数据文件(位数据流文件)下载到FPGA芯片中,进行实际的测试。FPGA工程师还需要有一定的硬件知识,能够看懂电路板原理图设计和PCB是最低要求了,能够独立设计原理图是最好的了。

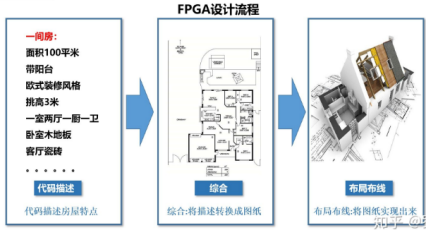

就比如盖房子的过程:

代码实现:比如我要盖一座房子,我把房子的特点描述出来:比如面积100平米、带阳台、欧式装修风格、挑高3米、一室两厅一厨一卫、卧室木地板客厅瓷砖等等要求,这个描述房屋特点的过程就好比我们用Verilog描述电路功能的过程。

逻辑综合:建筑师根据我们的要求画出施工图纸,施工图纸将我的需求数字化、具体化,比如这个墙有多高,门有多宽,窗户面积等等,这个过程就好比综合的过程,将房屋需求翻译成具体的数字化图纸,只不过综合是将电路功能翻译成门级网表,建筑师干的活就是综合工具软件干的活。

布局布线:工人拿会根据图纸(综合后网表),用砖、水泥、钢筋、木材等材料建造施工的过程就好比布局布线的过程。图纸规定了一面墙,但是没有规定具体用哪一块砖来砌墙,工人可以自主决定用哪些砖。布局布线是根据综合后的网表(施工图纸),利用FPGA芯片内部的可编程逻辑块(CLB),布线资源,时钟资源,存储资源等搭建电路的过程。