SGDMA与普通DMA

DMA(Direct memory access,内存直接存取),属于 Vectored I/O 方式,也是下沉运算的一种实现。

区别

Scatter-gather DMA 与 Block DMA(即普通DMA) 方式不同,

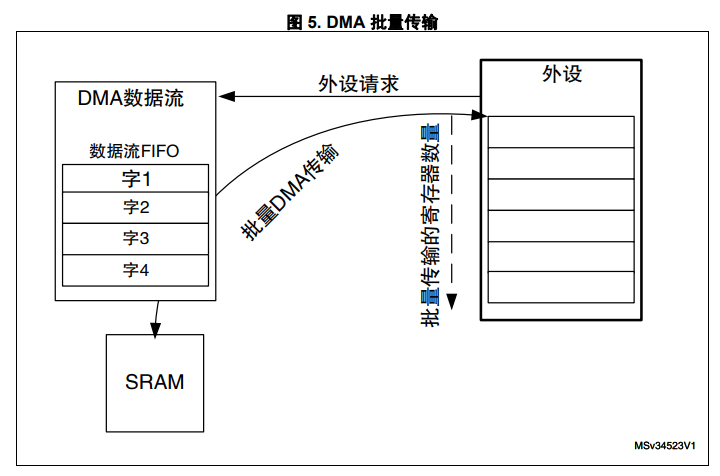

Block DMA: 一次只传输一块物理上连续的数据,完成后中断,主机收到中断后再行下一块物理上连续的数据传输。

Scatter-gather DMA: 使用一个链表描述物理上不连续的存储空间,然后把链表首地址告诉DMA master。DMA master在传输完一块物理连续的数据后,会直接根据链表继续传输下一块物理上连续的数据,直到传输完毕后才发起中断。

很显然,scatter-gather DMA方式比block DMA方式效率高,但需要硬件软件都实现。

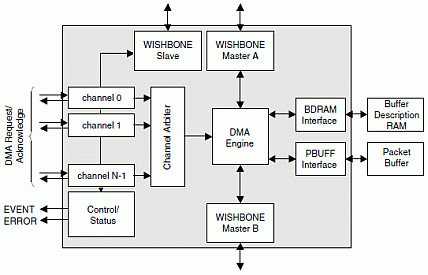

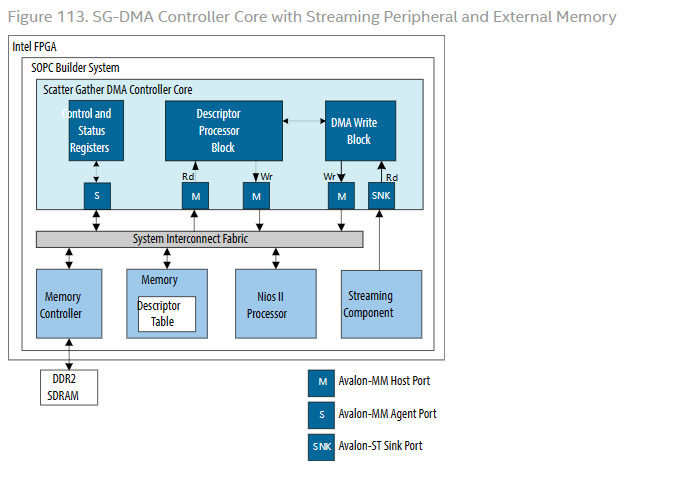

下图是某IP厂商的SG-DMA IP

Linux应用层 Vectored_I/O 写法(需驱动实现)

应用层的写法,代码来自Vectored_I/O-wikipedia:

#include <stdio.h>

#include <stdlib.h>

#include <string.h>

#include <unistd.h>

#include <sys/uio.h>

int main(int argc, char *argv[])

{

const char buf1[] = "Hello, ";

const char buf2[] = "Wikipedia ";

const char buf3[] = "Community!\n";

struct iovec bufs[] = {

{ .iov_base = (void *)buf1, .iov_len = strlen(buf1) },

{ .iov_base = (void *)buf2, .iov_len = strlen(buf2) },

{ .iov_base = (void *)buf3, .iov_len = strlen(buf3) },

};

if (writev(STDOUT_FILENO, bufs, sizeof(bufs) / sizeof(bufs[0])) == -1)

{

perror("writev()");

exit(EXIT_FAILURE);

}

return EXIT_SUCCESS;

}

STM32 的 DMA控制器(Block DMA)

支持 内存到内存,外设到内存,内存到外设 四种。

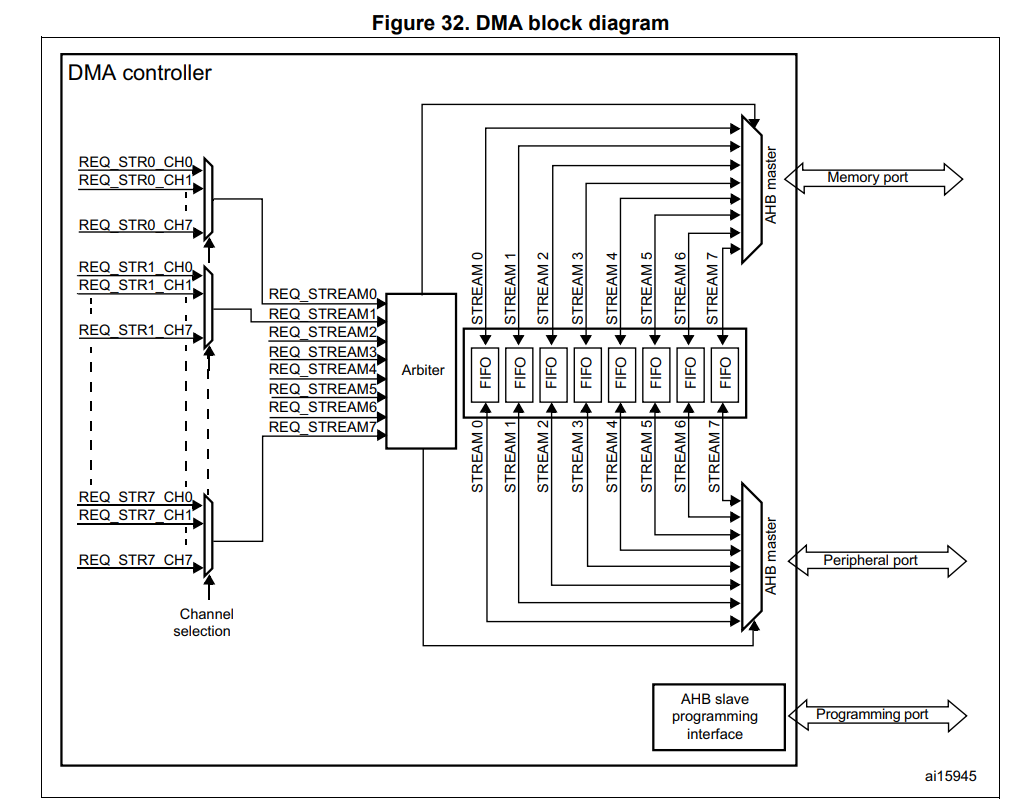

框图

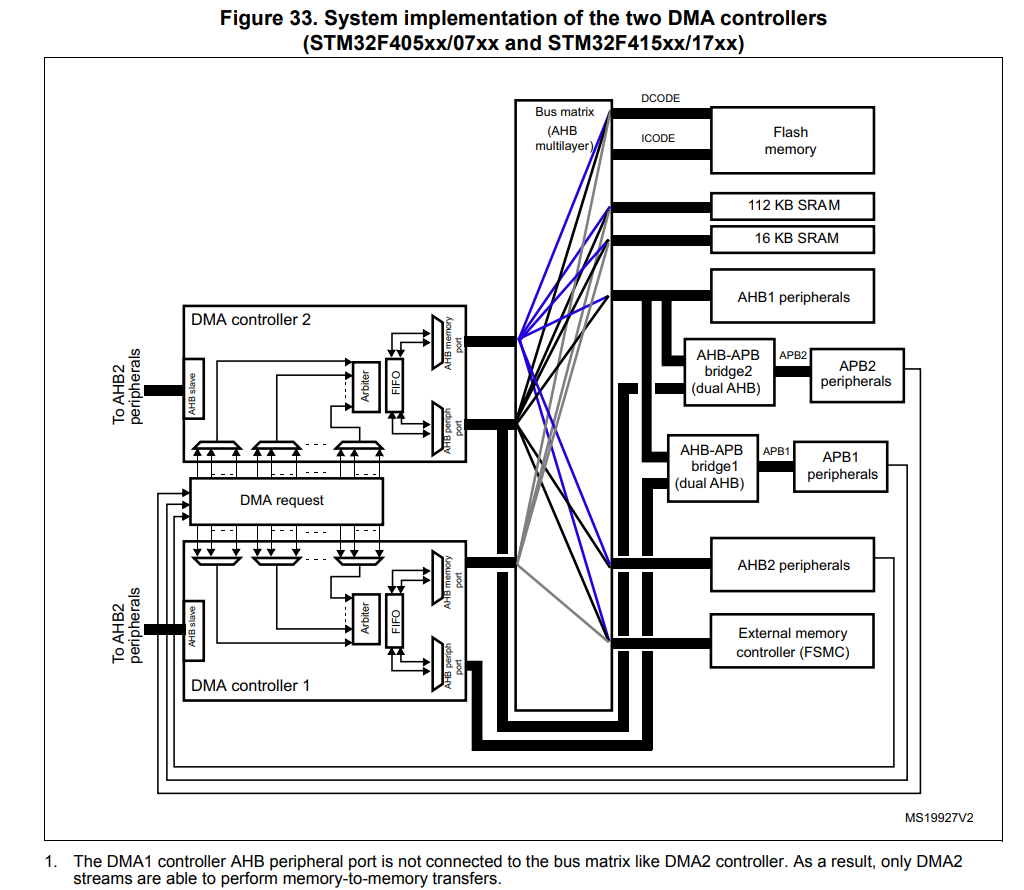

STM32上的DMA矩阵。

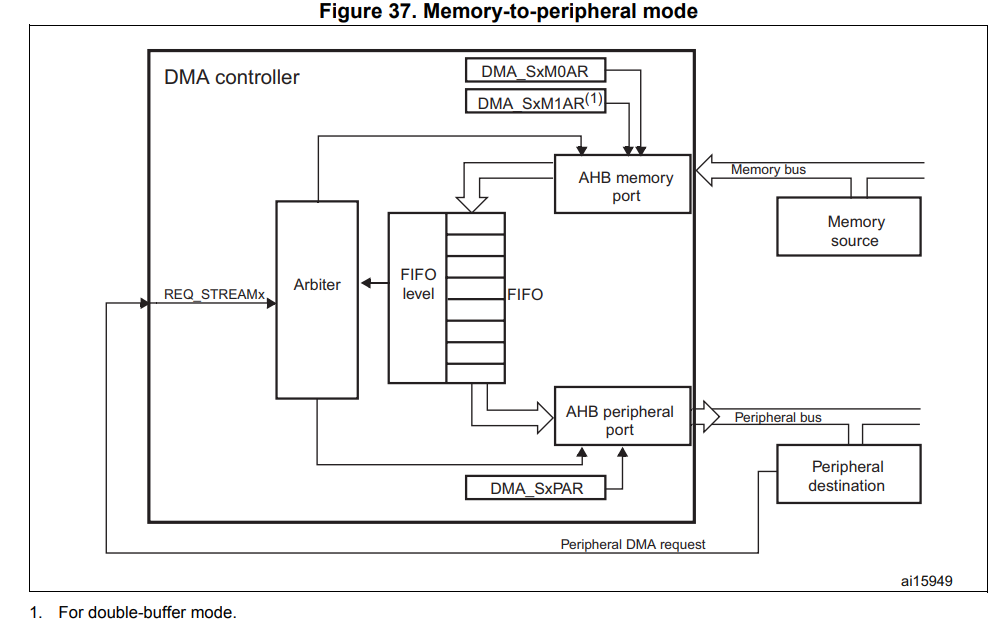

内存到外设模式的内部工作图

需要配置的参数有:

- DMA 数据流 / 通道

- 数据流优先级

- 源和目标地址

- 传输模式

- 传输数据量大小 (仅当 DMA 为流量控制器时)

- 源 / 目标地址递增或非增

- 源和目标数据宽度

- 传输类型

- FIFO 模式

- 源 / 目标批量传输数据量大小

- 双缓冲区模式

- 流控

AN4031 手册有更多的说明。

Block DMA 描述符

Block DMA 支持传输物理地址连续的内存,只需要告诉DMA控制器三元参数描述符(数据长度,源地址,目的地址)

FPGA

FPGA IP 设计和造芯片有一些相同的步骤。我们拿拥有居多开源资源的FPGA资料来看再好不过了。

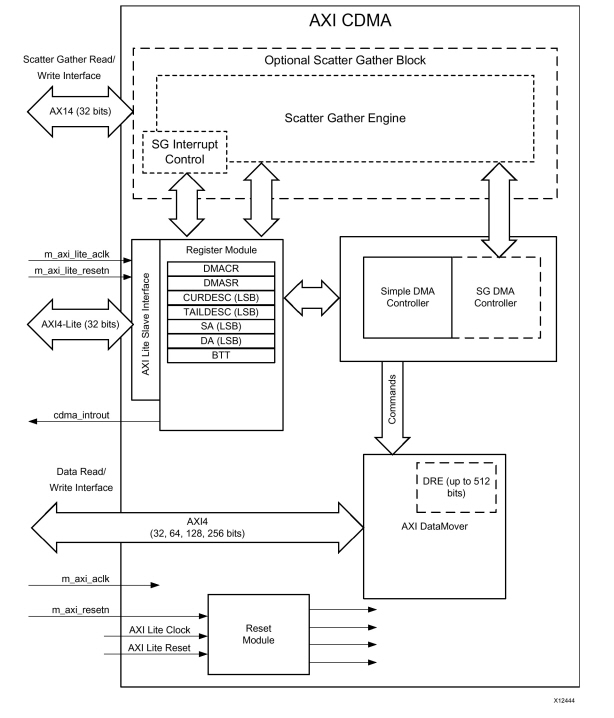

Xilinx IP 之 AXI CDMA

https://docs.amd.com/r/en-US/pg034-axi-cdma/Overview

像赛灵思的IP,控制器支持普通DMA和SGDMA两种,可以非常清晰地看到,SGDMA不同于普通DMA的接口。

该IP对于SGDMA的描述:

The AXI CDMA can optionally include Scatter/Gather (SG) functionality for off-loading CPU management tasks to hardware automation. The Scatter/Gather Engine fetches and updates CDMA control transfer descriptors from system memory through the dedicated AXI4 Scatter Gather Master interface. The SG engine provides internal descriptor queuing, which allows descriptor prefetch and processing in parallel with ongoing CDMA data transfer operations.

可以看到关键字样是off-loading卸载CPU的运算压力。SGDMA引擎提供了内部描述符队列。支持预读取和并行处理。

像在赛灵思的FPGA设计中,SGDMA会比普通DMA多了一个M_AXI_SG总线,用于读取SGDMA的描述符。

Intel IP 之 SG-DMA Controller Core

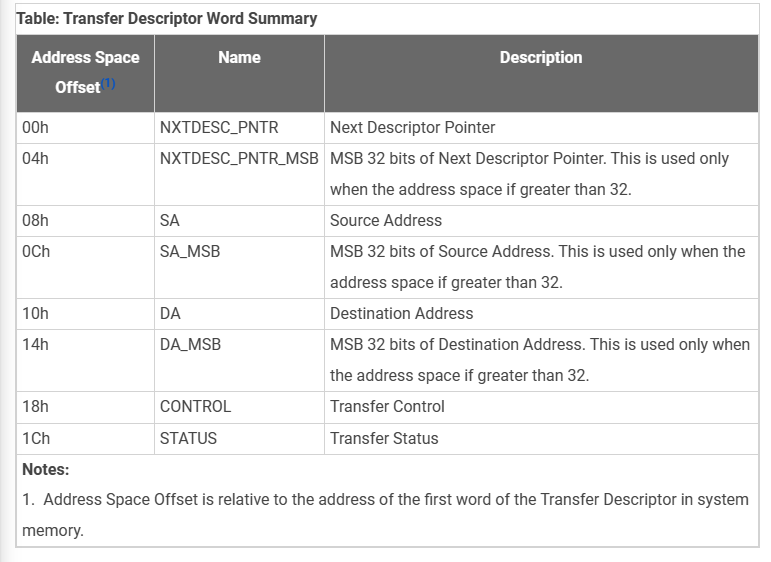

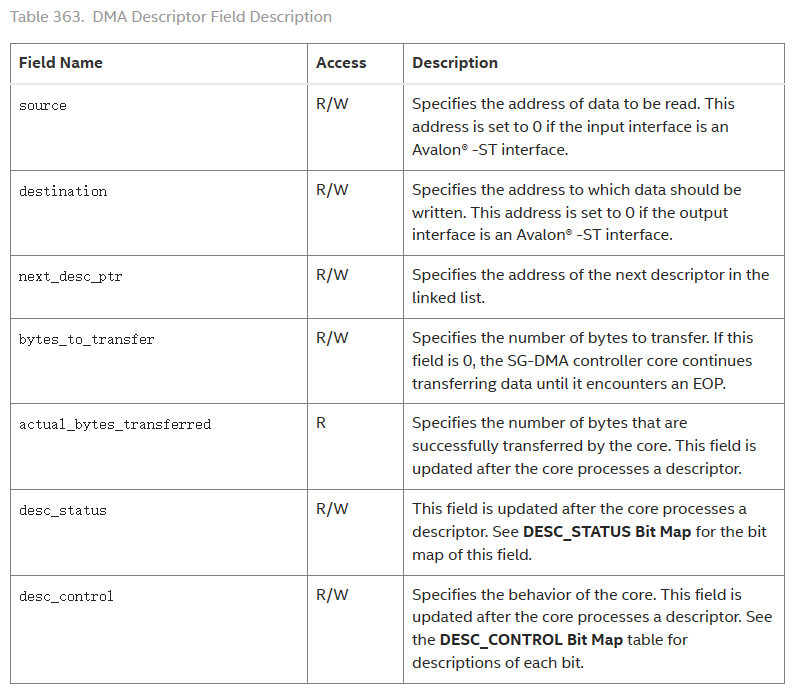

SG-DMA 描述符

我们可以看一下世界两大FPGA巨头的描述符

赛灵思FPGA的寄存器

英特尔旗下FPGA的寄存器

https://www.intel.com/content/www/us/en/docs/programmable/683130/24-1/dma-descriptors-06781.html

需要DMA控制器四元参数描述符(大小,源地址,目的地址,下一链的地址)

如果您需要设计FPGA程序,可以参考这篇:https://www.cnblogs.com/ruidongwu/p/15046127.html

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 阿里最新开源QwQ-32B,效果媲美deepseek-r1满血版,部署成本又又又降低了!

· 开源Multi-agent AI智能体框架aevatar.ai,欢迎大家贡献代码

· Manus重磅发布:全球首款通用AI代理技术深度解析与实战指南

· 被坑几百块钱后,我竟然真的恢复了删除的微信聊天记录!

· AI技术革命,工作效率10个最佳AI工具