AD软件 PCB规则设置

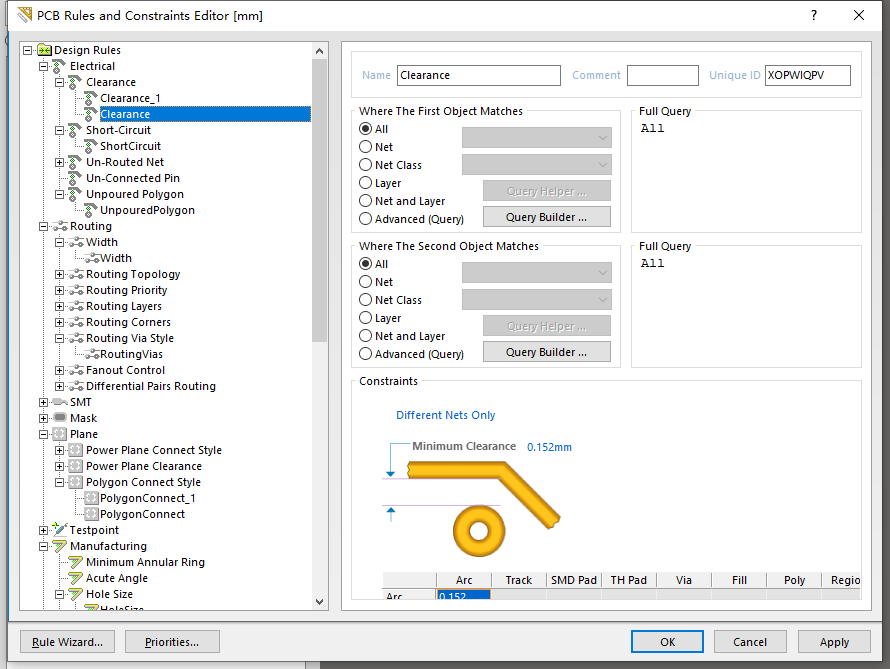

Clearance(间距):不少芯片引脚间距过小,需要将其设置到7mil或者更小,若敷铜采用同样间距,则可能导致部分区域与其他区域地线联通处宽度过小,在大电流情况下导致短线或者信号、电源波动较大;因此需要单独讲敷铜间距进行设置,新建一个间距规则,选择Advanced(Query),点击Query Helper ...,输出Inpolygon

With(走线间距):此处根据实际情况设置,我设置最大都为2.54mm,一般大于1.5mm使用铜箔

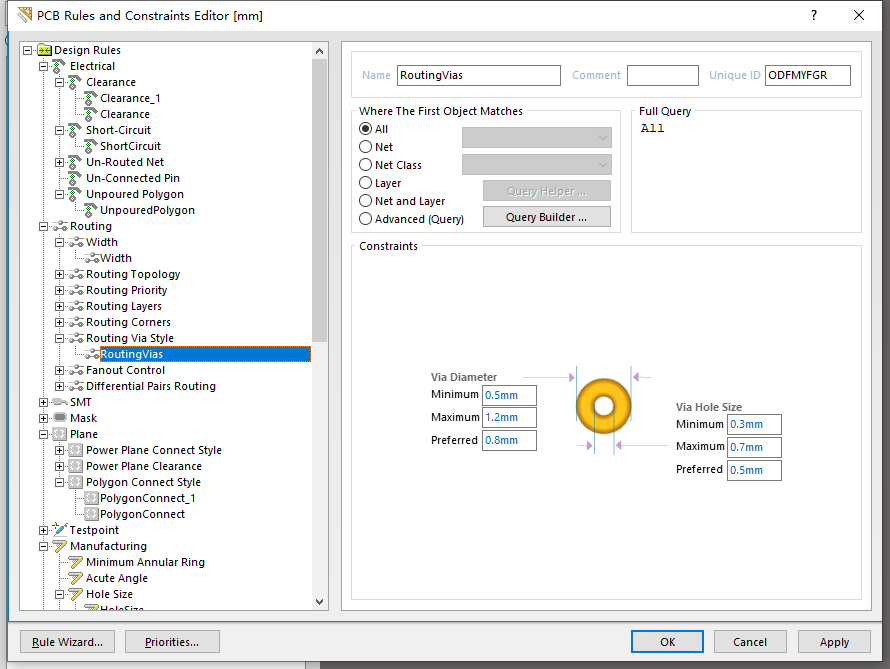

RoutingVias(过孔直径):这样设置方便调用,信号选用Minimum,小电流选用最佳Preferred,大电流选用Maximum

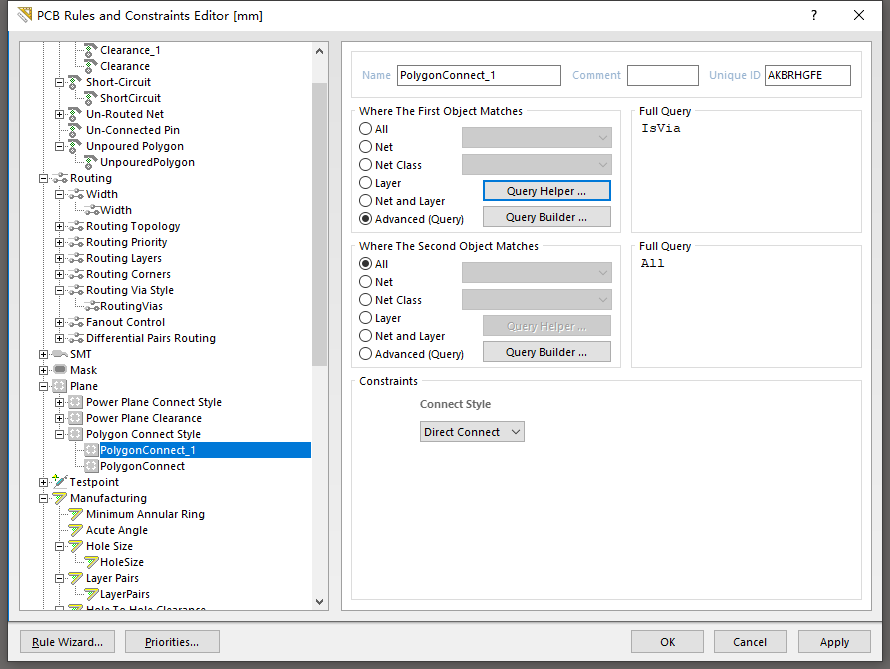

Polygon Connect Style(铜箔连接方式):在电源芯片、电源接插件等需要走大电流部分,使铜箔与其全部连接,可以增大电流通过能力。我一般喜欢将过孔也使用这种模式。格式: Isvia or incomponent('P1') or incomponent('U1')

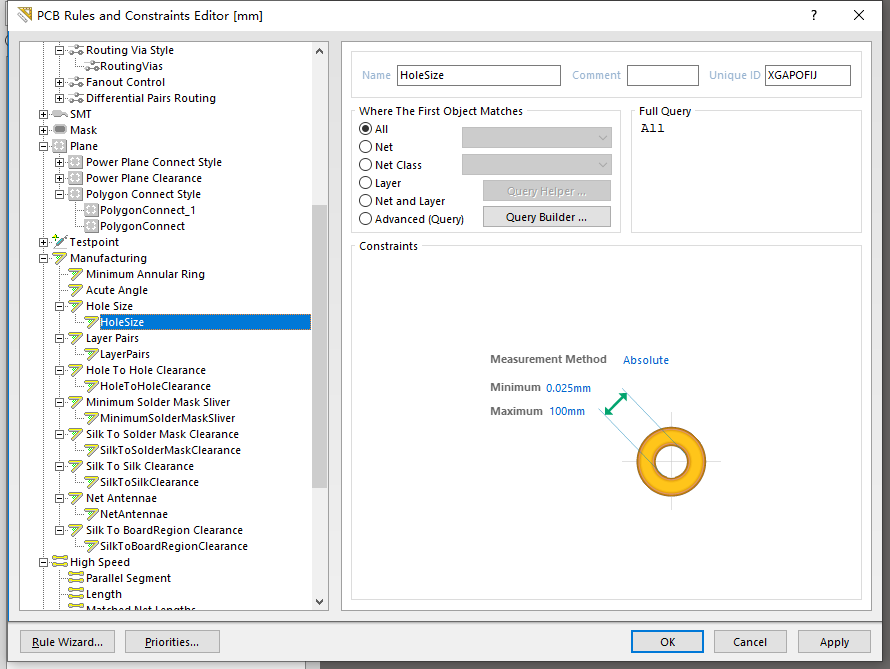

HoleSize(孔尺寸):随意设置

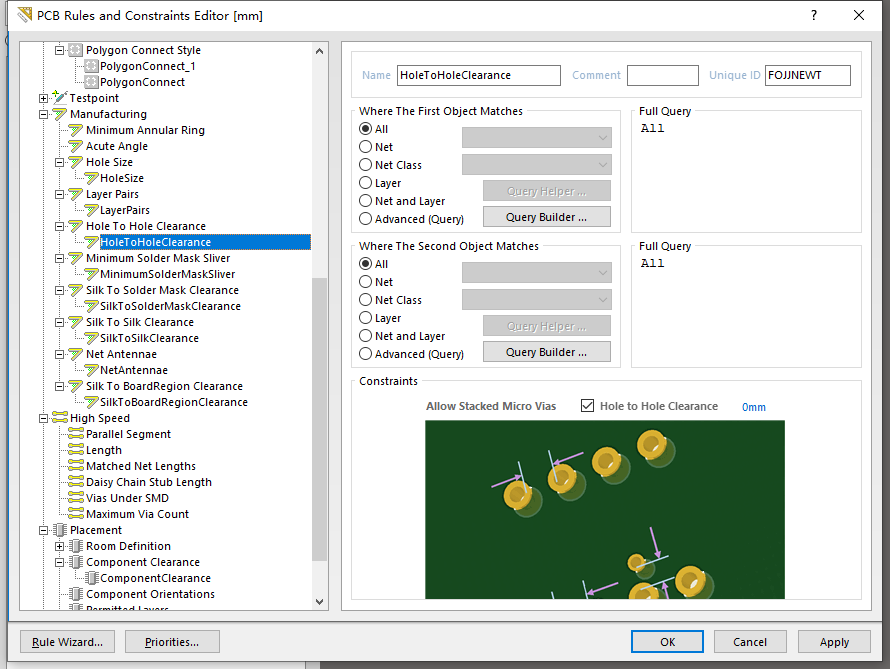

HoleToHoleClearance(孔与孔间距):

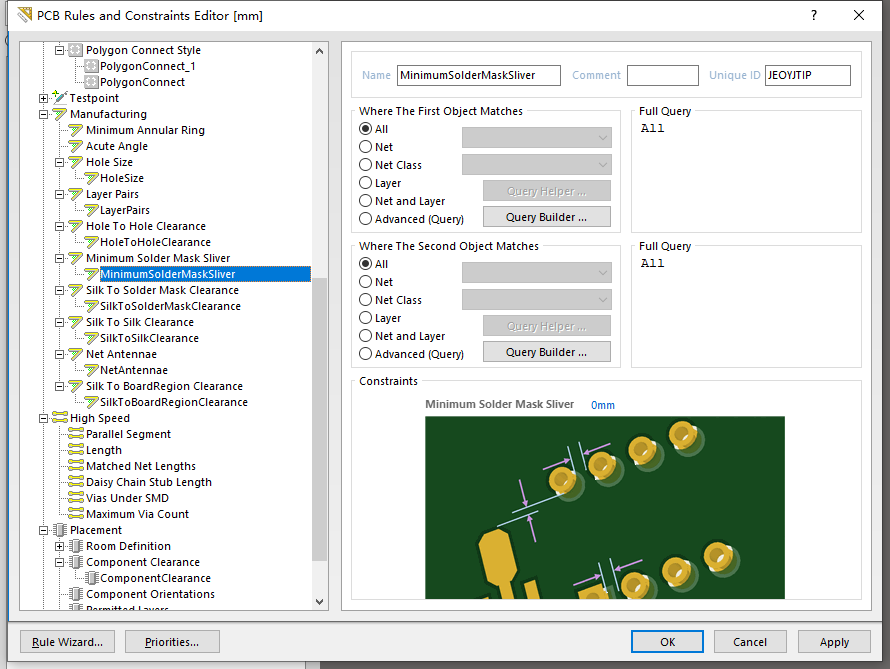

MinimumSolderMaskSliver:

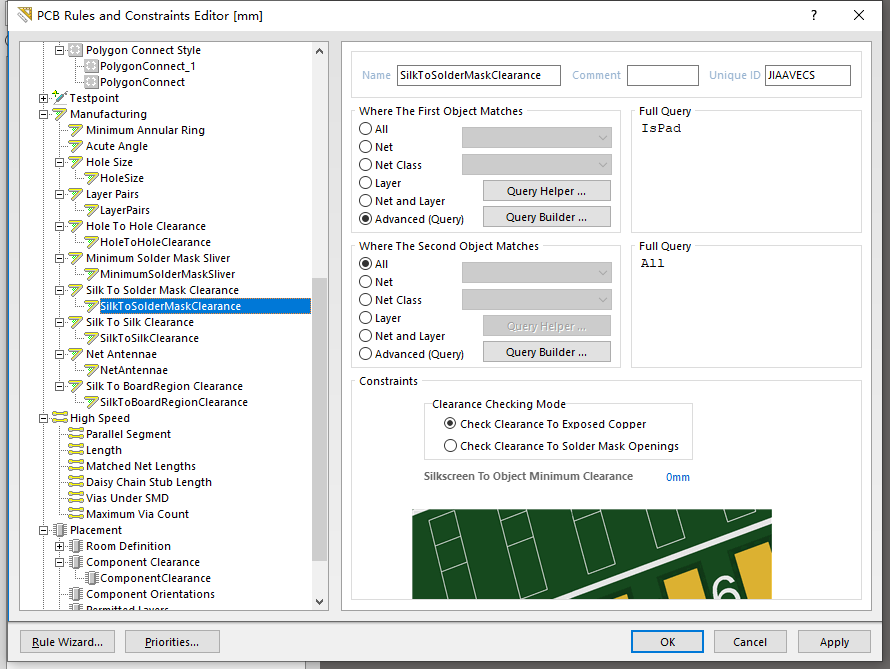

SilkToSolderMaskClearance:

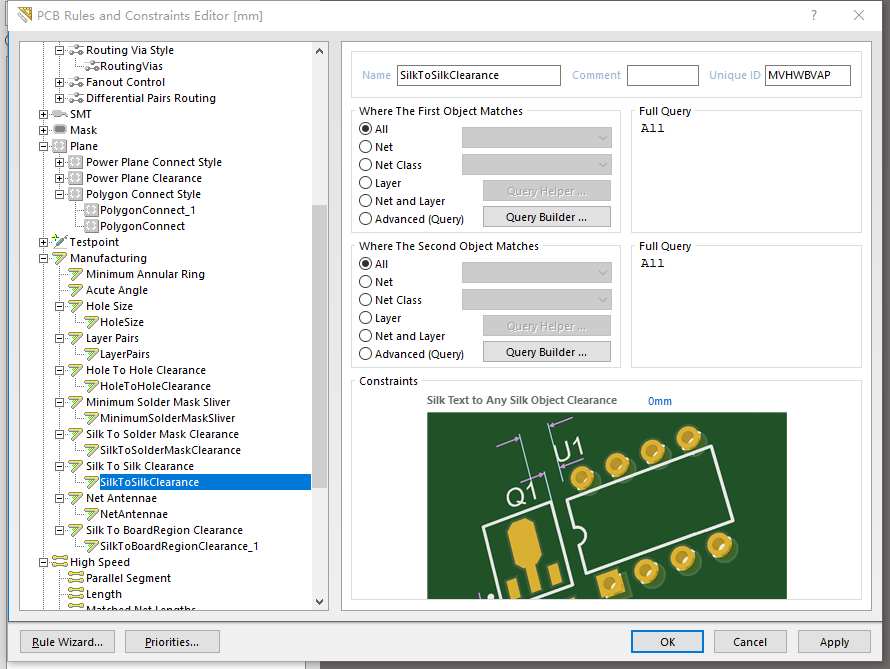

SilkToSilkClearance:

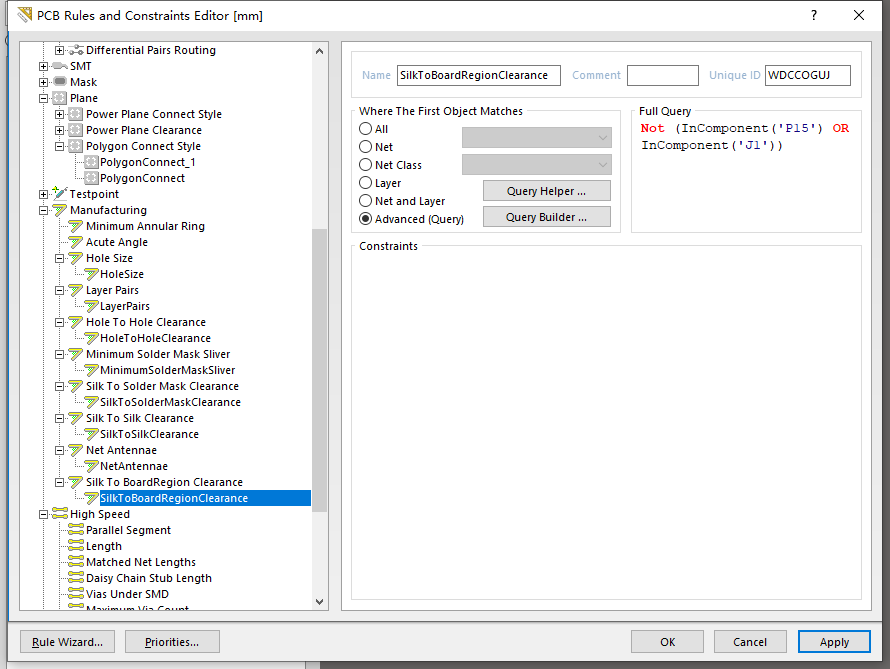

SilkToBoardRegionClearance:消除丝印处于板子外错误。格式:Not (InComponent('P15') OR InComponent('J1'))

ComponentClearance:设置使得芯片或者器件重叠在一起