cortex m0+ NVIC(中断)

1.维基百科:

当外部事件或异常产生时,由硬件负责产生一个中断标记,CPU根据中断标记获得相应中断的中断向量号,然后由CPU根据中断向量表的地址和中断向量号去查找中断向量表获得相应中断号的中断程序地址,进一步执行对应的中断处理程序。

2.在startup_MKE02Z4.s中定义中断函数:

UART0_IRQHandler

ADC_IRQHandler

FTM0_IRQHandler

3. cortex M0+ 中断优先级设置相关问题

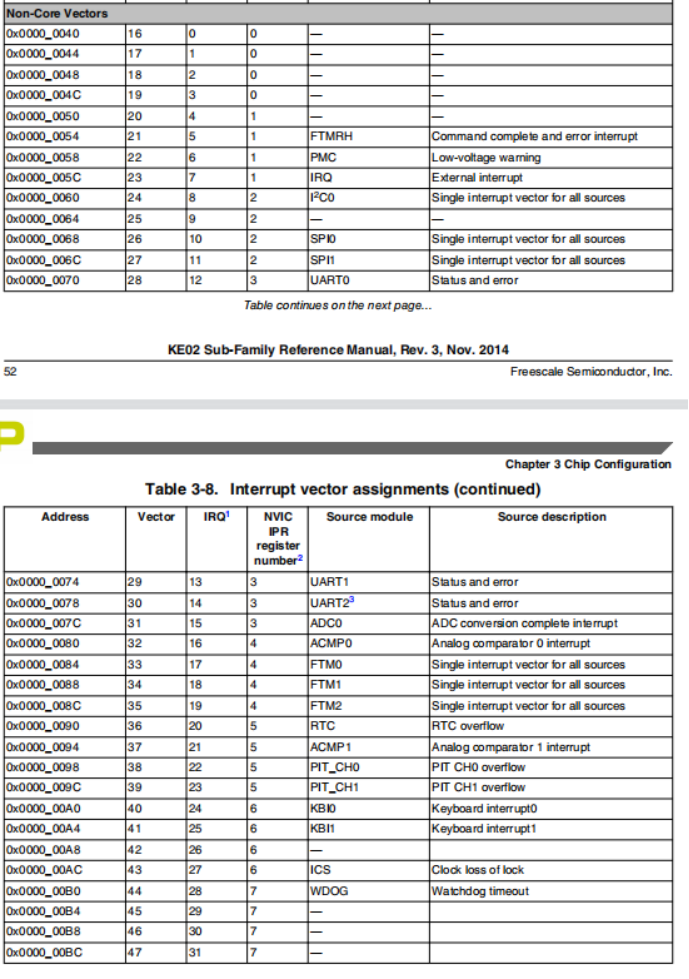

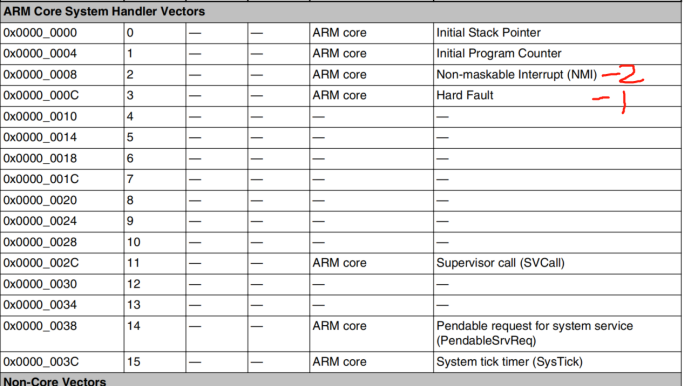

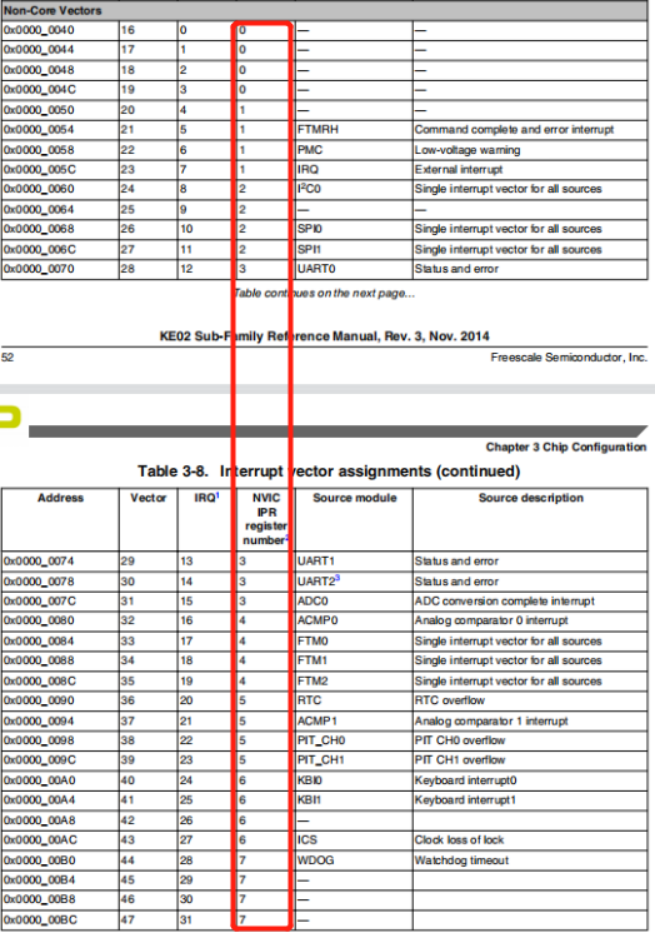

(1)22个非内核中断;7个内核中断,Reset(Initial Program Counter)、NMI和HardFault的执行优先级分别为-3、-2和-1;

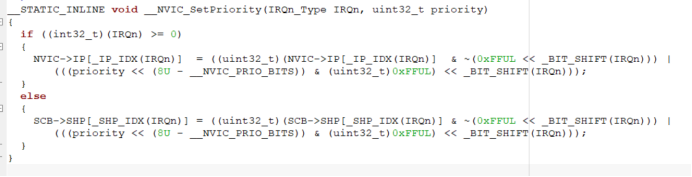

(2)优先级设置函数:

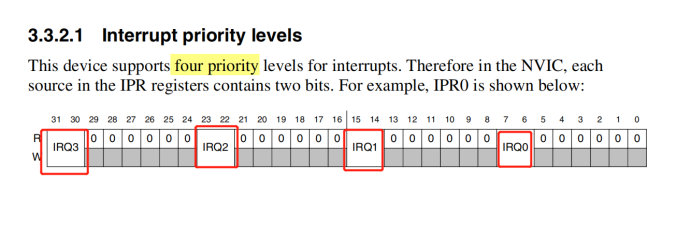

(3)优先级控制器NVIC-IPRn

NVIC-IPR0~NVIC-IPR7一共8个32位寄存器控制非内核中断;

2个bit可以控制4层优先级:0,1,2,3;数字越小,优先级越高;

默认情况下,每个非内核中断的优先级均为0;

优先级高的中断可以抢占优先级低的中断;

同等优先级的中断:向量号小的中断优先级高;

参考文献:ARMv6-M Architecture Reference Manual.pdf

浙公网安备 33010602011771号

浙公网安备 33010602011771号