PCIE状态机-LTSSM

一、PCIE LTSSM

LTSSM是指Link Training and Status State Machine,是PCIe物理层实现的,用于控制和管理PCIe总线上的数据链路。它提供了一组状态,以便设备进行链路训练和链接协商。

在PCIe总线上,发送端和接收端需要进行链路训练,以便确定最佳的链接速度和链接宽度。LTSSM的作用是控制这个过程,并在链路训练期间跟踪链路状态和错误。

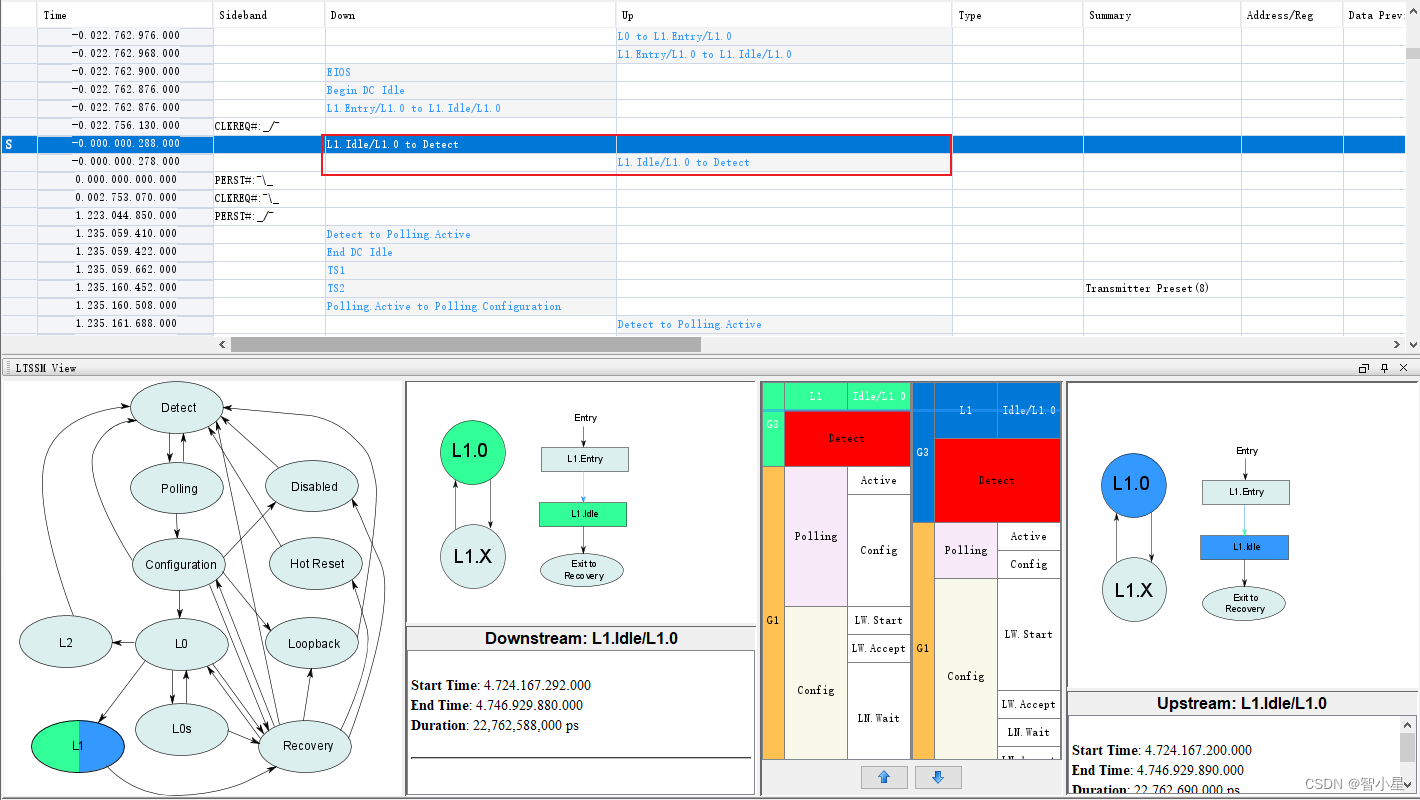

LTSSM状态包括:Detect、Polling、Configuration、Recovery、L0、L0s、L1、L2、Hot Reset、Loopback和Disable。当设备之间开始建立连接时,LTSSM从Detect状态开始。然后,它进入Polling状态,等待对方回应确认连接。如果确认完成,则进入Configuration状态,进行链路配置。之后,LTSSM进入L0状态,表明链路处于活动状态。如果设备需要低功耗状态,则可以进入L0s或L1状态。如果出现错误,则可能会进入L2状态或Loopback状态进行修复。

1. 链路训练和状态机

物理层的链路训练和状态机(LTSSM)模块负责配置和初始化一个设备的物理层、端口的发送器和接收器以及相关的链路,以状态机来管理和描述这个过程。

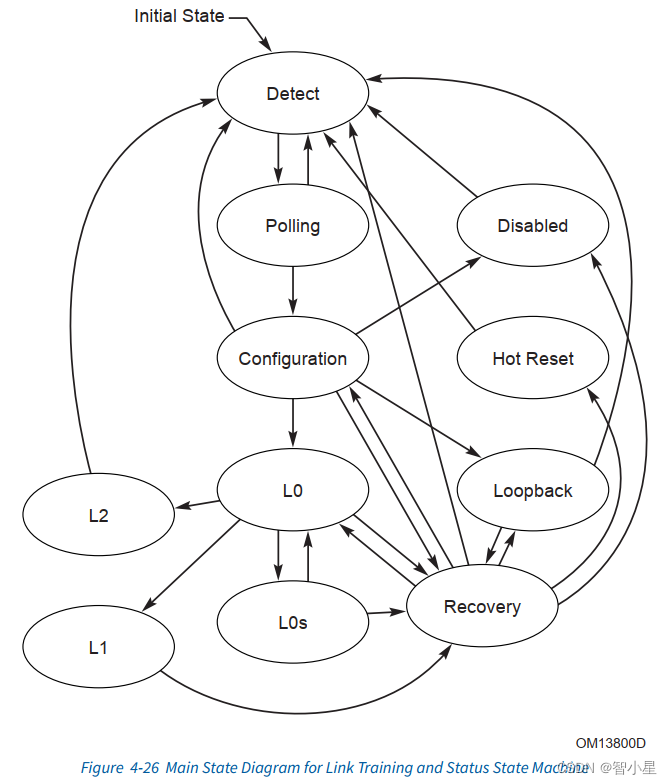

下图展示了LTSSM的 11 个状态,这些状态可以分为以下 4 种类型:

(1)PCIe链路训练状态:Detect、Polling 和 Configuration状态。正常PCIe链路训练状态转换流程:Detect -> Polling -> Configuration -> L0;L0是PCIe链路可以正常工作的电源状态。

(2)PCIe链路重训练状态:Recovery 状态。进入这个状态因素很多,比如电源状态的变化,PCIe链路速率的变化等。

(3)电源管理状态:PCIe总线的电源状态主要有两部分内容。

- 基于软件控制的PCI-PM电源管理机制

- 基于硬件控制的ASPM(Active State Power Management)电源管理机制,是基于硬件自主控制的链路电源管理机制,只有在PCIe设备处于D0状态时才可以启动ASPM机制,与ASPM有关的链路状态有L0、L0s、L1 (包括L1.1和L1.2)和 L2。

(4)其它状态:Disable、Loopback 和 Hot Reset。

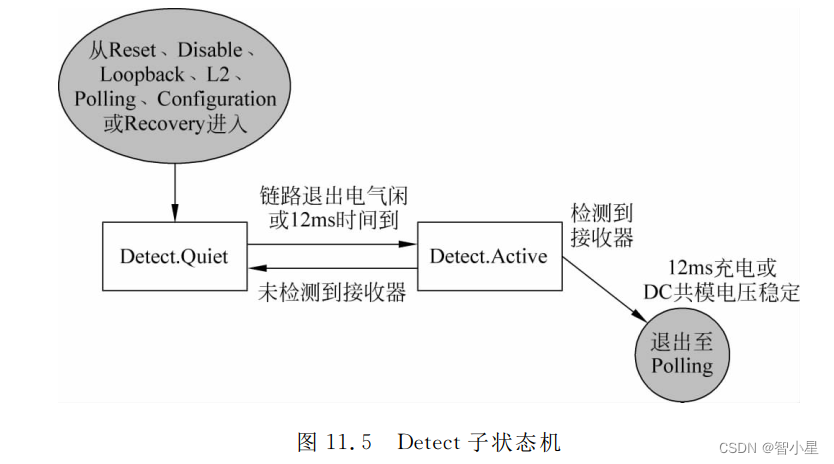

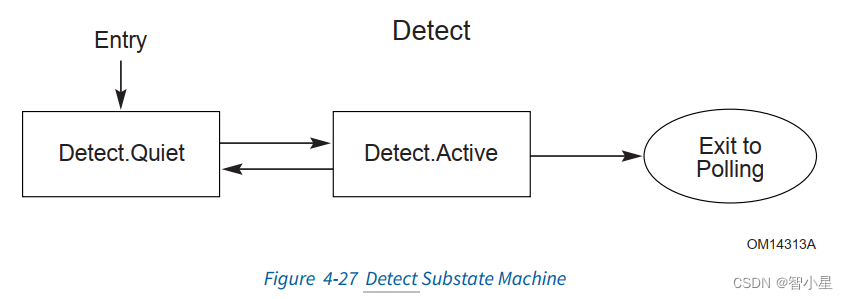

1.1 Detect 状态

Detect 状态是在基本复位或者软件产生的热复位命令后进入的初始状态,在复位80ms内进入这个状态。Detect状态也能从其它状态进入。如下图所示:

Detect有两个子状态:Detect.Quiet 和 Detect.Active。

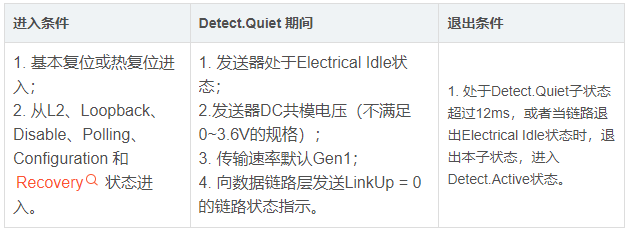

1.1.1 Detect.Quiet 子状态

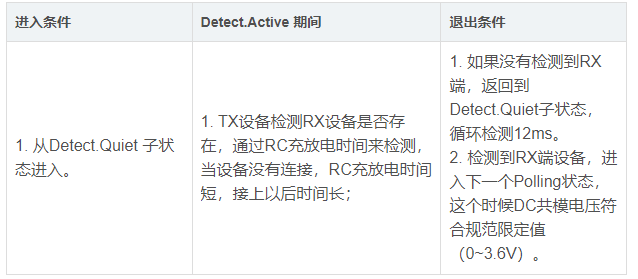

1.1.2 Detect.Active 子状态

我理解的Detect状态是有硬件实现的,且不需要发送PLP包,所有在Trace上看是没有Detect子状态的。

1.2 Polling 状态

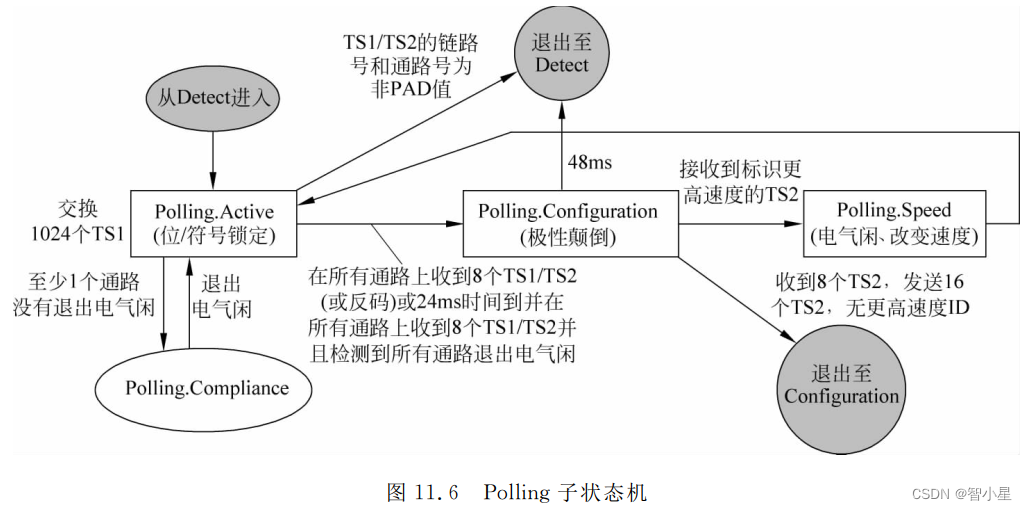

Polling 状态是链路训练和初始化过程中的第一个时段,在这个过程中两相连设备互相发送PLP包(TS1 和 TS2 序列)。Polling 状态机共有 4 个子状态:

- Polling.Active:进行 Bit Lock 和 Symbol Lock;

- Polling.Compliance:进行 Compliance 合规性测试;

- Polling.Configuration:实现极性翻转(Lane Polarity Inversion);

- Polling.Speed:确定链路速率。

- Bit Lock:在Bit传输过程中,RX PLL锁定TX Clock频率,这个过程称为RX实现“Bit Lock”

- Symbol Lock:RX端串并转化器知道如何区分一个有效的10-bit Symbol,这个过程称为“Symbol Lock”,这里用到的是COM控制符。

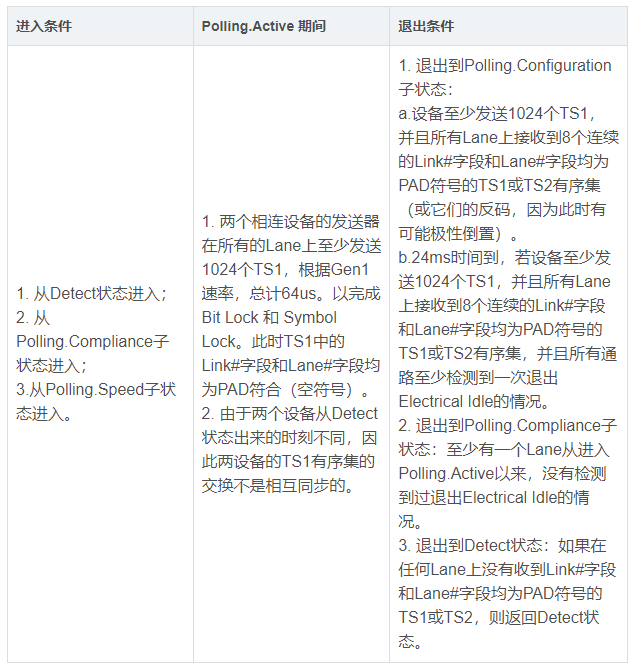

1.2.1 Polling.Active 子状态

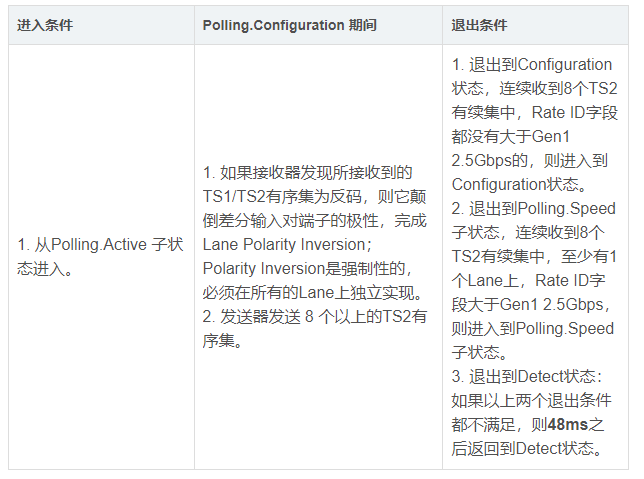

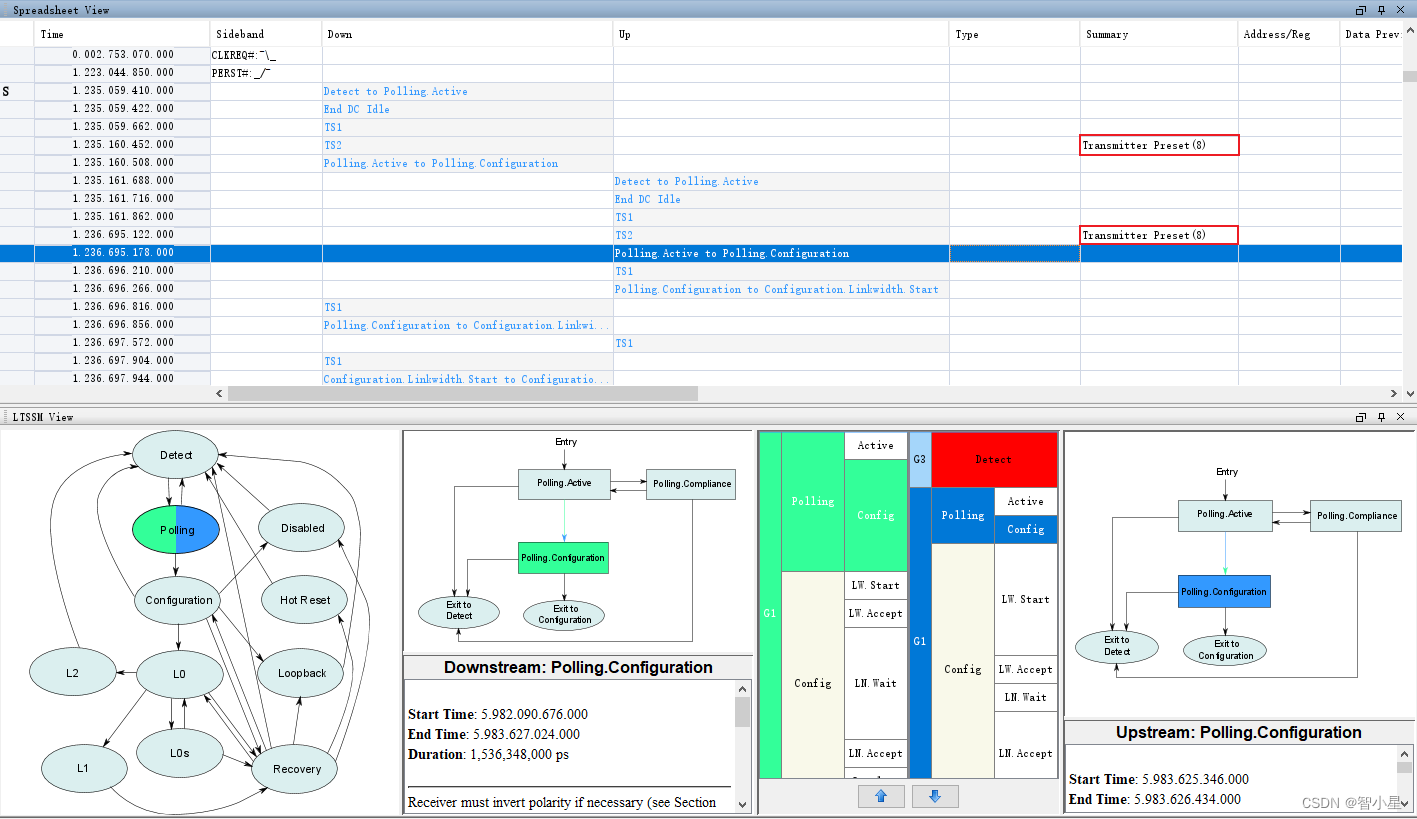

1.2.2 Polling.Configuration 子状态

在 Polling.Active 状态下至少发送1024个TS1 来实现 Bit/Symbol Lock。由于发送端和接收端不是同时退出Detect状态,所以从Trace上看TS1序列交流可能不会同步。随后发送8个TS2有序集,进入Polling.Configuration状态,在这个状态下完成Polarity Inversion极性反转。并进入下一个状态Configuration。

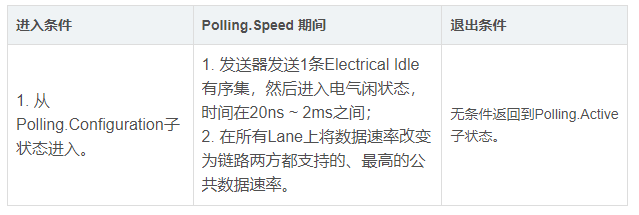

1.2.3 Polling.Speed 子状态

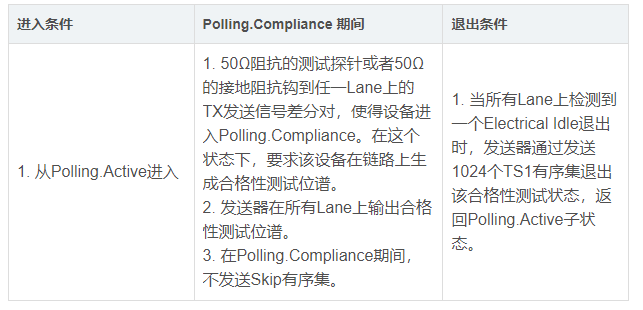

1.2.4 Polling.Compliance 子状态

1.3 Configuration 状态

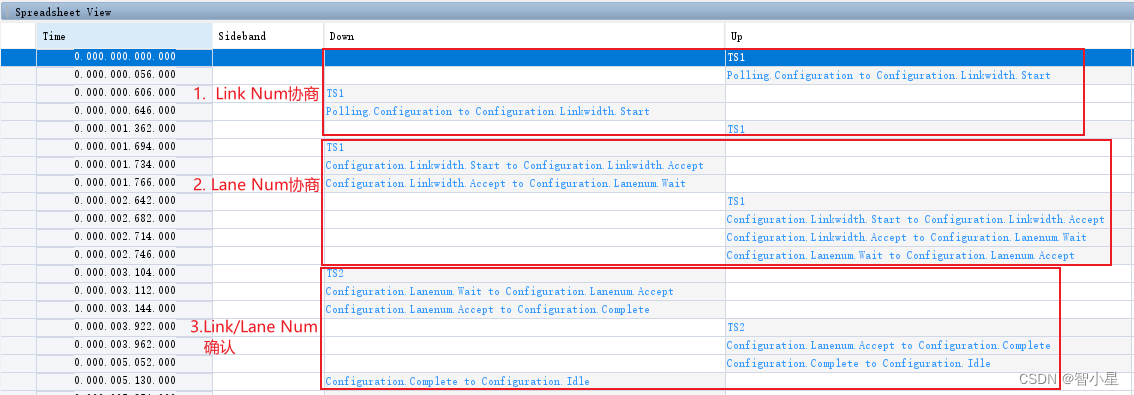

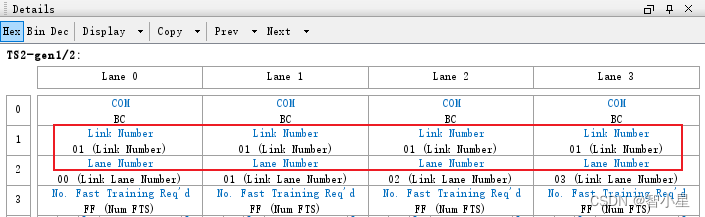

本状态的主要功能是为每一条Lane分配链路号和通路号,去除同一个链路各通路间的时差。上游设备往所有下游通路上发送TS1,下游设备也返回TS1,以此进行链路编号和通路编号。在Link Number 和 Lane Number 成功完成之后,双方再互相发送TS2进行确认。

Configuration包含6个子状态:

- Configuration.Linkwidth.Stat

- Configuration.Linkwidth.Accept

- Configuration.Lanenum.Wait

- Configuration.Lanenum.Accept

- Configuration.Complete

- Configuration.Idle

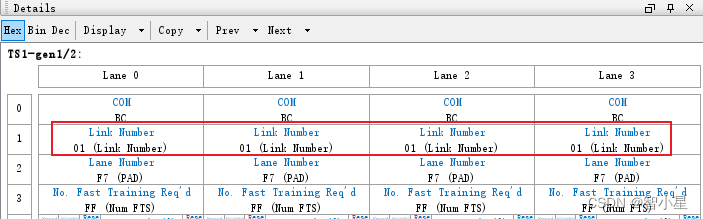

1.3.1 Link Number 协商

Downstream在TS1中设定Link Number,此时Lane Number为PAD,并发送给Upstream。

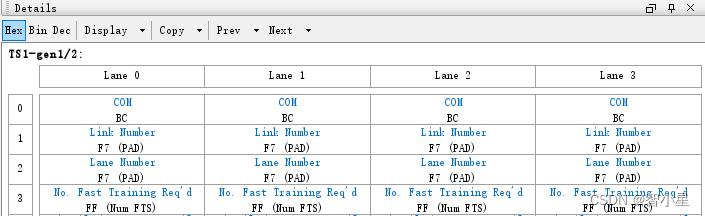

此时Upstream回复的第一个TS1,Link Number还是PAD。

1.3.2 Lane Number 协商

当 Downstream 看到 Upstream 返回的TS1中 Link number 已经是设定值,那么久认为Link num已经协商成功,然后就开始准备设定 Lane number,此时 Downstream 链路也进入Configuration.Linkwidth.Accept状态。

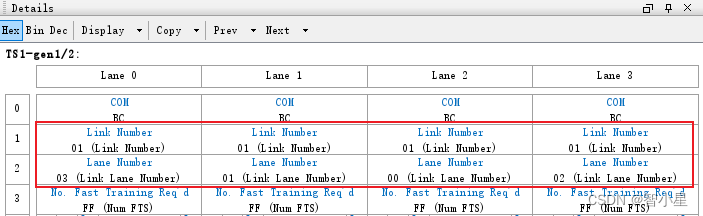

Lane Number 协商过程跟 Link Number 一样,在TS1 中包含了已设定的Link Number 和将要设定的 Lane Number。

Downstream 接收到 Upstream 返回的TS1 的 Lane Number 已经是设定值,Lane Number就协商完成了,接下来进入Configuration.Complete状态。

1.3.3 确认Link/Lane Number

Downstram 和 Upstream 双方通过发送 TS2 序列,对之前设定的Link/Lane number进行确认,这个过程LTSSM处于Configuration.Complete状态, 确认没有问题之后,就准备进入下一个状态。

1.4 L0 状态

当进入这个状态时,PCIe链路就可以愉快的开始正常工作了。这个状态可以传输TLP,DLLP等报文。

1.5 L0s 状态

表示设备处于低功耗状态,但仍能在短时间内快速恢复到L0状态,以响应来自系统的请求。

1.6 L1 状态

表示设备处于更加严格的低功耗模式,需要一些时间才能恢复到L0状态。在L1状态下,设备仍然保持接收来自系统的信号,但不会进行数据传输。

1.7 L2 状态

表示设备处于最低功耗模式,需较长时间才能从其恢复,此时设备已无法响应来自系统的信号。在L2状态下,设备会关闭其传输通道,以达到最低功耗状态。

1.8 Recovery 状态

当PCIe链路需要重新训练时,进入Recovery状态。主要有以下几种情况:

(1)PCIe链路信号发现error,需要调整 Bit Lock 和 Symbol Lock;

(2)从L0s或者L1低功耗电源状态退出;

(3)Speed Change。因为第一次进入L0状态时,PCIe链路速率是2.5GT/s。当需要调整更高(5.0GT/s或8.0GT/s)速率时,需要进入Recovery状态进行Speed Change。这个阶段 Bit Lock、Symbol Lock都需要重新获取;

(4)需要重新调整PCIe链路的Width;

(5)软件触发 Retrain 操作;

(6)仅在Gen3和Gen4,需要重新进行Equaalization。

我们结合一个上电过程中Gen1提速至Gen3的时序来解读一下Recovery状态的转换:

a. Downstream率先进入Recovery.RcvrLock状态, 之后向Upstream持续发送TS1并且将speed_change bit设置为1;

b. Upstream端看到TS1进来之后,也跟着进入Recovery.RcvrLock状态,同时回传TS1序列,不过此时,speed_change bit仍为0. 当Upstream接收达到连续8个TS1且speed_change bit设置为1,这时,Upsteam回传的TS1、TS2中speed_change bit设置为1,并告诉Downstream建议工作速率,接着进入Recovery.RcvrCfg状态;

c. Downstream收到Upstream建议的速率反馈之后,也返回TS2序列,并发送EIOS序列,准备进入Electrical Idle. 此时,LTSSM处于Recovery.RcvrCfg状态;

d. 之后,Downstream 和 Upstream相继进入Electrical Idle, LTSSM处于Recovery.Speed状态;

e. 经过一段时间timeout(Spec要求至少800ns),Upstream发送EIEOS, 退出Electrical Idle, 尝试跑最高速率8GT/s;

f. 接着 Downstream 也退出Electrical Idle, 尝试跑试跑最高速率8GT/s;

g. 最后,双方开始进行EQ。EQ之后,PCIe链路就可以回到正常工作状态。

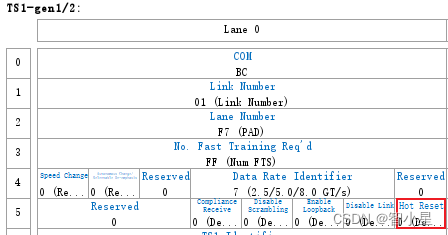

1.9 Hot Reset 状态

当某个PCIe设备发生错误时,我们有时候需要通过软件的方式对设备进行复位,这个方式就是Hot Reset。发送器在下游端口的所有Lane上连续发送Hot Reset 位为1的TS1序列。当接收器收到至少2个带有Hot Reset的位为1的TS1时,然后通过Recovery进入Hot Reset。

Hot Reset的指令是在TS1序列中体现,如下图:

Hot Reset触发之后,LTSSM会进入Recovery和Hot Reset状态,之后会到Detect状态,PCIe链路开始重新训练。

1.10 Disable 状态

用户可以通过设置修改Link Control寄存器,让PCIe链路处于Disabled状态。当退出Disabled状态后,LTSSM回到Dectect,PCIe链路重新训练。

当PCIe设备的驱动程序在系统启动时没有正确加载或出现故障时,该设备可能会进入PCIe Disable状态。在这种情况下,该设备将被禁用,并且无法使用。

1.11 Loopback 状态

PCIe Loopback状态是指在PCIe总线上使用一对物理或逻辑通道之间的默认“回环”路径进行数据传输的状态。这种状态被用于测试和诊断PCIe设备和总线的状况。在PCIe Loopback状态下,设备发送和接收数据,但数据不会离开设备,而是通过物理或逻辑通道返回到发送设备。这个过程可以测试设备的发送和接收能力,以及信号的质量和延迟。PCIe Loopback状态可用于测试所有PCIe层,包括物理层、数据链路层和传输层。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 震惊!C++程序真的从main开始吗?99%的程序员都答错了

· 别再用vector<bool>了!Google高级工程师:这可能是STL最大的设计失误

· 单元测试从入门到精通

· 【硬核科普】Trae如何「偷看」你的代码?零基础破解AI编程运行原理

· 上周热点回顾(3.3-3.9)