design PLL

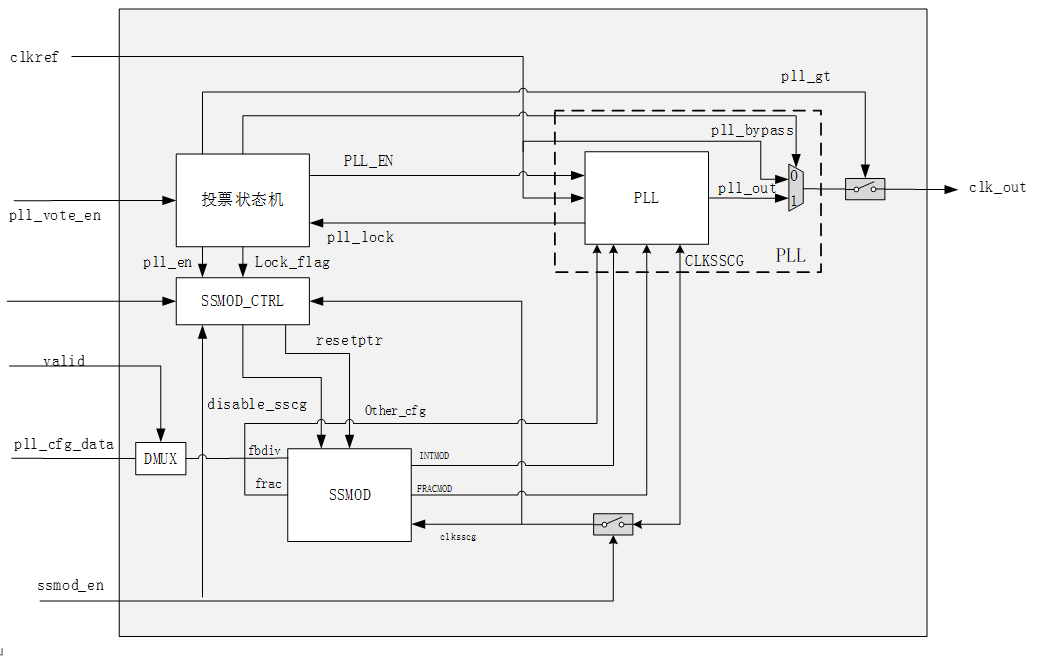

PLL

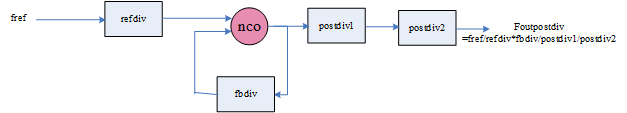

PLL主要是NCO中通过相位比较器,控制压控振荡器,控制频率。

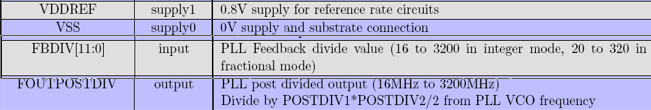

PLL_WRAP

PLL_WRAP内部有3部分组件:投票状态机、展频控制模块、PLL

- 投票状态机:

根据软件或者硬件(来源与pdvfs的寄存器配置)的投票信号控制状态机跳转,也可以关闭这个状态机,使用软件模式来启动PLL(start_fsm_bypass=1)

PLL启动流程

1、复位状态:PLL_EN=0,PLL_BYPASS=1,PLL_GT_EN=0,不启动PLL,选择refclk时钟,不关断输出时钟

2、启动PLL:PLL_EN=1,等待pll_lock(前面已经把ctrl0,ctrl1已经配置好了)

3、开启门控:PLL_GT_EN=1,关闭输出时钟

4、关闭bypss:PLL_BYPASS=0,选择PLL时钟输出

5、关闭门控:PLL_GT_EN=0,打开输出时钟

PLL关闭流程

1、PLL_GT_EN=1,关闭时钟输出

2、PLL_BYPASS=1,选择refclk时钟

3、PLL_GT_EN=0,打开时钟输出

4、PLL_EN=0,关闭PLL

- 展频模块:

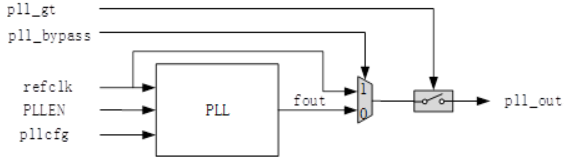

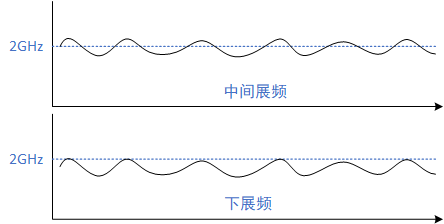

由于CPU/GPU工作的时钟频率很高,达到几个G,会产生很强的电磁干扰(EMI),展频模块用于降低电磁干扰。如果一个时钟一直工作在2GHz的频率上,那么在2G的频点上干扰就会非常强,展频模块就是小幅度调整工作频率的频点,让频率动态变化,不在一个固定的频率上,就可以使干扰分散开,避免一个频点上的大幅度干扰。展频分为中间展频和下展频,分别是让频率在2Ghz左右上下波动和让频率在2GHz下小幅度波动。展频的频率波动范围一般在0.1%~3%,比较小。

展频模块就是对输入的倍频系数进行细微调整:FRACIN->FRACMOD; INTIN->INTMOD

展频模块也是可以bypass的:配置ssmod_en

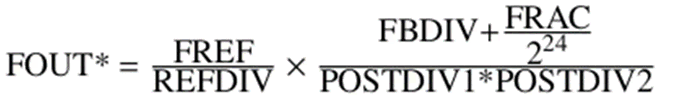

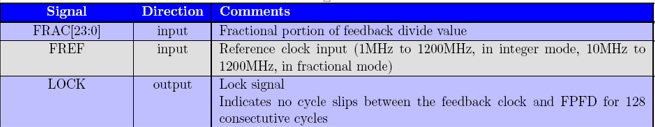

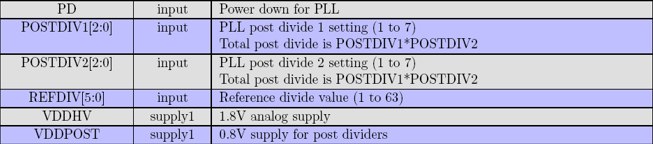

- PLL模块:PLL模块有两种工作模式,小数模式和整数模式,两种模式的输出频率如下公式。小时模式和整数模式通过dsmen信号控制。

整数模式

小数模式