HDLBits--Verilog习题记录5

此题目较难,本文代码也是借鉴别人才完全理解。

题目编号:verification:reading simulations->build a circuit from a simulation waveform->sequential circuit 10

题目描述:

This is a sequential circuit. The circuit consists of combinational logic and one bit of memory (i.e., one flip-flop). The output of the flip-flop has been made observable through the output state.

Read the simulation waveforms to determine what the circuit does, then implement it.

这是一个时序电路。 该电路由组合逻辑和一位存储器(即一个触发器)组成。 触发器的输出已通过输出状态可见。

阅读仿真波形以确定电路的作用,然后实现它。

问题分析:

首先明白上升沿或下降沿在Verilog的中真正含义:

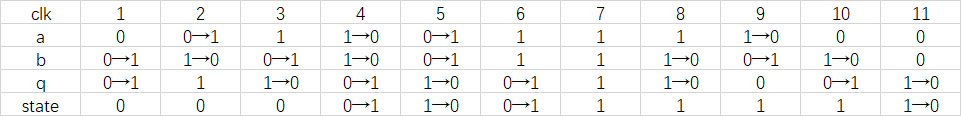

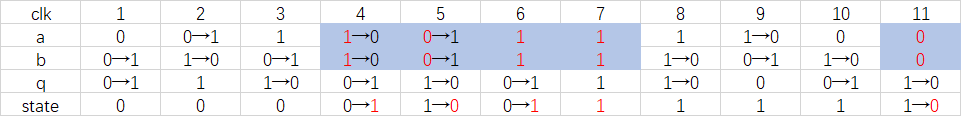

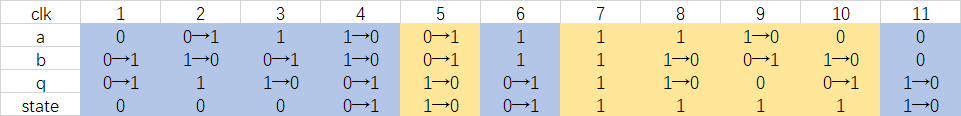

上升沿或下降沿的变化取决于0->1 1->0的起点变化。若上升沿clk时有q<=a;即在上升沿的时候,将时刻“0”位置对应的a的状态位非阻塞赋值给q.

还有就是上升沿(下降沿)的状态虽然起点为0(1),真实状态为1(0),但是它并不能直接认为等于1(0).

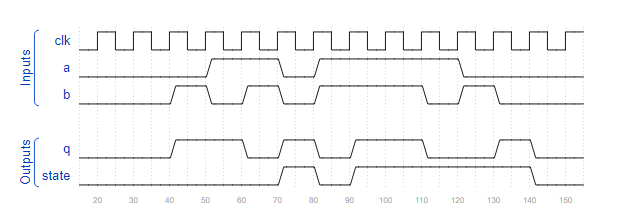

分析整理题目中的图像,列出表格:

观察波形,state较简单,从state入手分析表格数据:

观察之:

当a==b时,state<=a, 这里的state<=a即上文提到的起点变化,将时刻“0”位置对应的a的状态位非阻塞赋值给state。

其他情况则state保持上一个状态不变。

接着分析q,观察q与state之间的关系:

观察易得:

state状态为1,q为a,b同或结果

state状态为0,q为a,b异或结果

代码解析:

module top_module ( input clk, input a, input b, output q, output state ); always @(posedge clk) begin if(a==b) state <= a; else state <= state; end assign q= state?~a^b:a^b; endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号