HDLBits--Verilog习题记录3

3.Circuits---Sequential Logic---Latches and Flip-Flops----Detect an edge

问题描述:

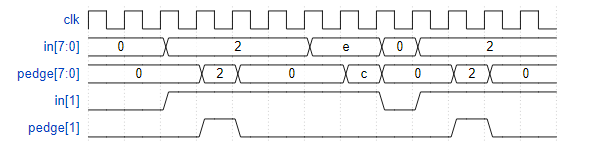

For each bit in an 8-bit vector, detect when the input signal changes from 0 in one clock cycle to 1 the next (similar to positive edge detection). The output bit should be set the cycle after a 0 to 1 transition occurs.

Here are some examples. For clarity, in[1] and pedge[1] are shown separately.

对于 8 位向量中的每一位,检测输入信号何时从一个时钟周期中的 0 变为下一个时钟周期中的 1(类似于上升沿检测)。 输出位应在 0 到 1 转换发生后的周期设置。

这里有些例子。 为清楚起见,in[1] 和 pedge[1] 分开显示。

问题分析:该题目中的pedge的功能是记录上一次的上升沿,为了区分两个不同的触发上升沿,可以使用两条always语句块。另外pedge每一位的结果的计算过程是0->1(上升沿),结果位为1,,即当某位的上一个状态是0,下一个状态为1,此时对应的pedge位为1。其余情况(0->0,1->1,1->0)对应的pedge位为0.通过简单观察知,计算表达式为:pedge=(pre_in)&~(now_in),或者用if来判断每一位也可。

代码解析:

module top_module ( input clk, input [7:0] in, output [7:0] pedge ); reg [7:0]temp; always@(posedge clk) temp=in; always@(posedge clk) pedge = in&~temp; /* begin pedge[0]=(temp[0]==0&&in[0]==1)?1:0; pedge[1]=(temp[1]==0&&in[1]==1)?1:0; pedge[2]=(temp[2]==0&&in[2]==1)?1:0; pedge[3]=(temp[3]==0&&in[3]==1)?1:0; pedge[4]=(temp[4]==0&&in[4]==1)?1:0; pedge[5]=(temp[5]==0&&in[5]==1)?1:0; pedge[6]=(temp[6]==0&&in[6]==1)?1:0; pedge[7]=(temp[7]==0&&in[7]==1)?1:0; end */ endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号