HDLBits--Verilog习题记录1

本文档是Verilog编程题的解题记录

1.Verilog Language--more Verilog features---Generate for-loop:100-bit binary adder2

题目说明:

Create a 100-bit binary ripple-carry adder by instantiating 100 full adders. The adder adds two 100-bit numbers and a carry-in to produce a 100-bit sum and carry out. To encourage you to actually instantiate full adders, also output the carry-out from each full adder in the ripple-carry adder. cout[99] is the final carry-out from the last full adder, and is the carry-out you usually see.

译文:

通过实例化 100 个全加器来创建一个 100 位二进制纹波进位加法器。 加法器将两个 100 位数字和一个进位相加以产生 100 位和并执行。 为了鼓励您实际实例化全加器,还要输出纹波进位加法器中每个全加器的进位输出。 cout[99] 是最后一个全加器的最终进位,也是您通常看到的进位。

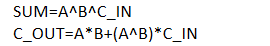

解题思路:已知两个一位的全加器公式

可以使用for循环,遍历每一位即可得到100位的全加器

代码:

module top_module( input [99:0] a, b, input cin, output [99:0] cout, output [99:0] sum ); integer i=0; reg med; always@(*) begin med=cin; for(i=0;i<100;i=i+1) begin sum[i]=med^a[i]^b[i]; cout[i]=(a[i]&b[i])|((a[i]^b[i])&med); med=cout[i]; end end endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号