I2C虚拟项目学习记录

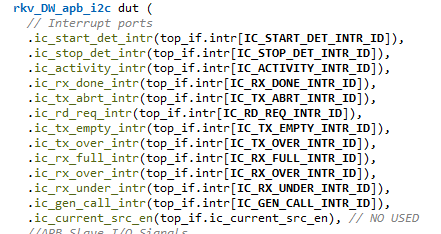

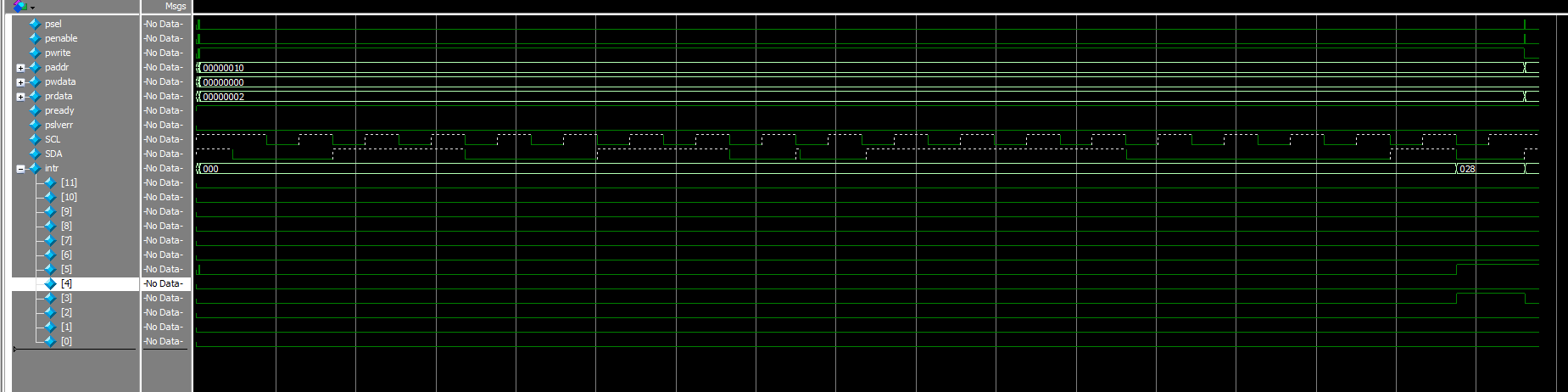

DUT中中断信号的连接

对应的参数定义

parameter IC_INTR_NUM = 12;

parameter IC_RX_OVER_INTR_ID = 0;

parameter IC_RX_UNDER_INTR_ID = 1;

parameter IC_TX_OVER_INTR_ID = 2;

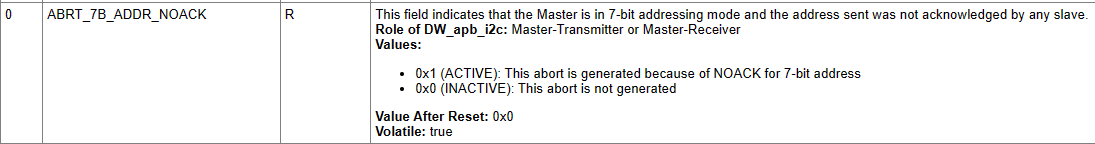

parameter IC_TX_ABRT_INTR_ID = 3;

parameter IC_RX_DONE_INTR_ID = 4;

parameter IC_TX_EMPTY_INTR_ID = 5;

parameter IC_ACTIVITY_INTR_ID = 6;

parameter IC_STOP_DET_INTR_ID = 7;

parameter IC_START_DET_INTR_ID = 8;

parameter IC_RD_REQ_INTR_ID = 9;

parameter IC_RX_FULL_INTR_ID = 10;

parameter IC_GEN_CALL_INTR_ID = 11;

IC_INTR_MASK的默认值

M_RX_UNDER == 1;

M_RX_OVER == 1;

M_RX_FULL == 1;

M_TX_OVER == 1;

M_TX_EMPTY == 1;

M_RD_REQ == 1;

M_TX_ABRT == 1;

M_RX_DONE == 1;

M_ACTIVITY == 0;

M_STOP_DET == 0;

M_START_DET== 0;

M_GEN_CALL == 1;

M_RESTART_DET_read_only == 0;

//1 means interrupt is unmasked

//0 means interrupt is masked

中断屏蔽寄存器

中断屏蔽就是有选择地让中断系统不理睬某些中断源的中断请求,使这些中断信号暂时不被CPU“感觉”,但信号仍保留,以便条件允许时再响应。CPU可用指令将其置1或置0。置0时封闭该设备的中断请求触发器INTR,使其不能将中断请求IR发出。

中断响应的条件

每当一个指令周期结束后,若中断源有中断请求(中断请求标记INTR=1),且CPU允许接受中断请求(处于开中断,EINT=1),CPU就可响应中断请求,进入中断周期。

在I2C中默认不能发出中断请求的中断源为:M_ACTIVITY、M_STOP_DET、M_START_DET、M_RESTART_DET_read_only

I2C的test

1.寄存器测试

采用寄存器模型的内建序列uvm_reg_hw_reset_seq、uvm_reg_bit_bash_seq、uvm_reg_access_seq进行测试。

uvm_reg_hw_reset_seq用于检查上电复位后寄存器模型与DUT中寄存器的默认值是否相同。对于寄存器模型,调用reset函数来使其内寄存器的值变为默认值(复位值)。

uvm_reg_access_seq用于检查寄存器的读写功能,要求寄存器的HDL路径已经完成映射。

uvm_reg_bit_bash_seq检查所有支持读写访问的阈。

rgm.reset();

uvm_reg_bit_bash_seq.model = rgm;

uvm_reg_bit_bahs_seq.start(m_sequencer);

2. I2C module status 测试

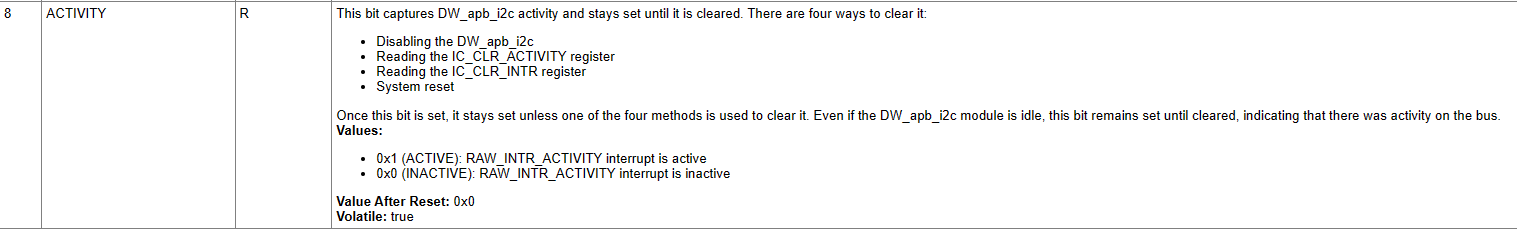

activity(start、stop)

IC_RAW_INTR_STAT bit[8] captures DW_apb_i2c activity and stays set until it is cleared.

四种清除activity中断的方式:disable DW_apb_i2c;读IC_CLR_ACTIVITY寄存器;读IC_CLR_INTR寄存器;系统复位。

该中断默认是被屏蔽的,在初始配置时,应该将其打开。然后正常读写,等待中断清除中断。

enable

使能DW_apb_i2c:关闭I2C,写数据;写数据,在未收到数据前,关闭I2C;读数据过程中关闭I2C;正常模式下是否能写。

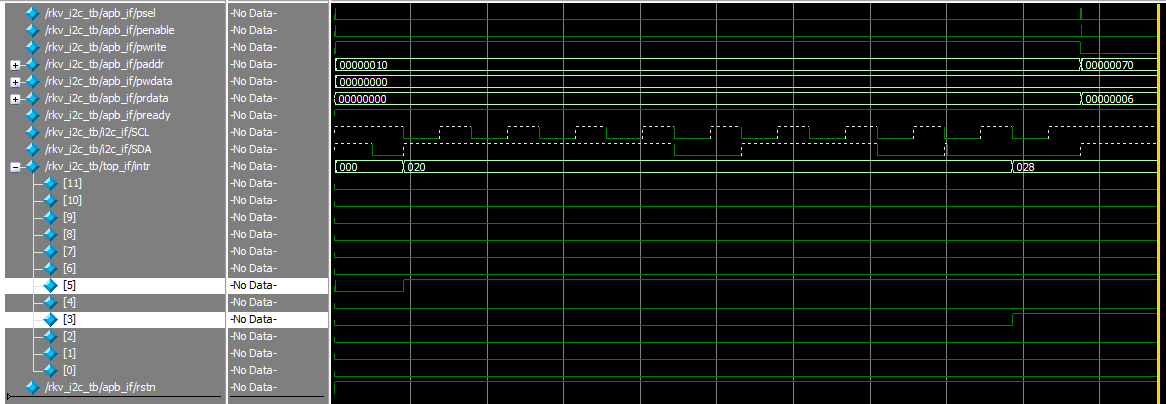

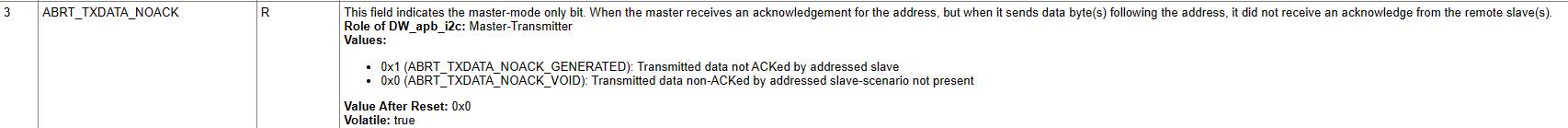

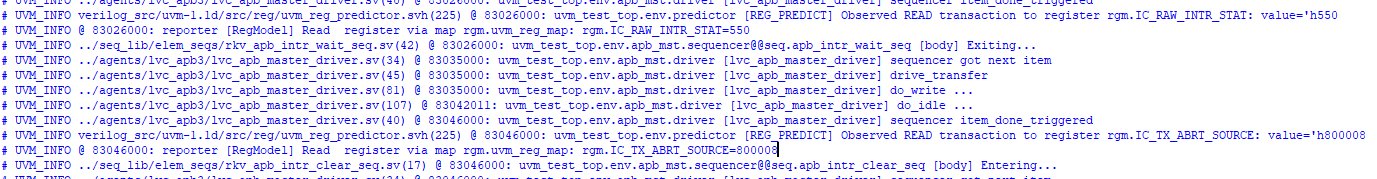

3.interrupt

中断状态寄存器能否正确反映中断状态;中断清楚寄存器能否正常清除中断;识别不同的tx abort源;

4.data buffer

FIFO的空满溢出;TX FIFO/RX FIFO;

5. I2C协议(function description)

三种速度模式;两种寻址方式;组合传输;控制SDA hold time;restart条件;

6.timeout counter

test case

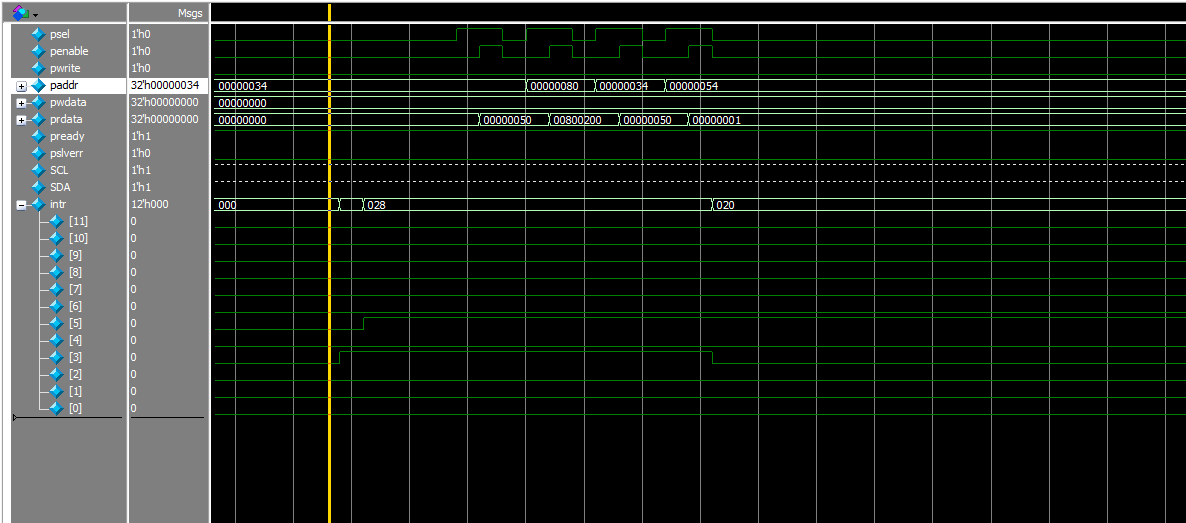

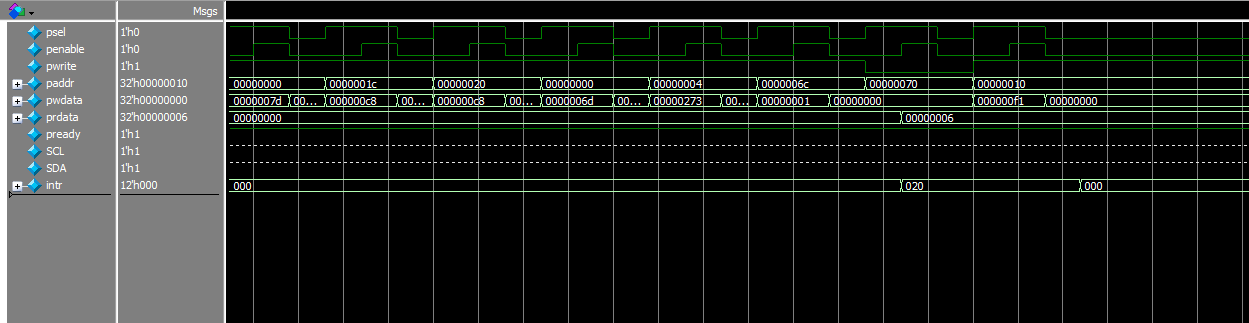

rkv_i2c_master_abrt_7b_addr_noack_test

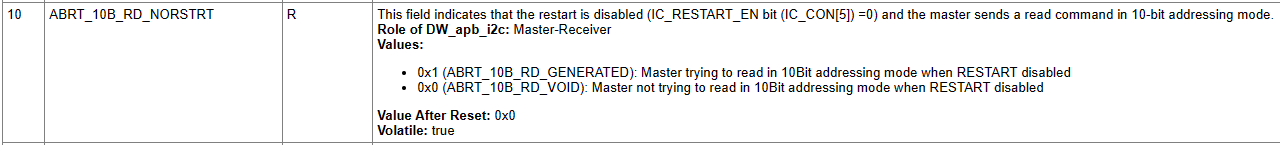

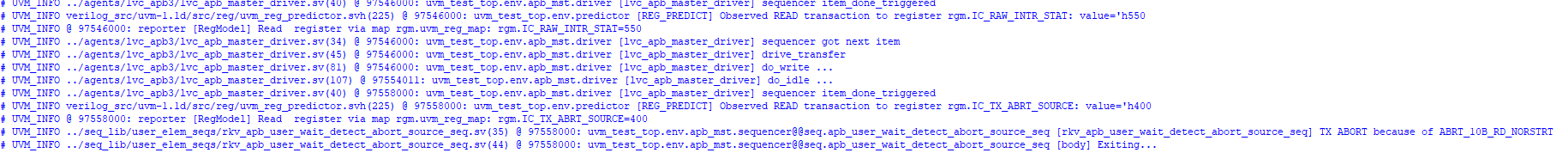

rkv_i2c_master_abrt_10b_rd_norstrt_test

rkv_i2c_master_abrt_7b_addr_noack_test

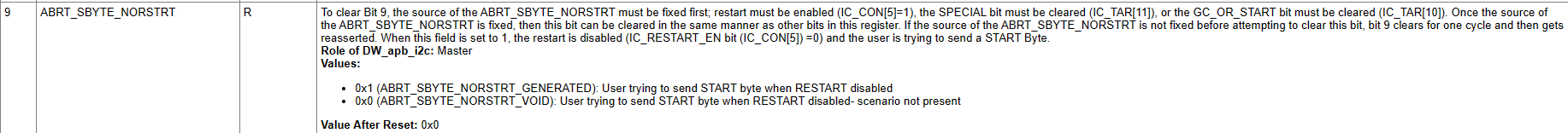

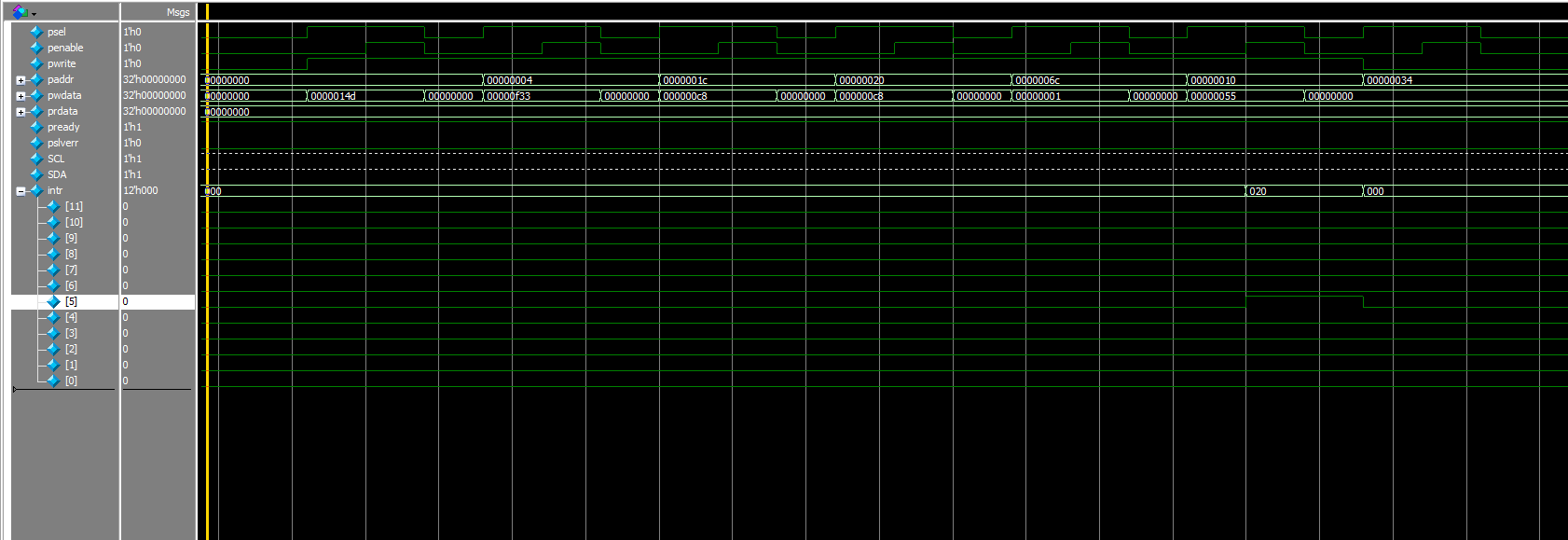

rkv_i2c_master_abrt_sbyte_norstrt_test

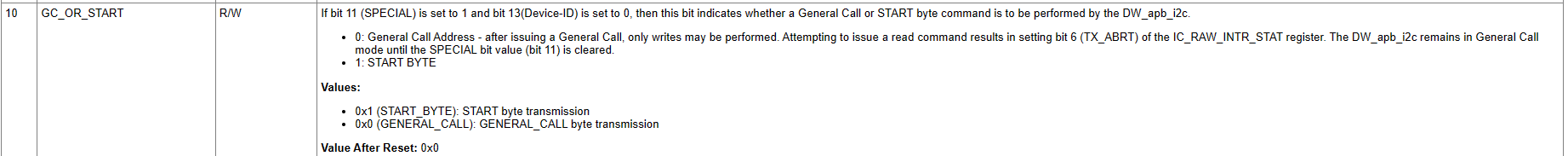

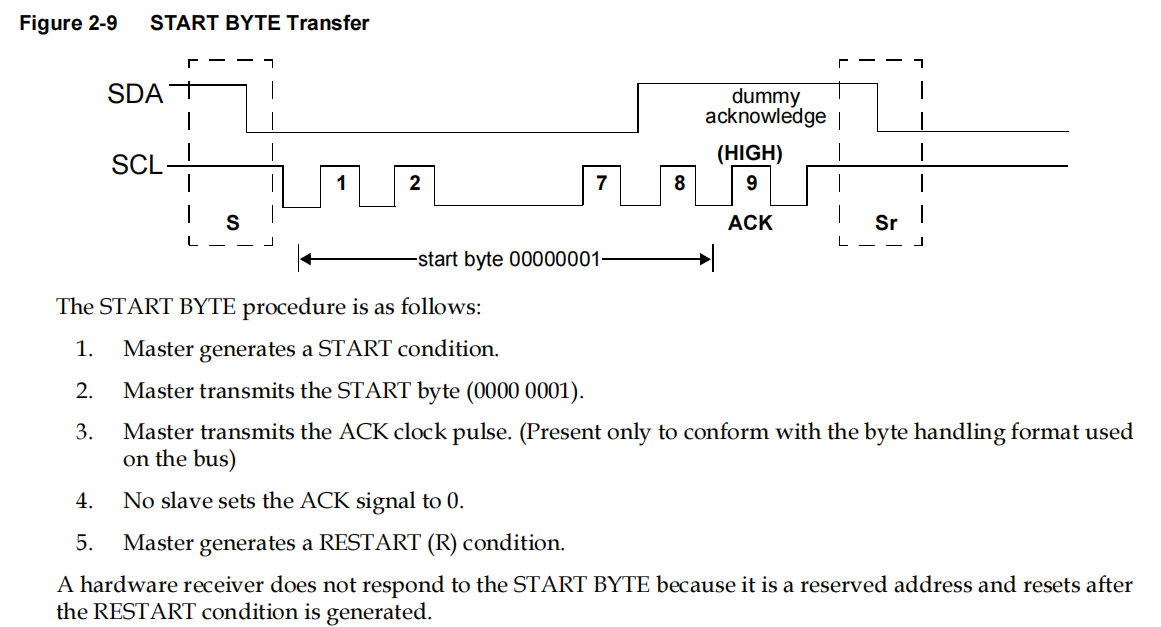

IC_TAR

DW_apb_i2c被寻址为从机时,支持以最高速度对I2C进行采样,不需要start byte传输;但是当其为主设备时,支持在每次传输时生成start byte传输,以备从设备需要。switch from the under-sample sampling to the correct rate of the master;

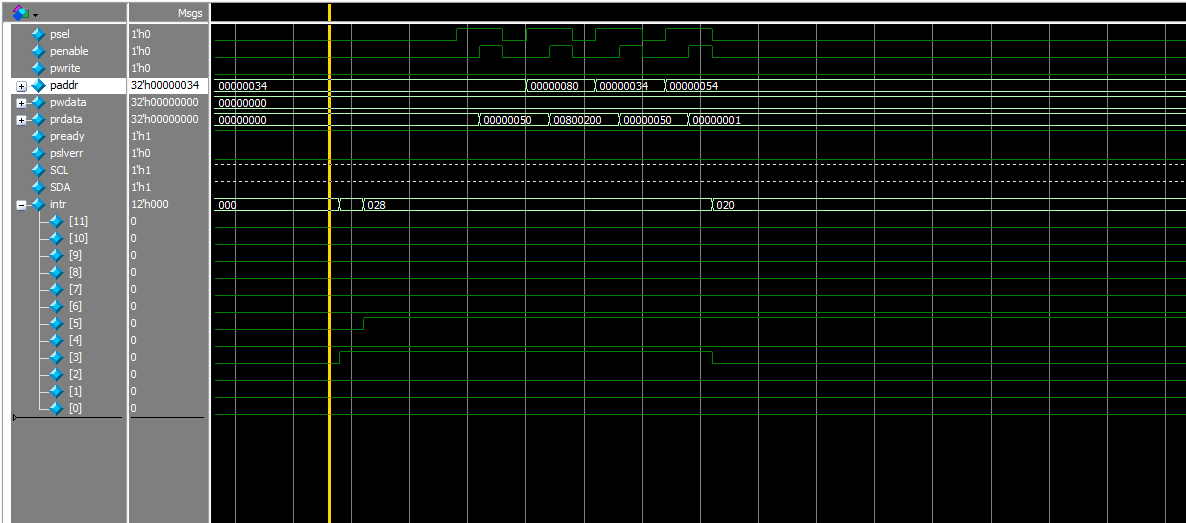

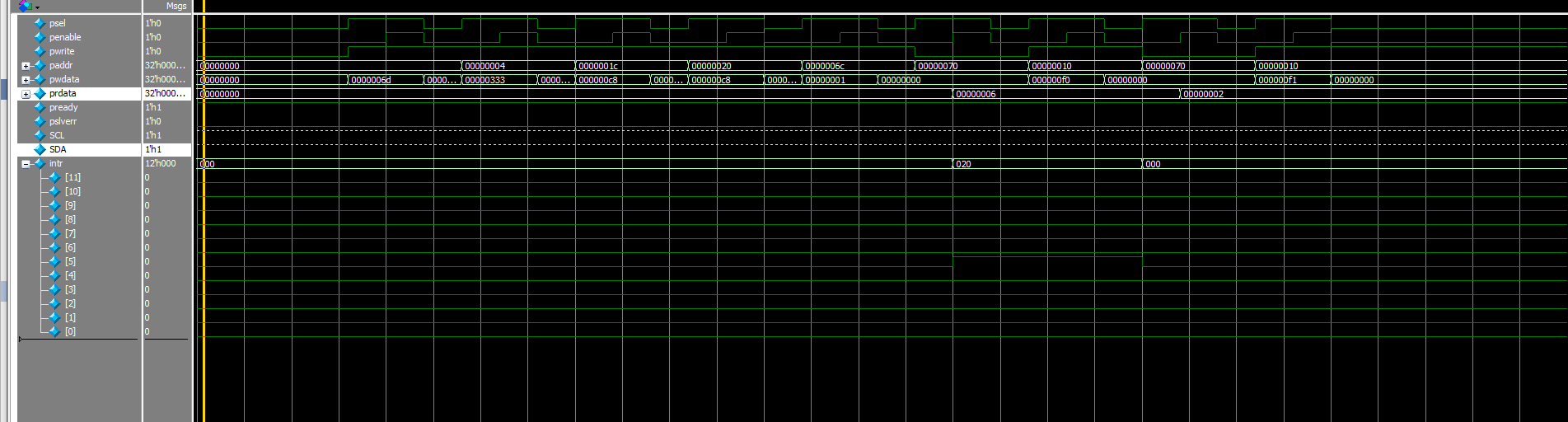

在寄存器上的访问

点击查看代码

`uvm_do_on_with(apb_user_cfg_seq,

p_sequencer.apb_mst_sqr,

{SPEED == 2;

IC_10BITADDR_MASTER == 0;

IC_RESTART_EN == 0;

TX_EMPTY_CTRL == 1; //0x0 IC_CON write 1_0100_1101

IC_TAR == `LVC_I2C_SLAVE0_ADDRESS;

SPECIAL == 1;

GC_OR_START == 1; // 0x4 IC_TAR write 1111_0011_0011

IC_FS_SCL_HCNT == 200; // 0x1c IC_FS_SCL_HCNT WRITE 'hc8

IC_FS_SCL_LCNT == 200; //0x20 IC_FS_SCL_HCNT write 'hc8(200)

ENABLE == 1; // 0x6c IC_ENABLE write 'h1

})

fork

`uvm_do_on_with(i2c_slv_write_resp_seq,

p_sequencer.i2c_slv_sqr,

{nack_addr == 0;

})

join_none

`uvm_do_on_with(apb_user_write_packet_seq,

p_sequencer.apb_mst_sqr,

{packet.size() == 1;

packet[0] == 8'b0101_0101; //0x10 IC_DATA_CMD write 0101_0101

})

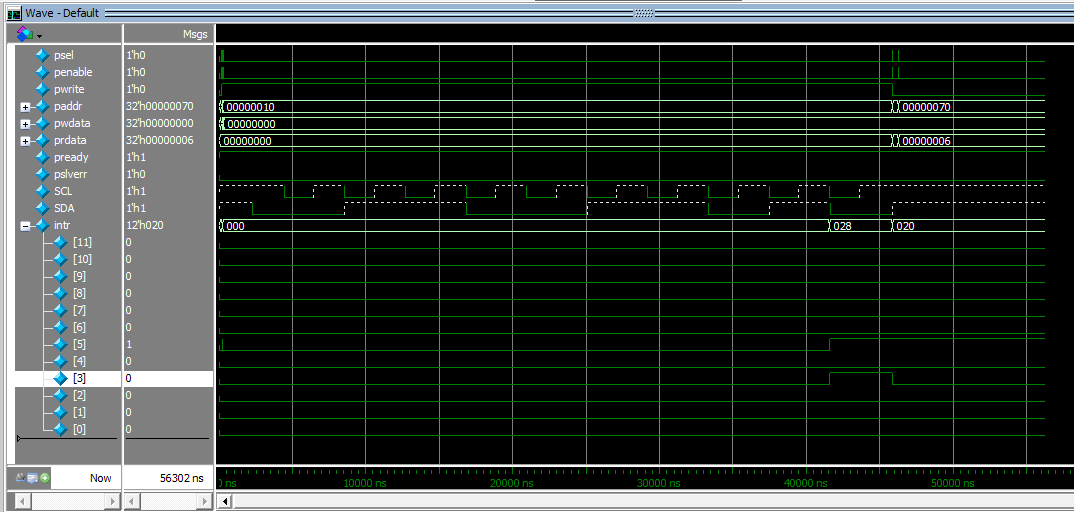

`uvm_do_on_with(apb_intr_wait_seq,

p_sequencer.apb_mst_sqr, //0x34 IC_RAW_INTR_STAT polling read until get 0101_0000

{intr_id == IC_TX_ABRT_INTR_ID;

})

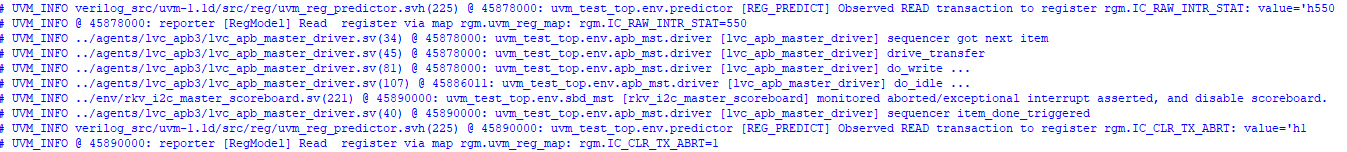

rgm.IC_TX_ABRT_SOURCE.mirror(status); //0x80 IC_TX_ABRT_SOURCE read 'h00800200

// check if interrupt output is same as interrupt status field

if(vif.get_intr(IC_TX_ABRT_INTR_ID) !== 1'b1)

`uvm_error("INTRERR", "interrupt output IC_RX_UNDER_INTR_ID is not high")

`uvm_do_on_with(apb_intr_clear_seq, //0x54 IC_CLR_TX_ABRT read 'h00000001

p_sequencer.apb_mst_sqr,

{intr_id == IC_TX_ABRT_INTR_ID;

})

`uvm_do_on(apb_user_wait_empty_seq, p_sequencer.apb_mst_sqr) //0x70 IC_STATUS read 'h00000006

在最后一次检查到中断信号前,中断信号拉起,等到访问完中断清楚寄存器后,中断信号拉低

rkv_i2c_master_activity_intr_output_test

rkv_i2c_master_abrt_txdata_noack_test

地址阶段Nack,之后发起中断

rkv_i2c_master_address_cg_test

apb总线

寄存器访问的方法:

read:读寄存器,读回硬件实际值;操作完成后,寄存器模型根据读写的结果更新期望值和镜像值。做的任何读写,bus看到了就会更新镜像值。

write:写寄存器,修改硬件实际值;

peek&poke:后门访问的方式读取/修改硬件实际值,操作完成后,rgm更新镜像值和期望值。

mirror:读回硬件实际值,更新寄存器模型镜像值和期望值。

set&get:修改/获取register和field的期望值。

update:检查寄存器的期望值和镜像值是否一致,若不一致,将期望值写入DUT,并更新镜像值,使其与期望值一致。

randomize:randomize期望值,镜像值不变。

浙公网安备 33010602011771号

浙公网安备 33010602011771号