DSP28335学习笔记(1)

DSP28335最小系统

-

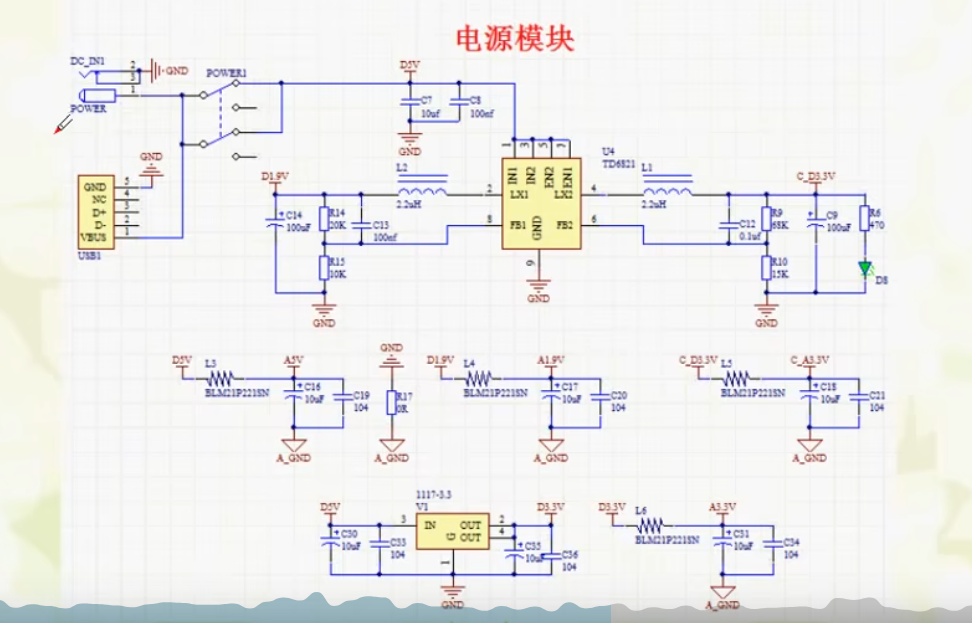

电源电路

-

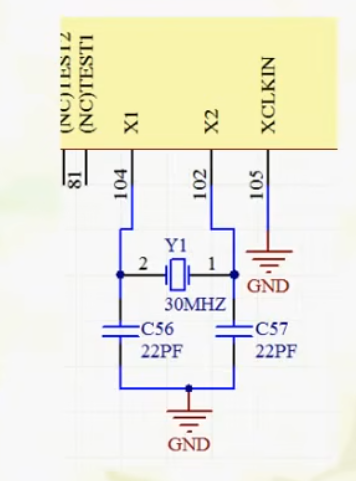

晶振电路

作用:提供稳定的时钟

晶振频率:一般为30MHz

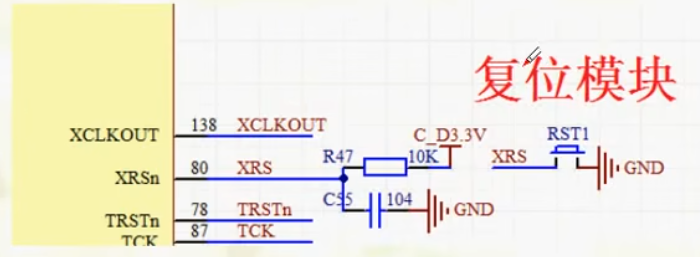

- 复位电路

使用JTag 烧录程序过程中不能复位,否则芯片可能锁死

-

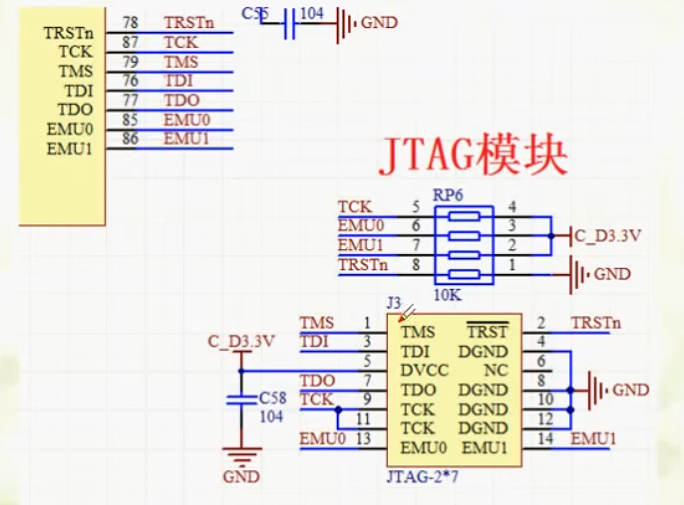

下载电路

F28335启动模式

存储器与寄存器

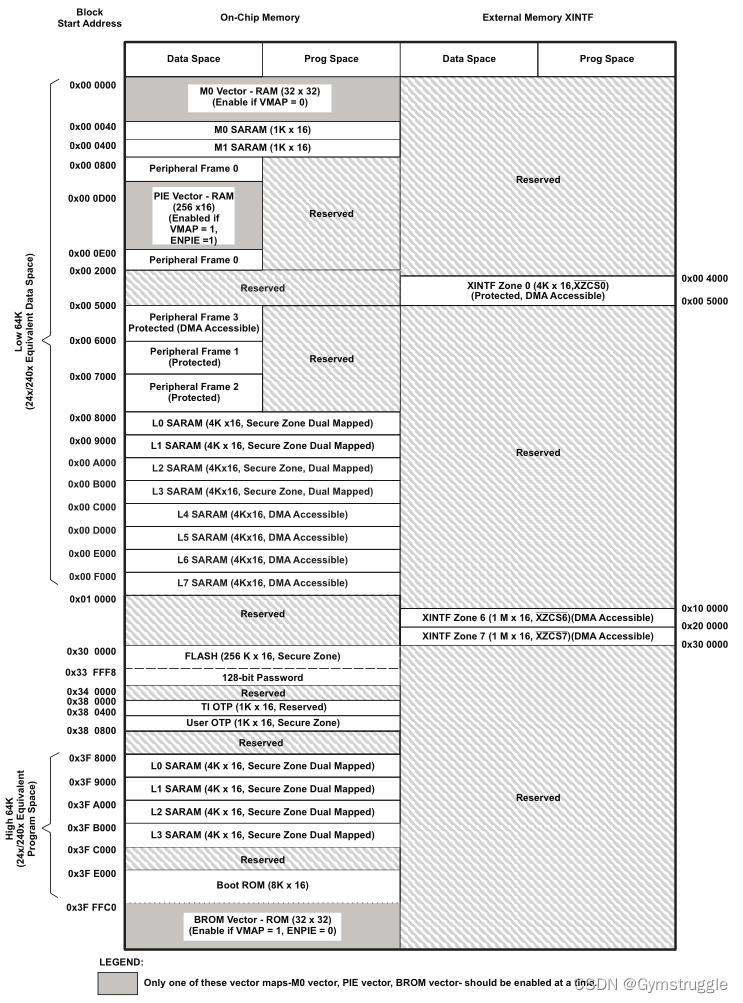

F28335芯片内部的存储器包括了256K×16位的FLASH(ROM),34K×16位的SARAM,8K×16 位的 BOOT ROM以及2K×16 位的 OPT ROM,采用统一寻址方式(程序、数据和 I/O 统一寻址),从而提高了存储空间的利用率。

存储器的这些存储空间都是实际存在的物理空间,为了统一管理以及便于访问这些空间,需要给这些空间分配地址,同样,为了统一访问片上的I/O和外设,都需要分配相应的地址。这就好似快递员将快递送到你家一样,你家就是存储空间,快递员是CPU,快递是数据,如果快递员不知道你家地址,那么快递就无法到家,因此有必要填写家庭地址。

存储器映射

为存储器的存储空间分配地址的行为就是存储器映射。查阅F28335的数据手册,可得F28335的存储器映射地址如图所示。

作如下几点说明:

-

空间大小的计算:比如M1的地址范围为0x800-0x400,则0x800-0x400=0x400=1024(dec)=1k,也就是说有1k的存储空间,而每个存储空间的大小为16位(这一点大家在之后编程的时候会发现,F28335操作的每一个寄存器大多数都是16位的),因此为1k×16。可能有人说该空间的大小为2k,这也是正确的,这是因为原则上认为1位就是1bit,而8位构成1字节(byte),1024个字节构成1kb,因此1k×16的大小为1k×2×8=2k×8;

-

FLASH的地址为0x30 0000-0x34 0000;BOOT ROM的地址为0x3F E000-0x3F FFC0;OPT ROM的地址为0x38 0000-0x38 0800;SARAM的地址就是0x00 0000-0x00 0800的M0、M1以及L0-L7;

-

外设帧 0/1/2/3,这 4 个空间也是存储空间同样分配了地址,但是它们只能是数据空间。设帧 1/2/3 空间是 Protected,表示这三个空间存放的寄存器不可以随便配置,若要对存放在 Protected 空间内的寄存器进行配置,要进行 EALLOW 声明,以 EDIS 结束声明,起到保护和警示作用。

寄存器映射

F28335片上集成了I/O以及多个外设,如SPI、SCI、EPWM、ECAP等,而操作F28335片上外设的本质就是在外设帧中相应存储空间写入或者读出数据,由于这一部分存储空间需要经常使用,人为操作频繁,因此正常编程时,需要频繁使用到这些存储空间的地址,而地址记忆时较为繁琐,因此可以为这些存储空间取人脑较为容易记忆的名字,取得名字我们称为Xx寄存器,而取名字的过程称为寄存器映射。这样,在编程时我们就可以在CCS中写这些寄存器的名字来替代原先的地址,也就能直接改变存储空间中的值,从而达到控制片上外设的作用。

从寄存器以及寄存器的映射概念可以看到,寄存器本质上就是存储器的中一些常用的存储空间。前面我说过,在CPU中也有一些寄存器,它们本质上也是存储空间,而在编写汇编语言时我们要经常用到CPU中的这些存储空间,因此为了书写的方便,我们也用同样的方法为这些存储空间编写名字,也就有了AX、BX、CX、DX、SI等。

下面我将以片上外设GPIO为例,说明在CCS中它是如何将GPIO下存储空间的地址进行映射。

先看下面这一条语句,这是一条非常简单的将GPIO68设置为高电平的语句。从该语句的结构上看,GpioDataRegs事实上是一个结构体,同时它也是映射后的寄存器。

GpioDataRegs.GPCSET.bit.GPIO68=1;

查看GpioDataRegs的说明,如下:

#ifdef __cplusplus

#pragma DATA_SECTION("GpioDataRegsFile")

#else

#pragma DATA_SECTION(GpioDataRegs,"GpioDataRegsFile");

#endif

volatile struct GPIO_DATA_REGS GpioDataRegs;

可以看到,GpioDataRegs是一个volatile struct GPIO_DATA_REGS类型的结构体。

(从目前看到的情况来说,GpioDataRegs就是一个volatile struct GPIO_DATA_REGS类型的结构体变量,而我们前面说对GPIO的操作实际上是对GPIO存储空间地址下的存储器进行数据写入或读出,我们既需要将GpioDataRegs当作一个寄存器,也需要对存储空间地址操作,显然根据寄存器映射的概念,我们需要将GpioDataRegs与存储空间地址结合在一起,也就是给存储空间地址取名为GpioDataRegs,这是“#pragma DATA_SECTION(GpioDataRegs,“GpioDataRegsFile”);”语句的作用。)

打开“DSP2833x_Headers_nonBIOS.cmd”文件,找到GpioDataRegsFile存在的语句如下:

GpioDataRegsFile : > GPIODAT PAGE = 1

可以看到,GpioDataRegsFile指向了GPIODAT,那么在该文件中找到GPIODAT存在的语句如下:

GPIODAT : origin = 0x006FC0, length = 0x000020 /* GPIO data registers */

可以看到,最终寄存器GpioDataRegs指向的地址为0x006FC0,长度为0x20,也就是32×16位。

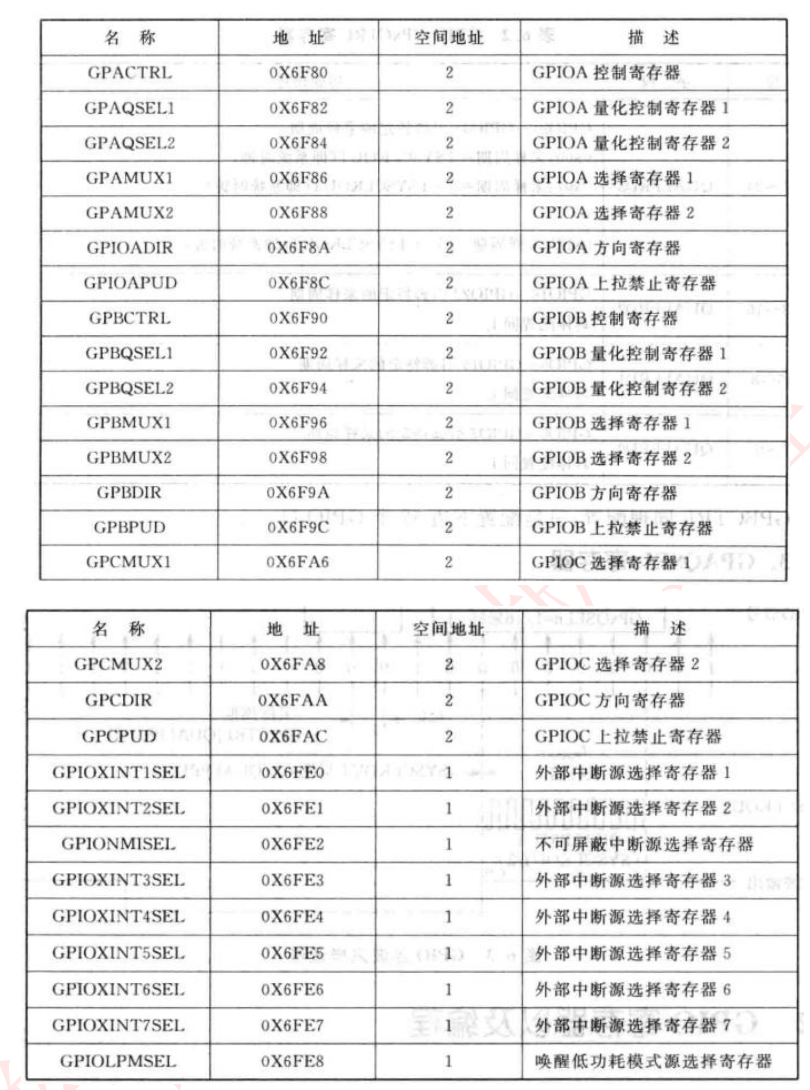

下面说明寄存器GpioDataRegs为什么指向的地址为0x006FC0,其长度又为什么是32×16位。首先从寄存器的名字可以看到,这是GPIO数据寄存器,查阅F28335的数据手册中GPIO数据寄存器地址映射情况如图所示。

可以看到,寄存器GpioDataRegs实际上是一个大类寄存器,其下包括了GPADAT-GPCTOGGLE等多个寄存器,而GPADAT寄存器的起始地址为0x6FC0,因此GpioDataRegs的起始地址也应该为0x006FC0。

回到“volatile struct GPIO_DATA_REGS GpioDataRegs;”语句中,点击GPIO_DATA_REGS可以看到该结构体的定义为:

struct GPIO_DATA_REGS {

union GPADAT_REG GPADAT; // GPIO Data Register (GPIO0 to 31)

union GPADAT_REG GPASET; // GPIO Data Set Register (GPIO0 to 31)

union GPADAT_REG GPACLEAR; // GPIO Data Clear Register (GPIO0 to 31)

union GPADAT_REG GPATOGGLE; // GPIO Data Toggle Register (GPIO0 to 31)

union GPBDAT_REG GPBDAT; // GPIO Data Register (GPIO32 to 63)

union GPBDAT_REG GPBSET; // GPIO Data Set Register (GPIO32 to 63)

union GPBDAT_REG GPBCLEAR; // GPIO Data Clear Register (GPIO32 to 63)

union GPBDAT_REG GPBTOGGLE; // GPIO Data Toggle Register (GPIO32 to 63)

union GPCDAT_REG GPCDAT; // GPIO Data Register (GPIO64 to 95)

union GPCDAT_REG GPCSET; // GPIO Data Set Register (GPIO64 to 95)

union GPCDAT_REG GPCCLEAR; // GPIO Data Clear Register (GPIO64 to 95)

union GPCDAT_REG GPCTOGGLE; // GPIO Data Toggle Register (GPIO64 to 95)

Uint16 rsvd1[8];

};

总结

- F28335的内核CPU与存储器是相互独立的;

- 寄存器与存储器本质是都是具体存在物理存储空间;

- 给存储器的存储空间分配地址的过程称为存储器映射;

- 一些存储空间需要经常操作,而直接操作地址的出错率较大,因此可以将存储空间的地址取人类容易记忆的名字,该过程称为寄存器映射,取得名字(指向存储空间的地址)称为寄存器。

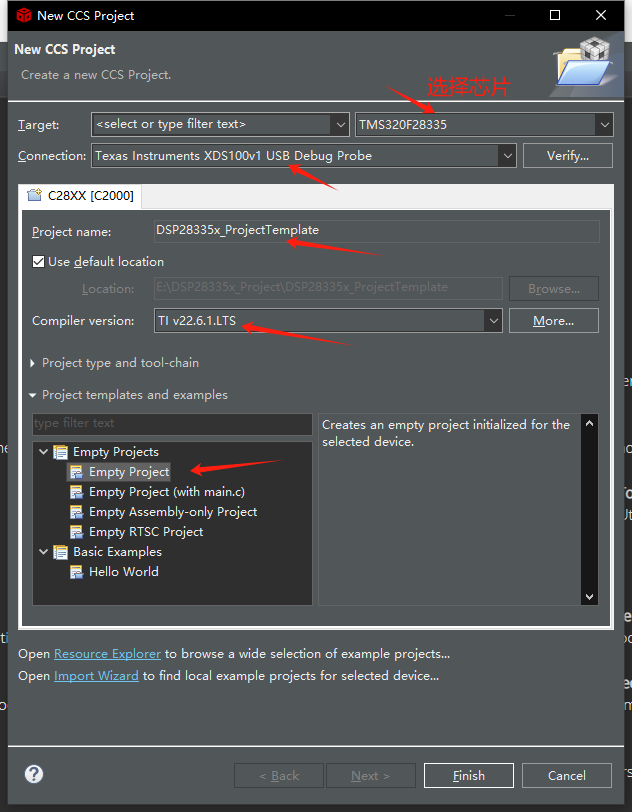

创建工程模版

一个完整的基础工程有哪些文件所构成呢?

①首先需要仿真调试或者flash烧写所需的.cmd文件和DSP的BIOS或nonBI0S .cmd文件。

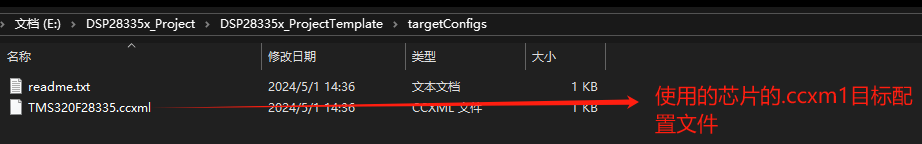

②其次需要我们使用的芯片的.ccxm1目标配置文件。

③芯片内核及外设.c源文件,比如DSP2833x Gpio.c、DSP2833x PieCtrl.c等。

④芯片内核及外设.h头文件,比如DSP2833xGpio.h、DSP2833x PieCtrl.h等。

⑤DSP .1ib库文件,常用的如IQmath.1ib等

- 创建工程

- 在工程文件夹中创建DSP2833x_Libraries添加工程所必须的文件

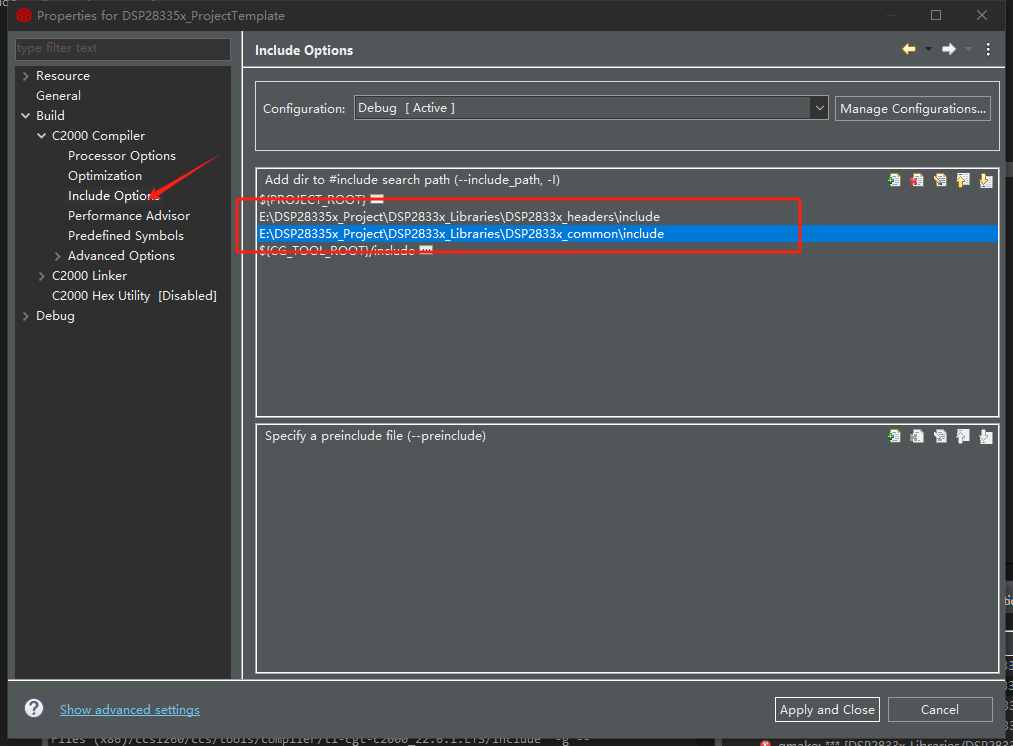

- 进入属性页,添加头文件的包含路径

F28335时钟及控制系统

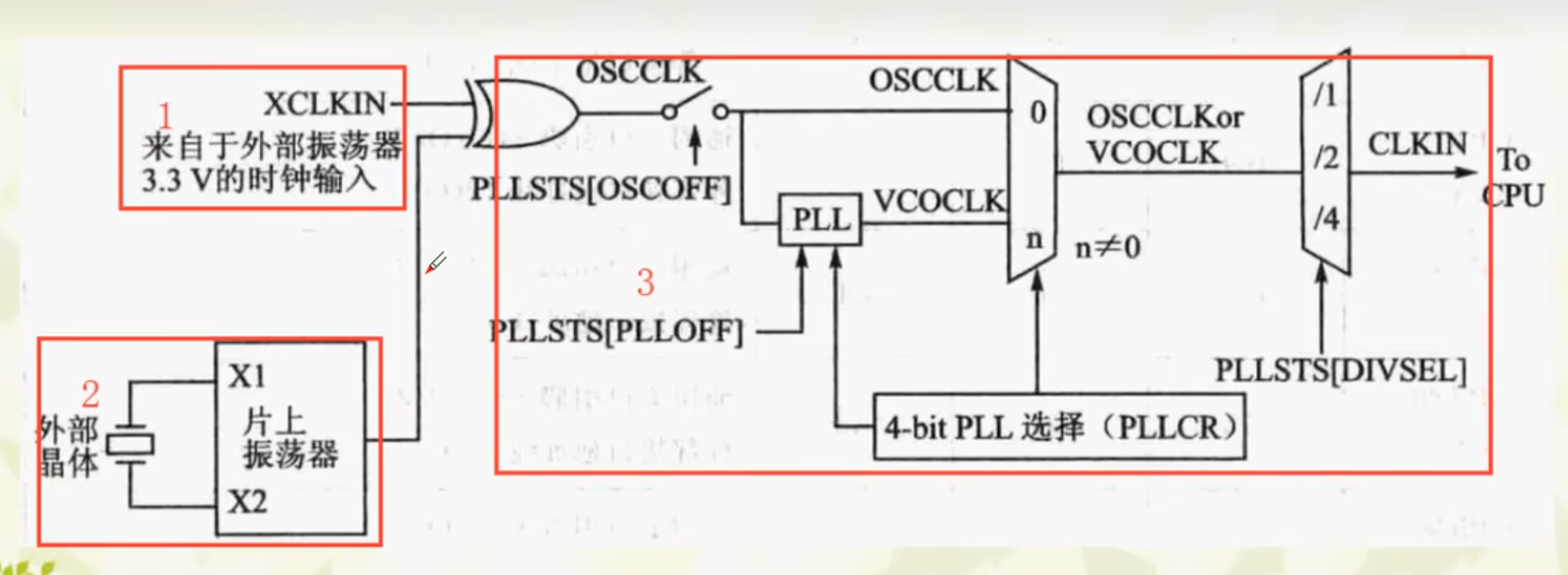

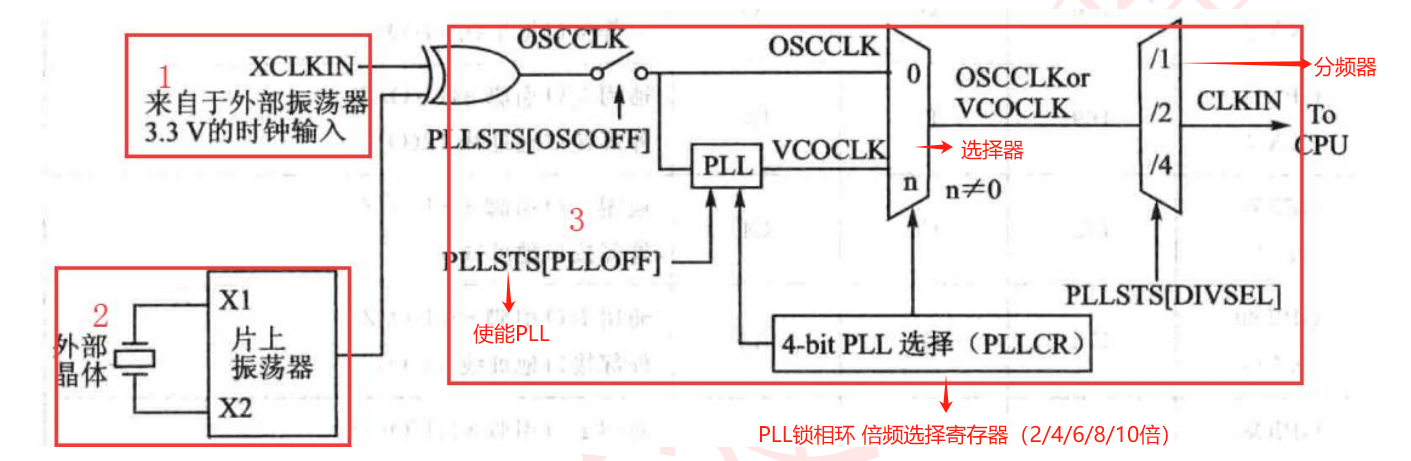

外部时钟

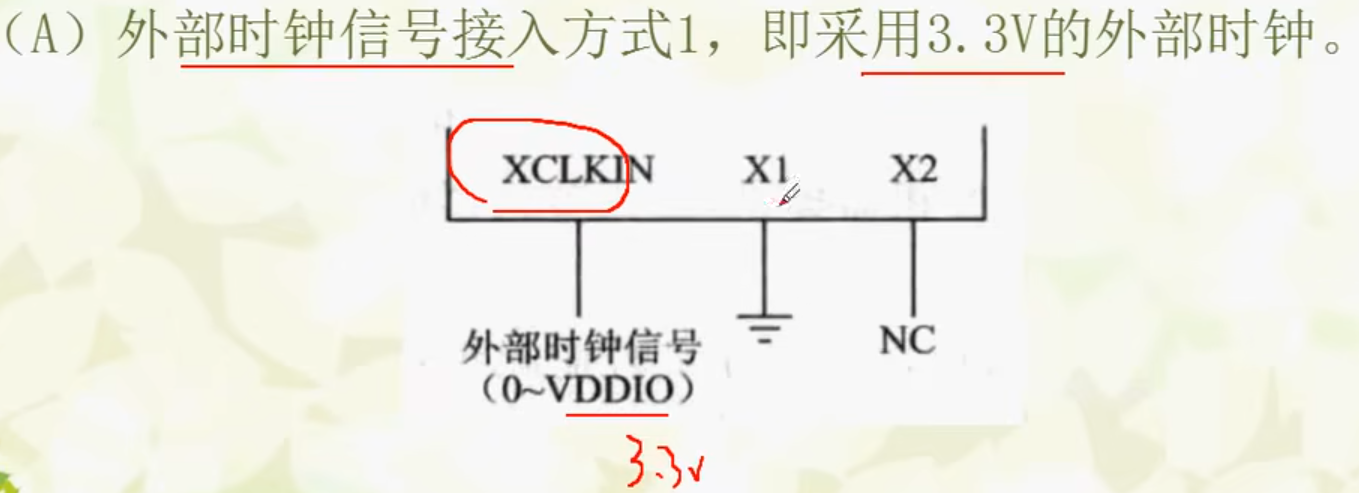

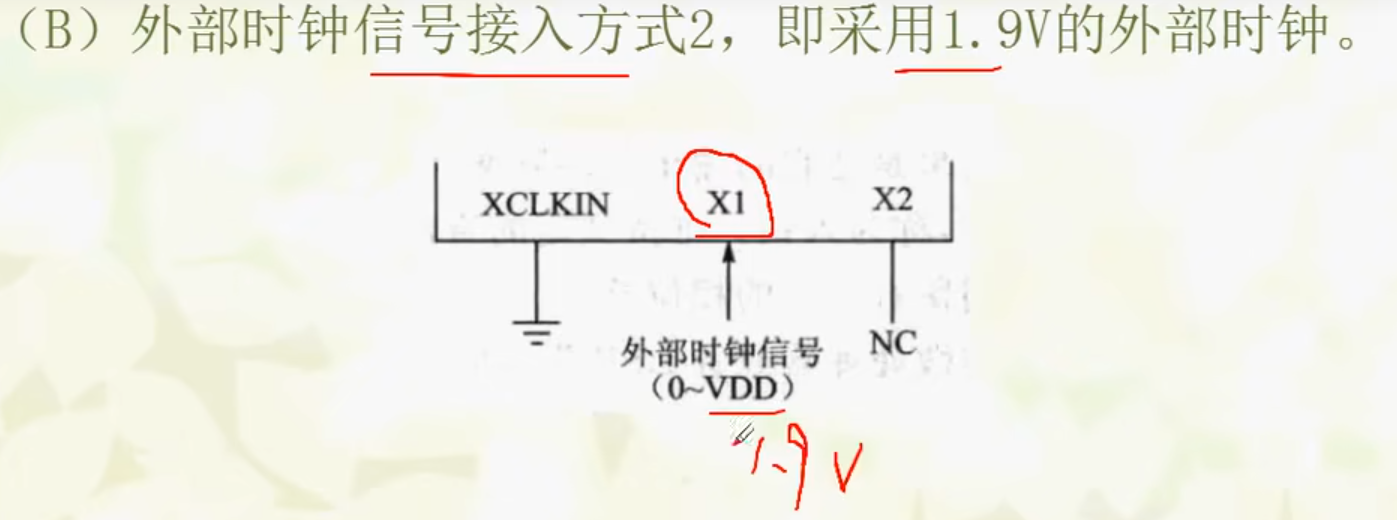

外部时钟源信号接入方法有2种,分别针对的是电压为3.3V的外部时钟和1.9V的外部时钟。

内部时钟

在X1和X2引脚之间介入外部晶振,晶振频率:30MHz。通过倍频、分频达到系统最大工作频率150MHz。

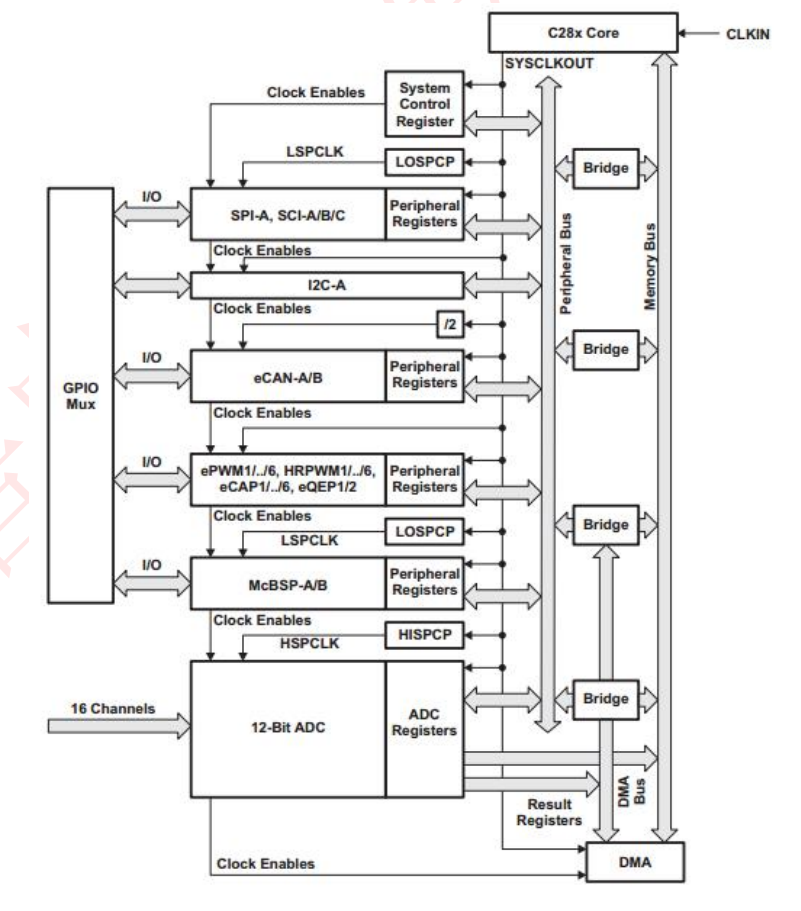

DSP 除了提供基本的锁相环电路外,还可以根据处理器内部外设单元的工作要求配置需要的时钟信号。处理器还将集成的外设分成高速和低速两种,可以方便的设置不同模块的工作频率,从而提高处理器的灵活性和可靠性。

- C28X 内核时钟输出通过 LOSPCP 低速时钟寄存器设置预分频,可设置成低速时钟信号LSPCLK,SPI、I2C、MCBSP 这些串口通信协议都使用低速时钟信号。

- 通过 HISPCP 高速时钟寄存器设置预分频,可设置成高速时钟信号 HSPCLK ,A/D 模块采用的是高速时钟信号,方便灵活设置 A/D 采样率。

- 通 过 1/2 分频给了 eCAN 模块。

- 直接输出给了系统控制寄存器模块、DMA 模块、EPWM 模块、ECAP 模块、EQEP 模块这些高速外设模块。

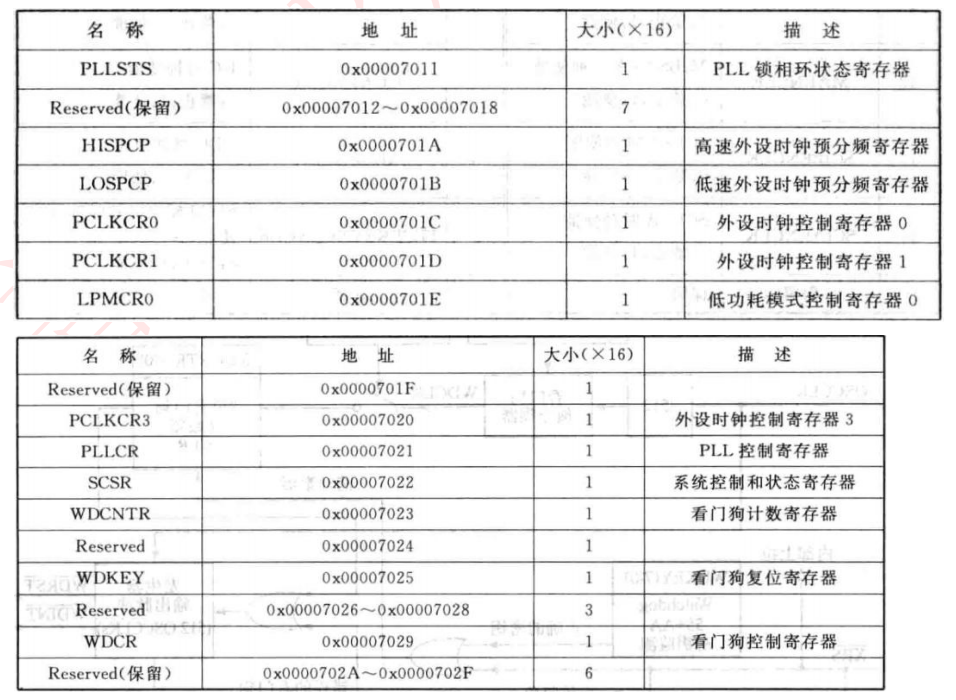

时钟单元常用寄存器

自定义系统时钟

void InitSysCtrl(void)

{

// Disable the watchdog

DisableDog();

// Initialize the PLL control: PLLCR and DIVSEL

// DSP28_PLLCR and DSP28_DIVSEL are defined in DSP2833x_Examples.h

InitPll(DSP28_PLLCR,DSP28_DIVSEL);//修改倍频系数、分频系数的值 实现自定义系统时钟

// Initialize the peripheral clocks

InitPeripheralClocks();

}

GPIO(通用输入输出口)

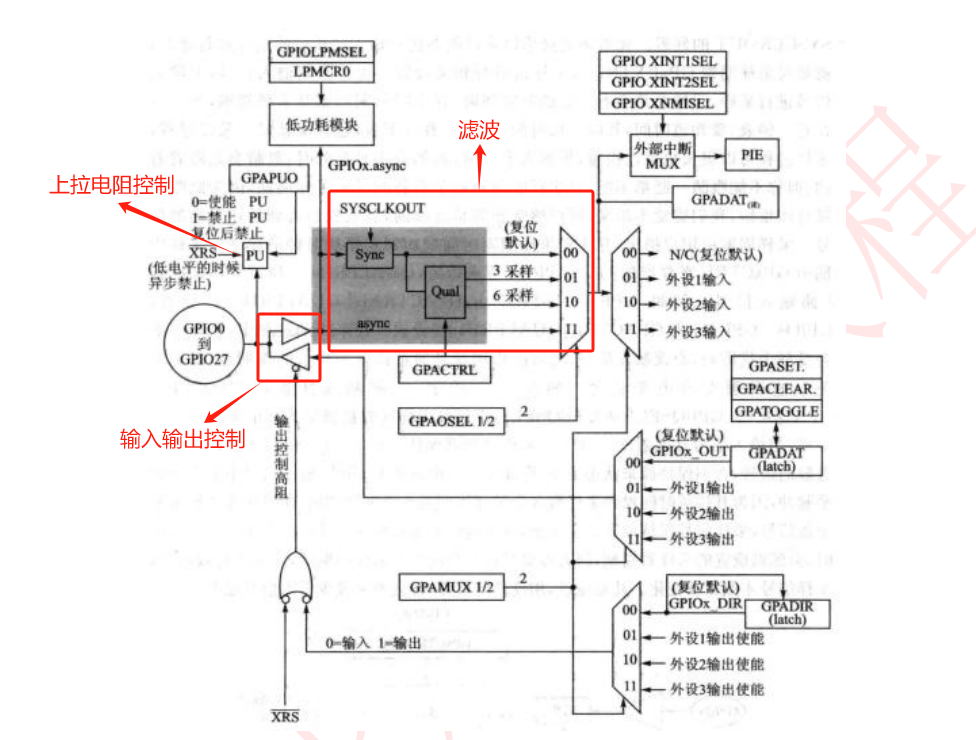

图中最左端 GPIO0-GPIO27 就是 F28335 芯片的引脚,其它部分都在芯片内部。

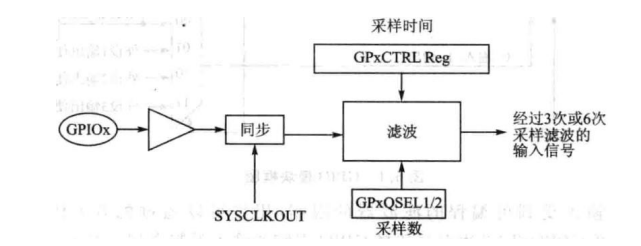

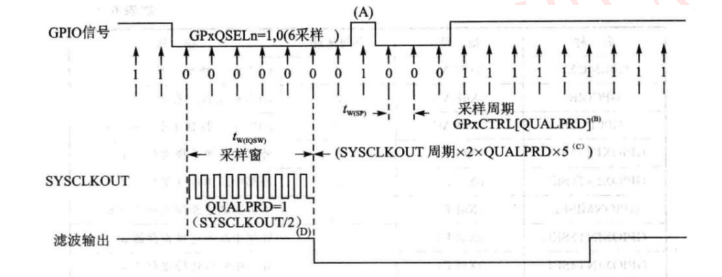

输入模式,在采样的过程中,信号可能会受到 干扰影响而误触发信号,滤波的作用就是通过设置采样窗的周期数,尽量避免一 些误触发的毛刺信号。如下图所示:

在限制选择器(GPAQSEL1、GPAQSEL2、GPBQSEL1 和 GPBQSEL2)中信号采样 次数被指定为 3 个采样或 6 个采样,当输入信号在经过 3 个或 6 个采样周期都保 持一致时,输入信号才被认为是个有效信号,否则保持原来的状态不变。

从图中可以看到 GPIO 输入信号中有 1 个较窄脉冲,因为其持续时间没到采 样数 3 个采样周期或 6 个采样周期,所以认为该脉冲是干扰信号,采样信号保持 原先状态不变,这样起到了滤波作用,但同时,采样信号在初始时会延迟设置的 采样数周期,因为需要经过 3 个或 6 个采样周期后才确认有效信号,采样信号才 做有效变化。凡是滤波,用硬件或软件都会或多或少引入信号延迟。

GPIO 相关寄存器

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 分享一个免费、快速、无限量使用的满血 DeepSeek R1 模型,支持深度思考和联网搜索!

· 使用C#创建一个MCP客户端

· 基于 Docker 搭建 FRP 内网穿透开源项目(很简单哒)

· ollama系列1:轻松3步本地部署deepseek,普通电脑可用

· 按钮权限的设计及实现