数字系统设计基础(1)

数字系统设计

3、时序逻辑电路

基本存储元件:锁存器和触发器。

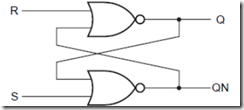

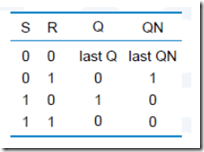

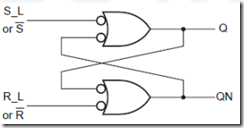

1. R-S锁存器(高电平输入置位清零):

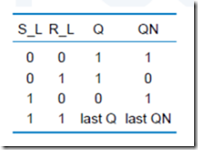

采用或非门实现的S-R锁存器。S-R锁存器具有两个输入信号R和S,两个输出信号Q和Qn,其中Qn是Q的反变量。如果S和R都是 0,则电路类似一个双稳态器件,Q=0 或者Q=1。R或S的改变使锁存器进入一个确定的状态。S=1,会输出Q变为1,称为置位S;R=1 会使输出Q=0,称为复位或者清零Q。如果S或者R无效(变为 0),锁存器将保持原来状态不变。

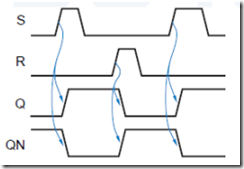

时序图中采用箭头表示因果关系:

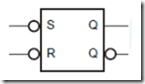

R-S锁存器电路符号:

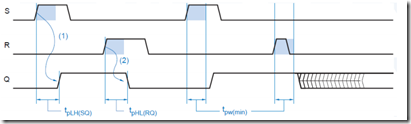

R-S锁存器的时序参数定义:从输入信号发生改变开始到输出信号响应此变化为止所需要的时间,定义为器件的传播延迟(propagation delay)。对于输入信号S和R,通常需要指定其最小脉冲宽度。如果输入信号的脉冲宽度小于最小脉冲宽度tpw(min),可能导致锁存器进入亚稳态。

2. R-S锁存器(低电平输入置位清零):

两种锁存器的差别:输出置位清零与输入电平的关系相反。

R-S锁存器(低电平输入置位清零)电路符号:

posted on 2011-10-30 16:22 youngdream 阅读(415) 评论(0) 编辑 收藏 举报