Design as You See FIT 阅读笔记

Design as You See FIT

作者及会议名称:DATE 2009, Daniel Holcomb, UC Berkeley

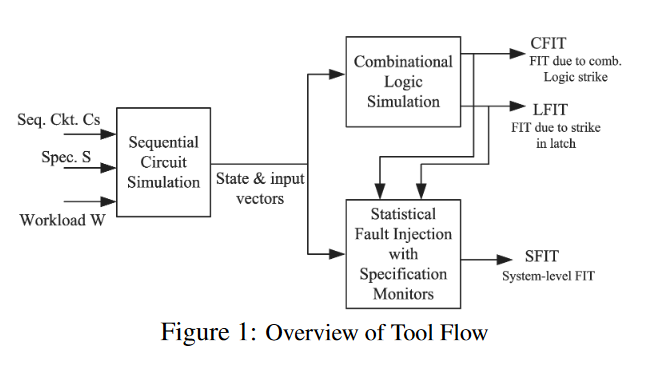

本文的重点贡献:提出了一种新方法计算时序电路发生系统级故障对输出产生影响的概率。

- CFIT: 计算组合单元的故障率,结合逻辑屏蔽、时序屏蔽和电气屏蔽。组合单元对整个电路故障率的贡献可由

FIT Rate和 该单元发生软错误导致系统级故障的概率 计算得到。 - SFIT: 计算时序单元的故障率,时序单元对整个电路故障率的贡献定义为 其

FIT Rate与 该单元发生信号翻转导致系统级故障的概率(\(P_{l_i}\)) 的乘积。 - 方法的输出是一个节点和锁存器的列表,根据它们对整个电路的 FIT 贡献排序

Overview of Approach

时序电路 \(C_s\) 形式化地建模为一个元组 \(<I, O, L, \delta, \rho, \theta>\)

- \(I \rightarrow Input Signals\)

- \(O \rightarrow OutputSignals\)

- $L \rightarrow $ 状态变量集合(锁存器)

- $\delta \rightarrow $ 确定锁存器下一状态的函数(\(2^I × 2^L \Rightarrow 2^L\))

- \(\rho \rightarrow OutputFunction\)

- \(\theta \rightarrow InitialState\)

三个输入

- 时序电路 \(C_s\)

- 电路规范 \(S\) (一组断言或者一个参考模型)

- \(Workload\ W\),电路在工作负载 W 上满足电路规范

输出

- 模拟过程中锁存器的状态集合

- 输入向量集合

Circuit-Level Soft Error Analysis

\[\begin{cases}

g_{i} \rightarrow struck\ gate \\

E \rightarrow set\ of\ flipped\ latches \\

CFIT_{g_{i} \rightarrow E}: 产生于g_{i},\ 被\ E\ 捕获的软错误

\end{cases} \\

\]

CFIT 依赖于电气、逻辑和时序掩盖,所以也依赖于电路的输入向量。

\[\begin{cases}

CFIT_{g_{i} \rightarrow E} = \frac{1}{|L_s|} \sum_{v \in L_{s}}{(CFIT_{g_{i \rightarrow E}}^v)} \qquad (2-1)\\

FIT_{l_{i}} = LFIT_{l_{i}} + \sum_{\forall g_{i}}{(CFIT_{g_{i} \rightarrow l_{i}})} \qquad (2-2)

\end{cases}

\]

- 公式2-1:某个逻辑门被粒子轰击产生瞬态脉冲被下游锁存器捕获的概率 \(\Leftrightarrow CFIT\)

- 公式2-2:某个锁存器自身被粒子轰击产生状态翻转 + 捕获上游故障瞬态脉冲的概率 \(\Leftrightarrow SFIT\)

粒子轰击用一个元组 (q, t) 表示,q 代表轰击产生的电荷量,t 代表轰击产生的时间(0表示时钟到来),\(\pi\) 代表从\(g_i\) 到 \(l_i\) 的敏化路径。

\[bool\ function: \quad N_{g_{i} \rightarrow l_{i}}^{\pi}{(q, t)}

\]

当给定输入向量时,\(g_{j}\) 被粒子轰击产生瞬态脉冲被下游锁存器锁存的概率。

\[CFIT_{g_{i} \rightarrow E}^{v}\ =\ \textstyle \int_{q = 0}^{\infty} \textstyle \int_{t = 0}^{t_{cycle}} {R(q, t) * N_{g_i \rightarrow E}^{v} {(q, t)} dtdq}

\]

- \(R(q, t)\): 粒子轰击逻辑门产生电荷量为q,产生时间为t 的瞬态脉冲的概率

- 粒子轰击逻辑门产生软错误的两个关键因素:引起信号翻转所需要的电荷量;该门产生大于此电荷量的概率。这两个因素都依赖于门的输入状态。

Pre-characterizing gates

收集到的电荷要产生error,它必须要能够对电容充电以产生和传播电压毛刺。

\[I(t) \propto \frac{1}{\tau} \sqrt{\frac{t}{\tau}}\ exp(\frac{-t}{\tau})

\]

Path-Based Analysis

基于一个前提:路径不会显著衰减毛刺,逻辑门的 FIT 只依赖于它的输入、负载电容和敏化路径延迟。

\[N_{g_{i} \rightarrow l_{i}}^{\pi} {(q, t)} = \hat{N}_{g}^{s} {(q, t - d_{\pi})}

\]

- \(\pi: g_{i} \rightarrow l_{i} \text{的一条敏化路径}\)

- \(s: \text{Input state}\)

- \(\hat{N}: \text{pre-characterized gate}\)

BFIT Implementation

整体设计:BFIT工具读入一个网表和预表征的门库(gate library),从网表中创建DAG(有向无环图),最后通过C++模型输出一个可执行的仿真程序。

- 输入向量:从相同电路的时序仿真采样得到

- FIT:计算所有输入向量得到的 FIT,然后取均值

- 每个输入向量经过3个步骤处理:

- 电路状态变量采样值\(l \text{ from } L_{S}\),随机输入状态\(i \text{ to circuit inputs } I\),共同构成组合逻辑的输入向量。输入向量通过DAG传播。

- 一旦输入向量传播完毕,通过DAG的回溯确定每一条敏化路径的延迟。

- 对于电路中的每一个门,其敏化路径和终止锁存器列表已知,计算其 FIT。

Experiment Result

ISCAS'89 Benchmarks

本文做的一些前提假设:

- 假设每个锁存器都已经被加固了,即不会由于粒子轰击直接导致锁存器翻转 \(\Leftrightarrow LFIT = 0\)

- 假设系统故障是由一个或多个锁存器捕获任一错误引起的,即锁存器捕获的任何错误信号都会导致系统错误 \(\Leftrightarrow P_{l_{i}} = 1\)

总结

这篇文章本质上是在分析 gate cell 被粒子轰击产生瞬态脉冲被下游锁存器捕获的概率,而锁存器捕获到瞬态脉冲传播到输出的概率是没有分析的(默认所有捕获的瞬态脉冲都能传播到输出端,即\(P_{l_{i}} = 1\))。

使用这个方法可以得到时序电路中每个门和锁存器对整个电路软错误率的贡献。如果对于纯组合电路(把输出看成锁存器),就可以得到每个门的软错误率数据。