FPGA小例子

AND ---与门;OR --- 或门;INV --- 非门;NAND --- 与非门;NOR --- 或非门;XOR --- 异或门;XNOR ---同或门;MUX --- 数据选择器;

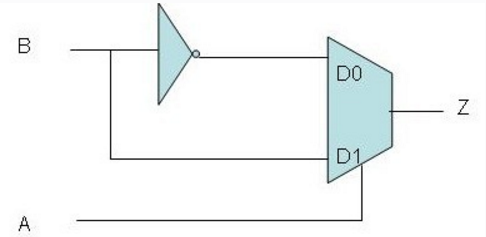

1.使用一个inv和一个二选一mux实现 异或。

module xor_rill ( input a, input b, output z ); assign z = a?(~b):b; endmodule

2. 三态门(常用于inout端口)。

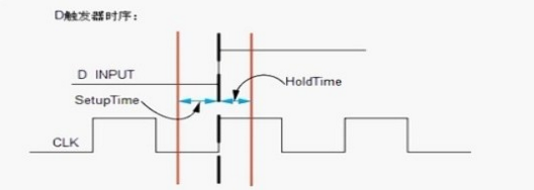

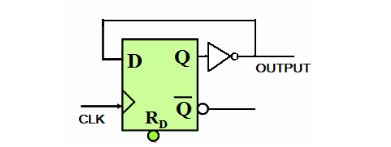

3. 用波形表示D触发器的功能

4. 亚稳态

4.1 何为亚稳态

(1)在时钟上升沿时,D在发生变化,如果D input输出为1则 ;

;

(2)在时钟上升沿时,D在发生变化,如果D input输出为0则 ;

;

(3)在时钟上升沿时,D在发生变化,在中间思考跳转很久,但不知道Dinput跳到0还是1(此状态出现概率非常低,但会出现)到下一个时钟还没有思考好是0还是1,没有出现稳定状态,这就是亚稳态  ;

;

4.2 危害 :会导致挂死,除了复位,完全不能工作。

4.3 什么时候会出现

(1)时序不满足

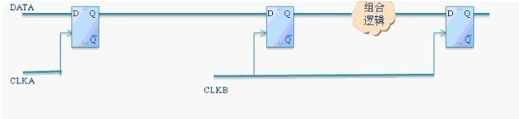

(2)异步接口或跨时钟域信号

4.4如何解决

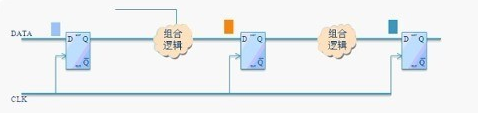

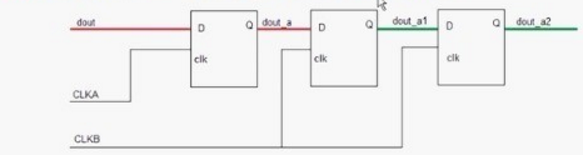

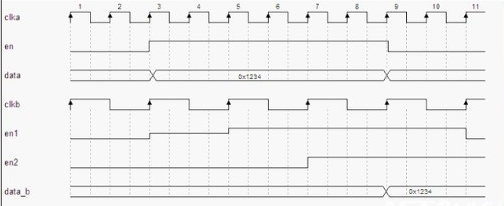

(1)单比特信号

(2)多比特信号

(3)多比特,但数据流小,用fifo不划算,使用使能信号

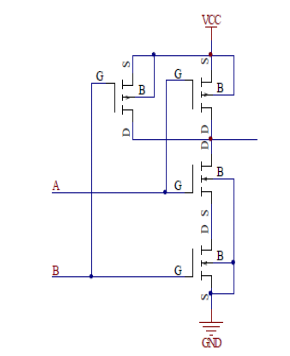

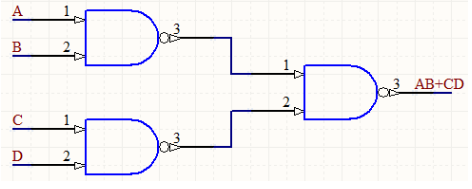

5. 用逻辑门和CMOS电路实现 ab + cd

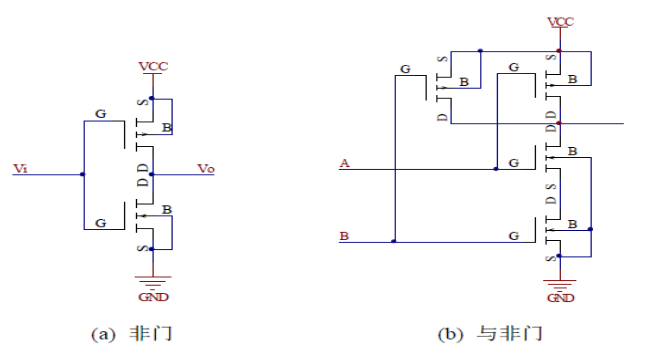

(1)首先给出CMOS构成的与非门电路

(2)用与非门实现逻辑ab+cd

这里化简的时候用到了反演律~(a&b) = ~a | ~b;

6. 给了reg的setup,hold时间,求中间组合逻辑的delay范围

假设时钟周期为period,则:

Delay < period - setup – hold

7. 用 D 触发器实现 2 倍分频的逻辑电路

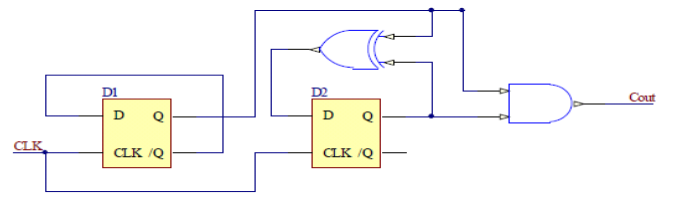

8.用D触发器做个4进制的计数器

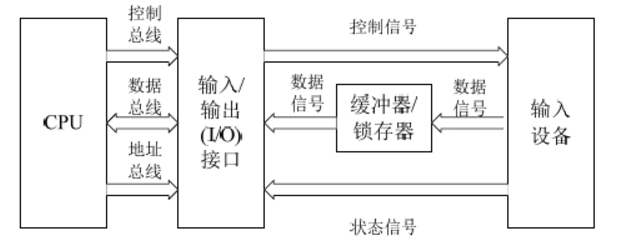

9.请画出微机接口电路中,典型的输入设备与微机接口逻辑示意图 (数据接口、控制接口、锁存器 /缓冲器)

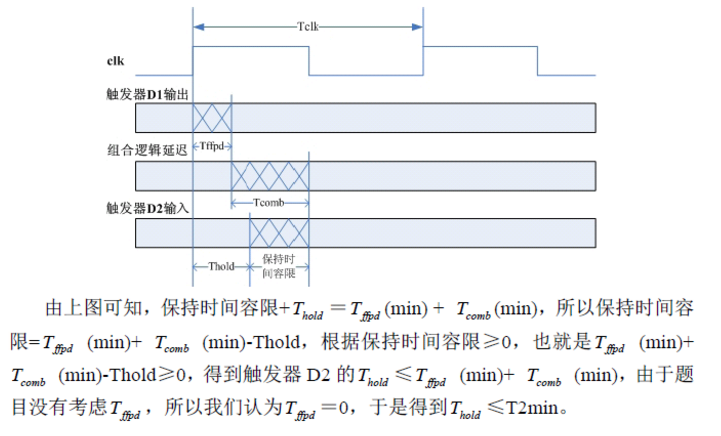

10. 时钟周期为 T,触发器 D1 的建立时间最大为 T1max,最小为 T1min。组合逻 辑电路最大延迟为 T2max,最小为 T2min。问,触发器 D2 的建立时间 T3 和保 持时间 T4 应满足什么条件

11. 给出某个一般时序电路的图,有 Tsetup、Tdelay、 Tck->q,还有 clock 的 delay, 写出决定最大时钟的因素,同时给出表达式

T+Tclkdealy>Tsetup+Tco+Tdelay ;

12. 画出 CMOS 电路的晶体管级电路图,实现 Y=A*B+C(D+E)

带入非门和与非门:

13. 利用 4 选 1 数据选择器实现 F(x,y,z)=xz+yz’

14. 用逻辑门画出 D 触发器

15. A、 B、C、 D、E 进行投票,多数服从少数,输出是 F(也就是如果 A、B 、C、D 、E 中 1 的个数比 0 多,那么 F 输出为 1 ,否则 F 为 0) ,用与非门实现,输入 数目没有限制

记 A 赞成时 A=1,反对时 A=0 ;B 赞成时 A=1,反对时 B=0 ;C、 D、E 亦 是如此。由于共 5 人投票且少数服从多数,因此只要有三人投赞成票即可,其他人的投票结果并不需要考虑。基于以上分析,下图给出用与非门实现的电路:

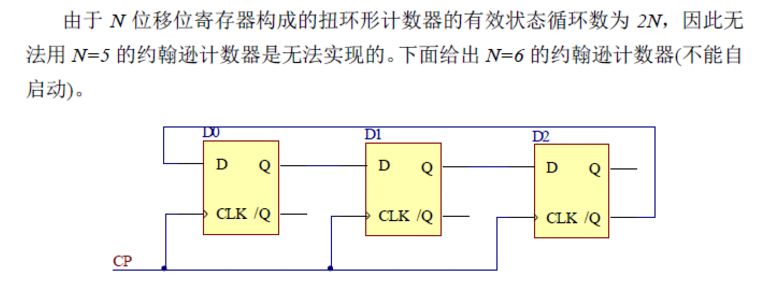

16. 实现 N 位 Johnson Counter,N=5

浙公网安备 33010602011771号

浙公网安备 33010602011771号