基于FPGA的HDMI显示设计(三)

10月10日 ~ 20日期间实习,令我万万没想到的是实习题目是 “便携式高清电视显示屏测试系统原型设计” 也就是 “基于FPGA的视频显示”。

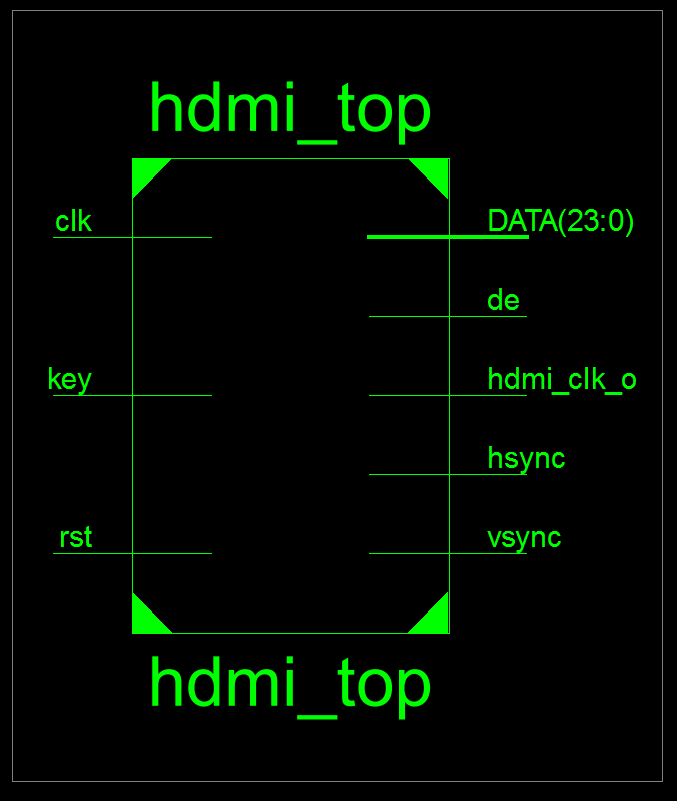

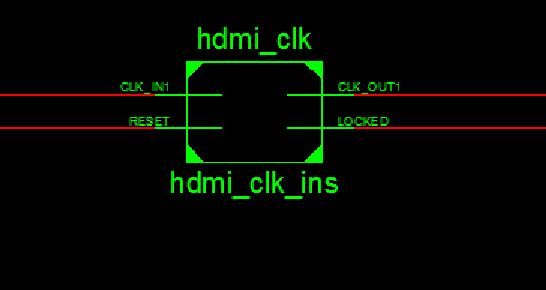

实习要求用 HDMI 接口显示,其实和VGA显示差不多的就多了两个引脚而已(de 和 hdmi_clk_o)。如下图:

虽然感觉做这个没什么意思了,但多多少少还是有一点收获的。

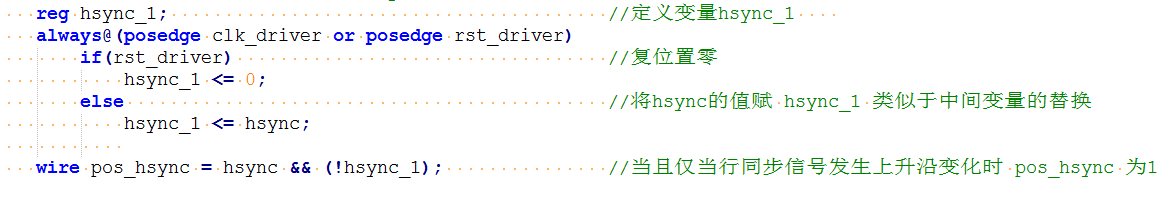

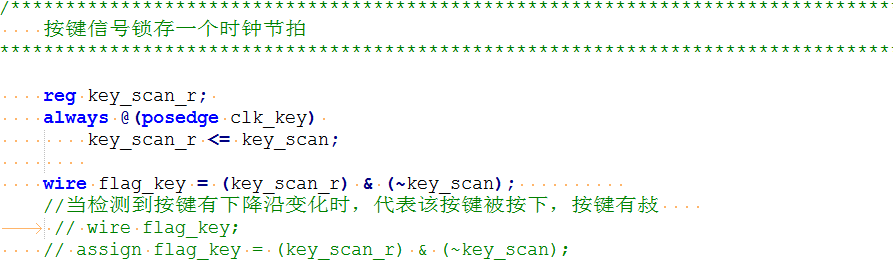

(1)锁存一个时钟的数据用作判断

源代码片段例子1:

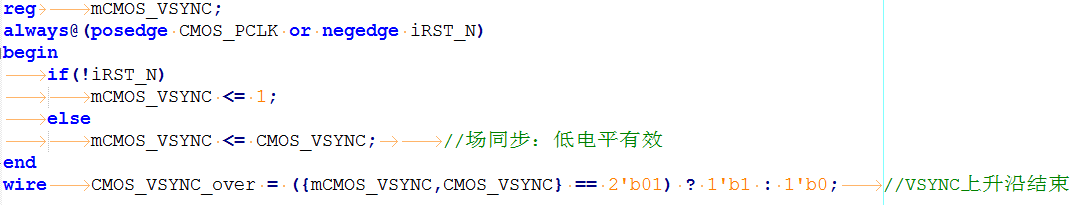

源代码片段例子2:

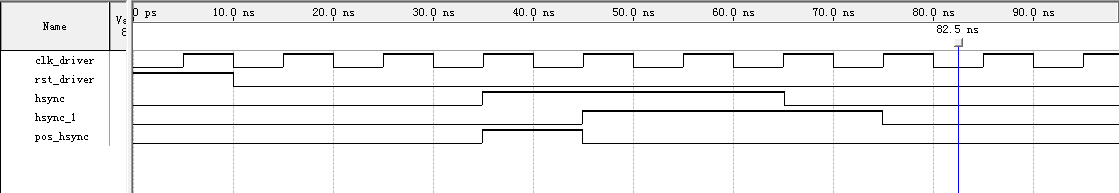

我在quartus ii 9.0上随便拉的波形:

原理: hsync_1 锁存了一个周期的下的 hsync 的数据,这样线网型变量 pos_hsync 就能表示出上升沿产生的一个周期变化。

启发:同理能写出下降沿有效的判断。

用处:用于判断,提高可靠性。

缺陷:有一定的局限性,原信号变化需要大于一个周期;其它。

例子:按键信号有效判断。

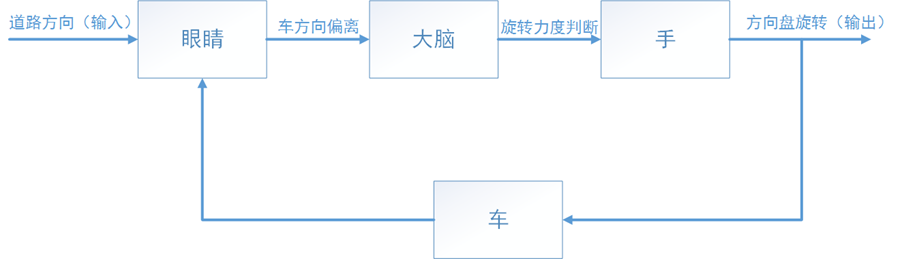

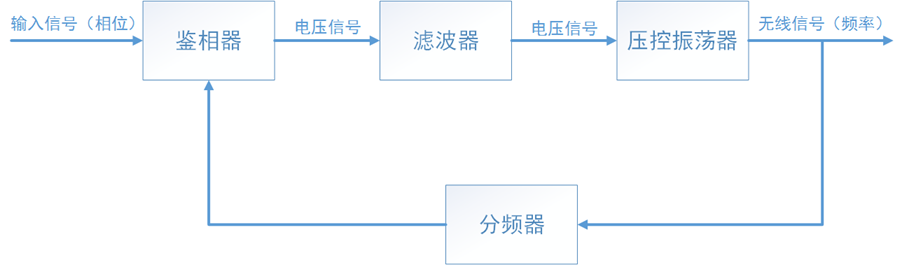

(2) 锁相环使用进一步认识

形象对比:

一般 IP 核生成的倍频 / 分频电路模块默认除了时钟输入引脚(CLK_IN1)和时钟输出引脚(CLK_OUT1),还有高电平复位的异步清零引脚(RESET)和高电平有效的相位/频率检测器的使能端(LOCKED)。

选择“LOCKED”,通过这个输出端口可以判断锁相环是否失锁,高电平表示正常。可以用 LOCKED 作为全局复位信号。如果其它模块是高电平复位,那么需要在 LOCKED 端加上一个反相器。(一般用 CLK_OUT1 作为全局时钟)

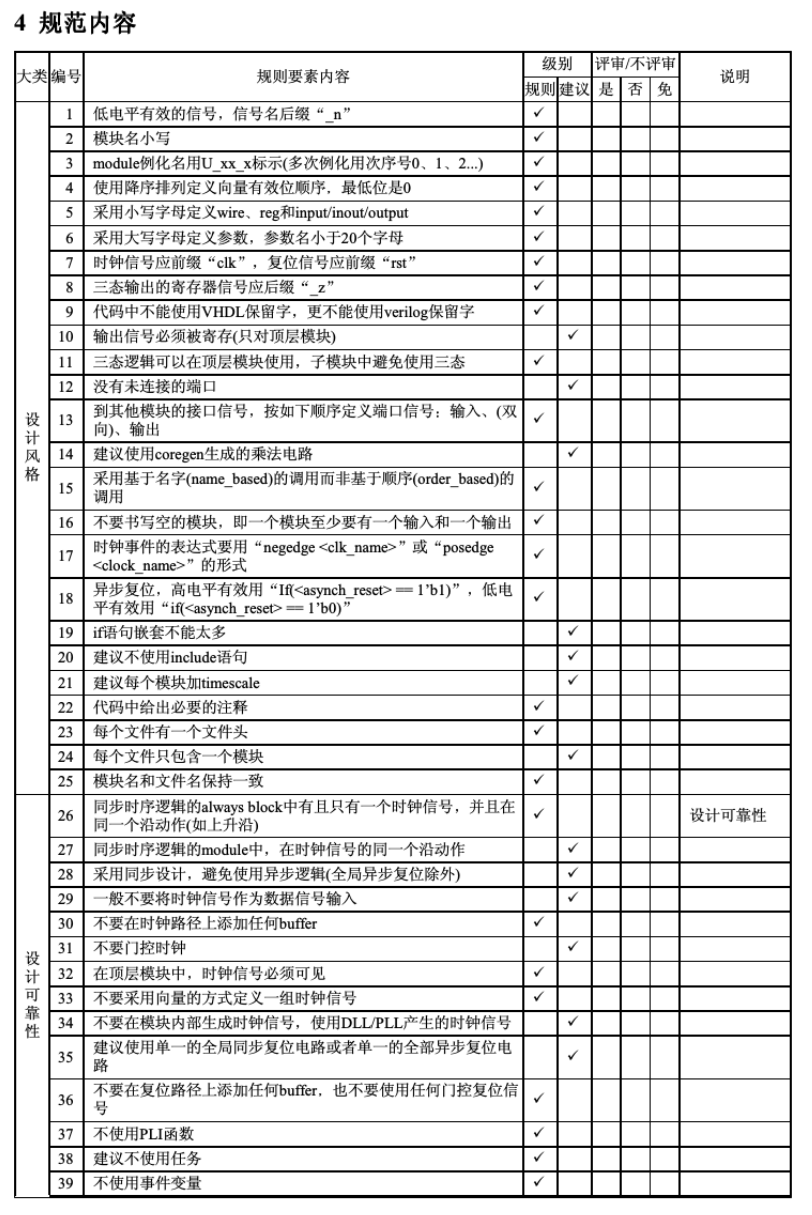

(3)Verilog HDL 编程规范

可以参看华为的 Verilog HDL 编程规范:

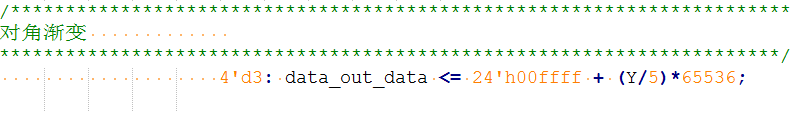

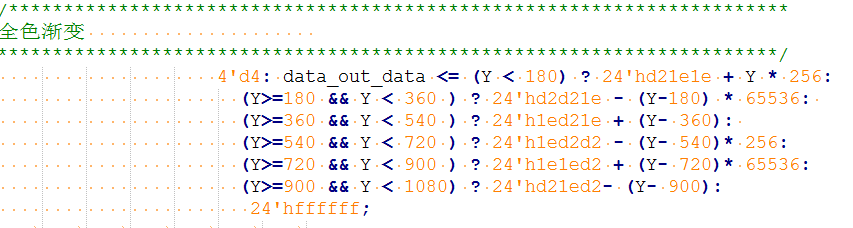

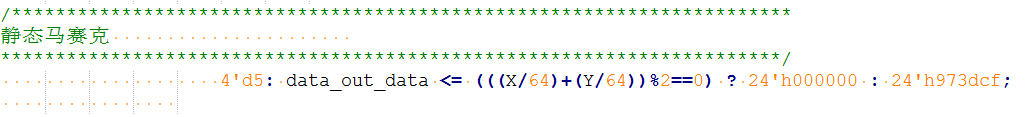

(4)算法认识

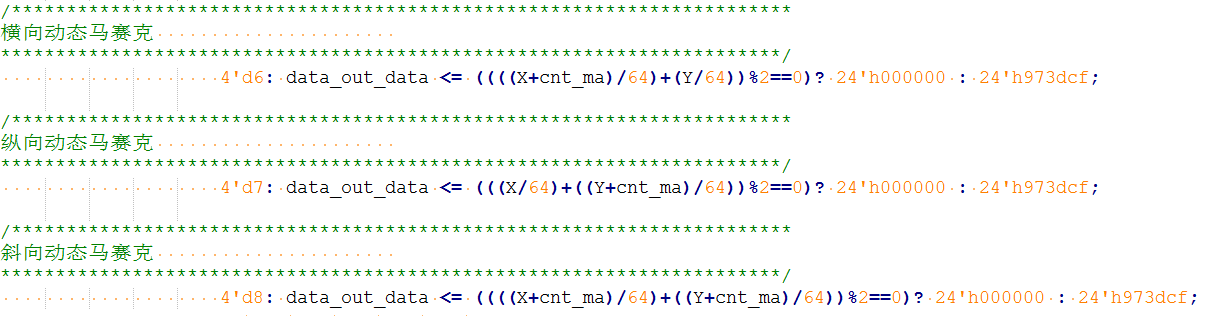

马赛克(棋盘格)这个对比第二篇的异或算法很相似。

(5)Xilinx (赛灵思)的 ISE 还是蛮好用的

嘿嘿嘿!

浙公网安备 33010602011771号

浙公网安备 33010602011771号