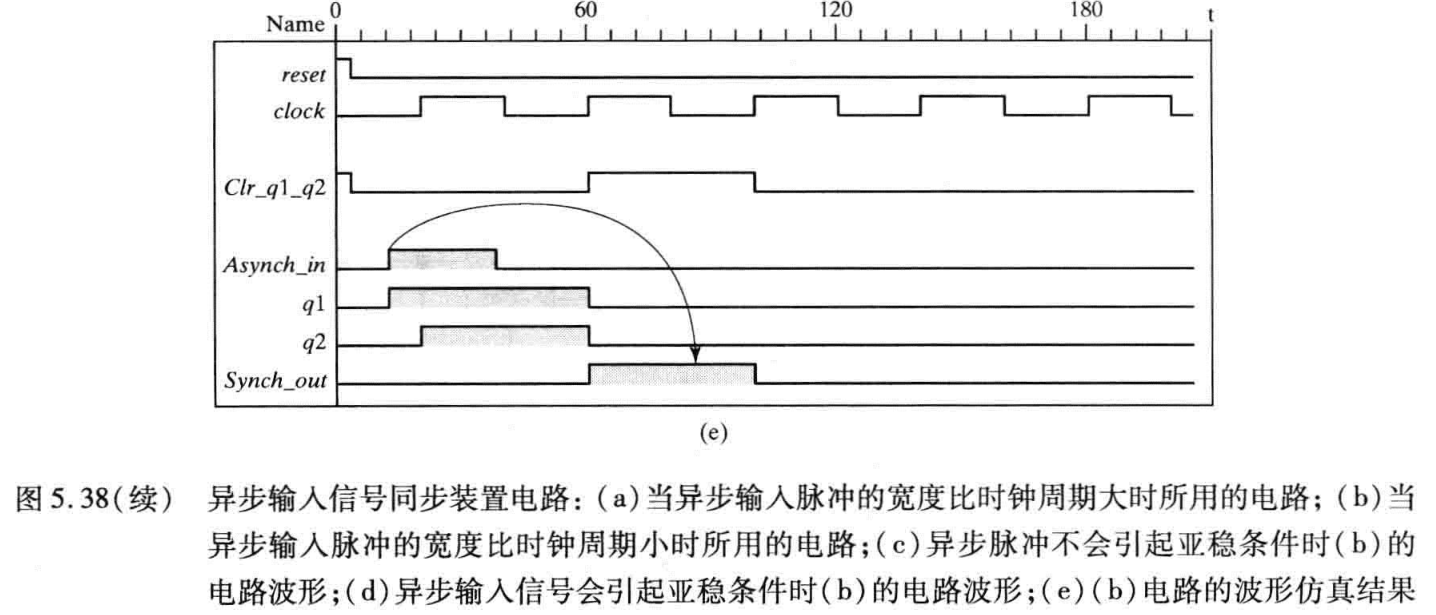

异步信号同步 - 小于时钟周期的窄脉冲信号同步

异步信号同步 - 小于时钟周期的窄脉冲信号同步

参考书籍

《Verilog HDL高级数字设计(第二版)_Michael D.Ciletti》 5.17节 用于异步信号的去抖开关、亚稳定性和同步装置

示例Verilog代码

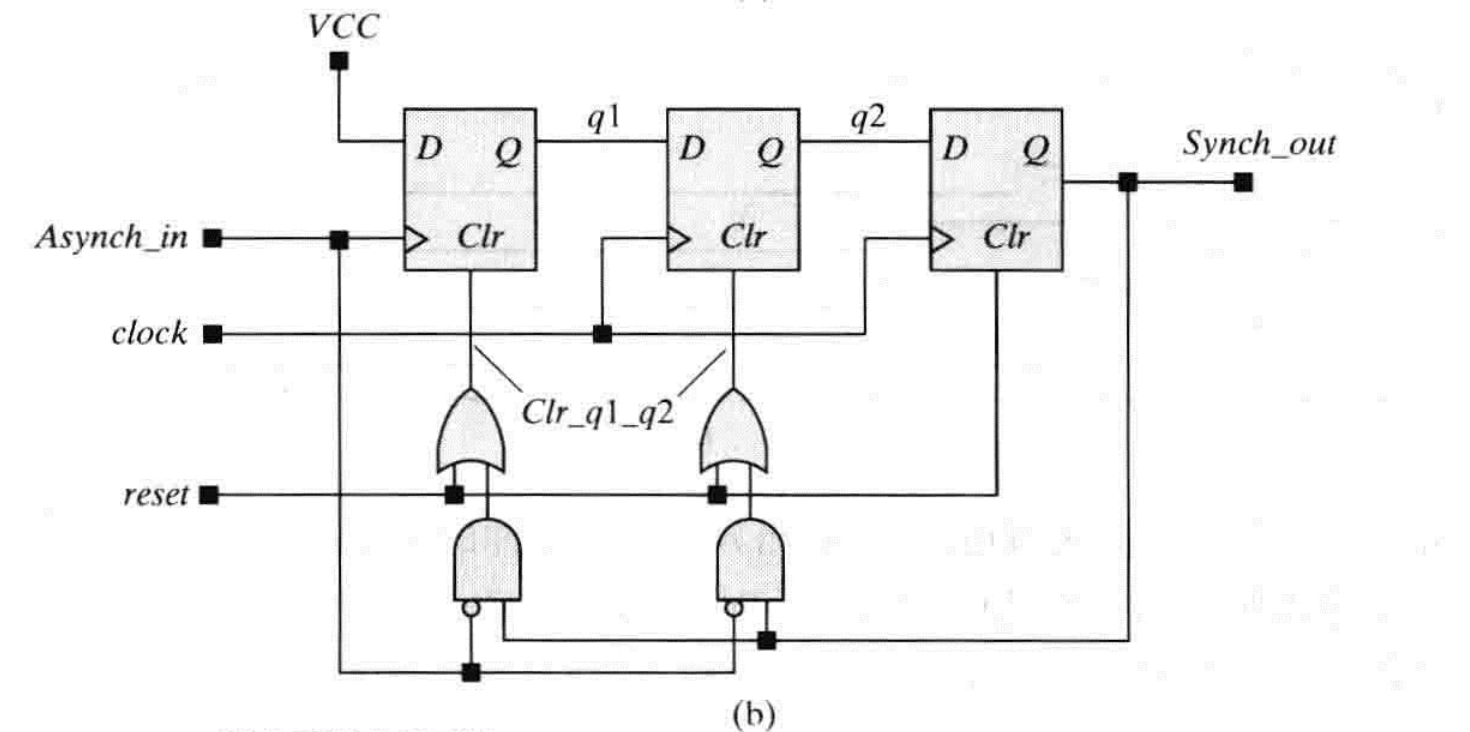

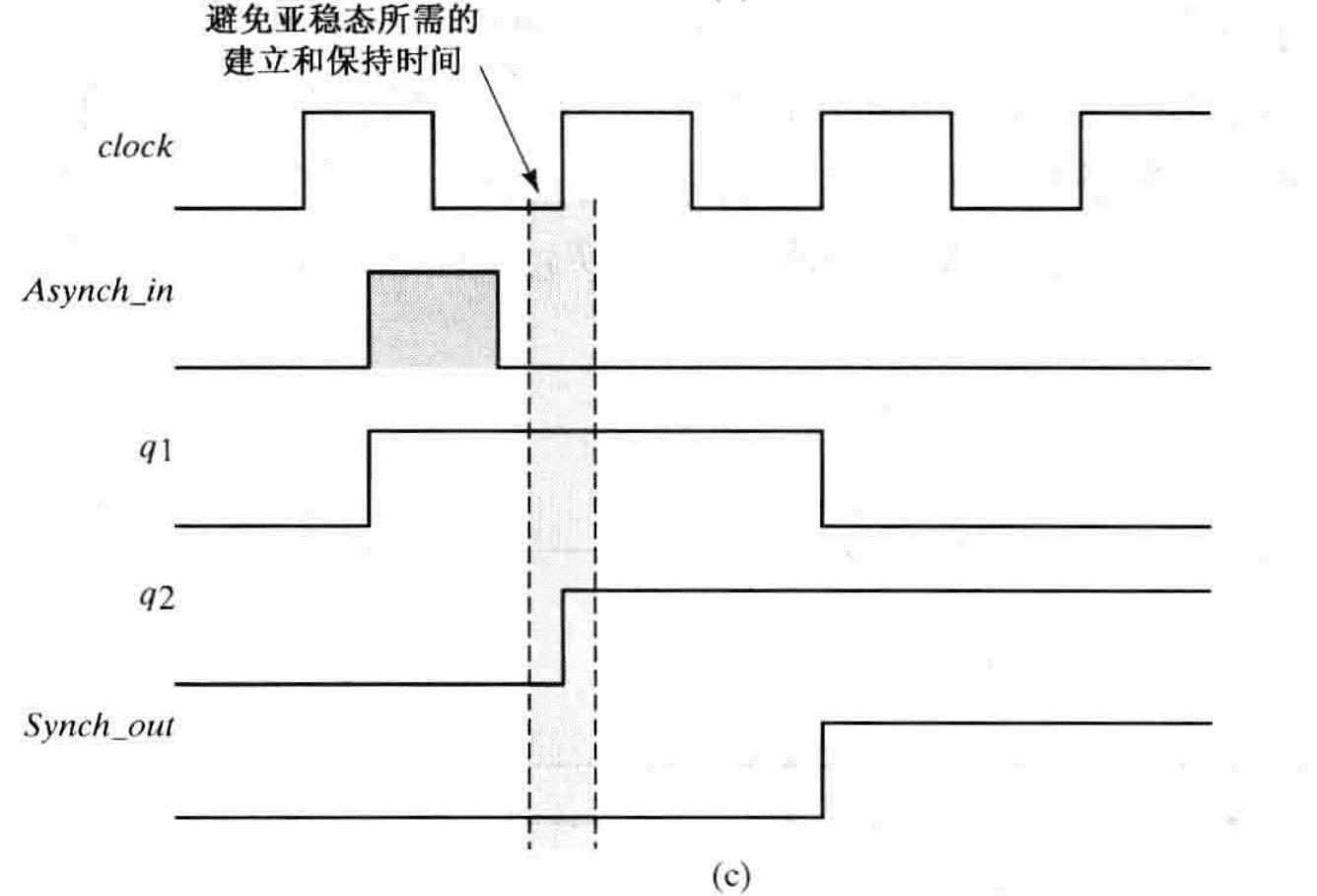

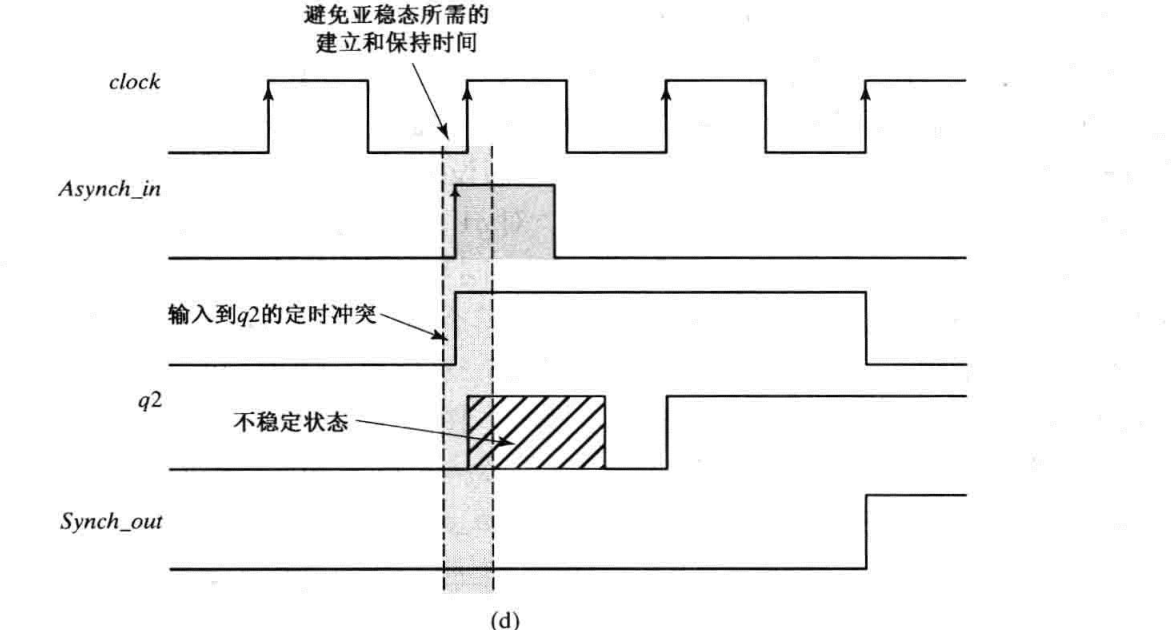

// 基本思路和打两拍一致,只不过加了一级触发器获取窄脉冲和反馈复位

module sync_narrow_pulse (

input clk ,

input rst_n ,

input asynch_in , // 一般为小于时钟周期的异步脉冲信号

// 如果大于一个时钟,输出可能不是一个周期

output wire synch_out

) ;

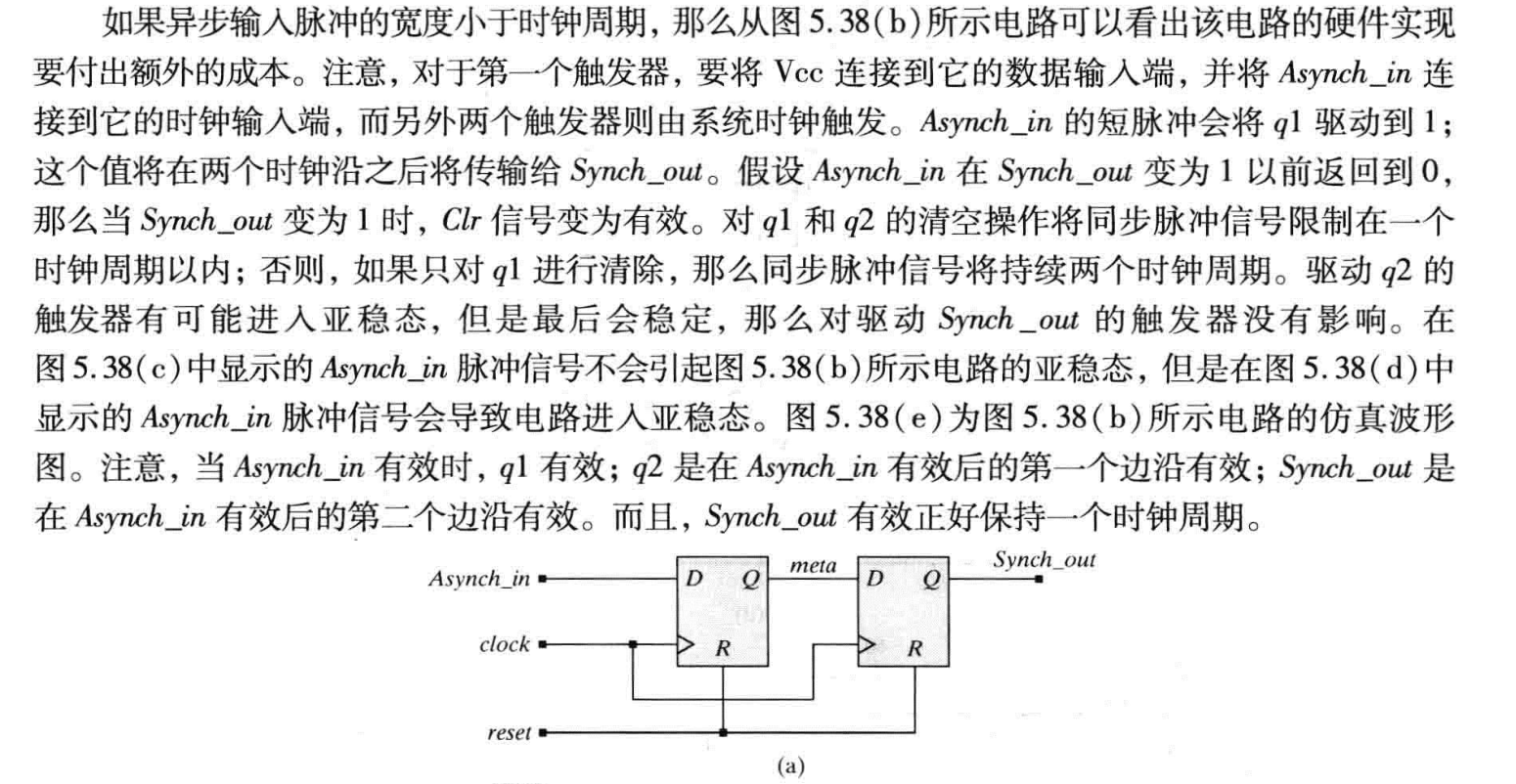

reg dff1 ; // 获取窄脉冲信号(narrow pulse)

reg dff2 ; // 消除亚稳态(metastable state)

reg dff3 ; // 稳定的信号输出

wire rst_dff1_dff2 ;

assign rst_dff1_dff2 = rst_n & (asynch_in | ~dff3) ;

// 用异步信号作为D触发器时钟获取窄脉冲信号

always @(posedge asynch_in or negedge rst_dff1_dff2)

if (rst_dff1_dff2 == 1'b0) dff1 <= 1'b0 ;

else dff1 <= 1'b1 ;

// 第一级同步器,注意为了最终得到一个脉冲则复位条件和dff1是相同的

always @(posedge clk or negedge rst_dff1_dff2)

if (rst_dff1_dff2 == 1'b0) dff2 <= 1'b0 ;

else dff2 <= dff1 ;

// 第二级同步器,此D触发器的输出是稳定信号

always @(posedge clk or negedge rst_n)

if (rst_n == 1'b0) dff3 <= 1'b0 ;

else dff3 <= dff2 ;

assign synch_out = dff3 ;

endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号