STM32速成9.3更新-感想:寄存器为王,配置好寄存器就完事了

第一阶段:预备

1寄存器映射:将外设映射在寄存器上,通过对寄存器修改来操作外设。STM32最高支持4G的地址,分为了8个BLOCK,每个BLOCK大小是512M,其中片上外设部分在当前学习阶段较为重要 ,APB1、APB2、AHB1、AHB2是速度不同的总线, GPIO都在AHB1上。

2.对某IO进行操作:1)直接写寄存器/2)寄存器别名操作/3)将*也定义在别名内。

3.寄存器地址在中文参考手册的2.2

4.相对地址与绝对地址:绝对地址就是寄存器的地址,而相对地址就是相对某个基地址的偏移量,例如总线基地址、GPIO基地址、具体寄存器地址。

5.使用结构体封装,访问寄存器更方便,对同类型的寄存器可以避免重复定义,节省工作时间。

6.结构体是库函数的雏形, 可以定义操作、寄存器。可提升程序可读性、方便修改程序。

7.固件库、Libraries存放库源码、Project存放工程模板、Utilities存放评估板例程。

8.固件库工程,目前最简单的方法就是复制一个工程再添加内容修改。

keil5 在空白处右键选择Go to xxx.h即可进入.h文件

第二阶段:LED灯与按键识别

1.LED灯为GPIO输出,按键识别GPIO输入;

2.使用时都先将寄存器配置好,再使用程序操作;

3.按键消抖有硬件消抖与软件消抖:硬件:电容;软件:延时。

第三阶段:位带操作

1.为了单独对某一IO操作而引入的概念,因32只可对32位寄存器操作,因此将单独位膨胀成32位地址。

2.计算公式 AliasAddr= =0x22000000+ (A-0x20000000)*32 +n*4 AliasAddr= =0x42000000+ (A‐0x40000000)*32 + n*4.

3.统一公式 AliasAddr= =(addr & 0xF0000000) + 0x02000000 + ((addr & 0x000FFFFF)<<5) +((BITNUM)<<2).

4.使用

#define GPIOH_ODR_ADDR (GPIOH_BASE+0x14)

#define BITBAND(addr,bitnum) (addr & 0xF0000000) + 0x02000000 + ((addr & 0x000FFFFF)<<5) +((bitnum)<<2)//位带别名区地址

#define MEM_ADDR(addr) (*(volatile unsigned long *)(addr))//地址立即数强制转换成指针, volatile 特征修饰符,确保本条指令不被优化。

#define BIT_ACTION(addr,bitnum) MEM_ADDR(BITBAND(addr,bitnum))//对指针操作

#define Phout(n) BIT_ACNTION BIT_ACTION(GPIOH_ADDR,bitnum)//输出

7.形参-主调函数与被调函数之间的关系,接收调用该函数时传递的参数;实参-调用时传递给函数的参数,实际的值。

第四阶段:启动文件(定制结构和指令时需要写启动文件)

1.启动文件,上电后启动的第一个文件。初始化堆栈指针、PC指针、系统时钟、_main

2.启动文件为汇编语言编写,注释时使用“;"注释起说明作用。

3.栈?局部变量、函数调用、函数形参的开销。

4.暂时略

第五阶段:RCC时钟控制RCC_PLLCFGR

1. HSE高速外部时钟、有源1-50M、无源4-26M(HSEON打开-位16)

2. HSI高速内部时钟,16M.HSE故障自动切换到HSI()

3.PLLCLK锁相环时钟,HSE倍频后180MHz。VCO在1-2MHz之间,建议2MHz,限制PLL抖动。

4.系统时钟,SYSCLK,最高180M,来源于HSI、HSE、PLLCLK

5.HCLK时钟,AHB高速总线时钟,最高180M,位AHB外设提供时钟,内系统定时器提供时钟,内核提供时钟(CPU时钟)。

6.过程 配置HSE、配置分频因子M、配置倍频因子N、分频因子P、系统时钟选择、AHB分频器、得到HCLK、再分频得到APB时钟。

7.例程中的HCLK---180M、APB1---90M、APB2---45M。

8、其余时钟1)RTC时钟,实时时钟,外部32.768KHz、HSE_RTC(HSE分频1Mmax)、内部32Khz时钟 (可直接用作看门狗时钟)

9.PLL48CK:48MHz,USB_FS\RANG\SDIO提供时钟。

10.I2S时钟:I2S时钟(内部或者外部)

11.以太网时钟(25-50MHz)、USB时钟(24---60MHz)

12.根据官方system_stm32f4xx.c中的时钟配置部分可以修改出自己的时钟配置模块。

第六阶段、中断概念

1.中断以前学过一些,简单说就是有事件打断当前的操作,而能不能打断当前的操作就需要引入优先级的概念,如果事件优先级比我高,那就打断当前操作,此外,如果打断了当前操作,去执行新的操作,在新操作执行完成后还要继续执行当前操作,因此又需要现场保护等。

2.中断事件向量表中包含了中断事件(87个)与系统异常(10个)的优先级,一共有87个。每个中断/异常服务程序都有一个对应的地址

3.中断向量地址可以存储器重映射,做偏移。

4.NVIC---嵌套向量中断控制器,内核外设,管理内核与片上所有外设的中断---core_cm4.h

5.ISER中断使能、ICER中断清楚、ISPR中断悬起、ICPR悬起清除、IABR有效位、IP优先级、STIR软件触发、

6.IPRX设置主优先级、次优先级,仍然一致时比较硬件编号(在向量表)。

7.外设的中断请求是通过寄存器产生中断请求,例如SPI传输完成,修改寄存器产生发送完成中断请求(类似发送完成标志位)

8.有了请求就需要配置请求优先级,仲裁模块程序,中断服务函数(函数名在启动函数已确定、如果名字错了在执行时会执行自带的程序,无限跳转;函数一般写在stm32f4xx_it.c)。

9总结:1、使能中断请求;2、配置中断优先级分组;3、配置NVIC寄存器;4、编写中断服务函数。

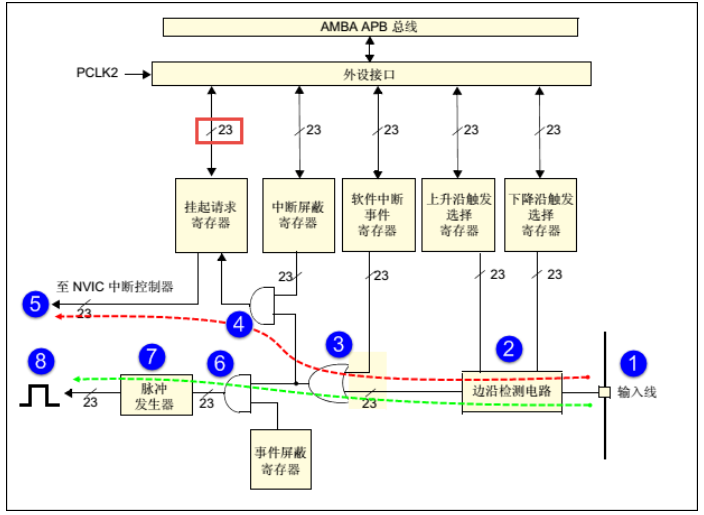

第七阶段 EXTI!!!!

1.EXTI---外部中断控制器,通过对IO上电平的检测,产生一个中断/事件,事件以脉冲形式传播,传给DAC/TIM,中断传给NVIC。一共有23条,8条特定,16条通用。

2.既然要检测IO,首先得配置寄存器(SYSCFG_EXTICR)来确定检测的是哪个IO,在用寄存器(EXTI_RTSR、EXTI_FTSR)来确定检测的边沿,当检测到边沿后会产生一个内部高电平。这里我觉得还需要考虑边沿检测的始终信号。

3.产生外部中断之后呢,STM32将外部中断与内部中断放在一起比较(或门),那软件中断从何而来?答曰,需要配置寄存器(EXTI_SWIER)全配置后才可产生。

4.到了这里还没完,还需要设置中断屏蔽寄存器EXTI_IMR(中断屏蔽)+EMR(事件屏蔽),当他们也设置使能之后才能有效。

5.事件到此就结束了,中断到此还最后还没完,还有挂起请求寄存器EXTI_PR,最终,全配置好才会产生请求。

6.为什么这么设置呢?我觉得1、程序更加稳定;2、功耗;

7.EXTI初始化结构体->配置哪个接口(EXTICR)、工作模式(IMR/EMR)、上升沿下降沿(RTSR/FTSR)、使能(后面的寄存器PR)

8.具体使用:1、定义结构体变量;2、配置连接的GPIO;3、配置EXTI;配置时定义端口的宏;4、配置NVIC;5、写中断服务程序;6、写main;

补充:STATIC 作用域为当前文件,

第八阶段:系统定时器-SysTick

1.4个定时器、递减计数器、流程为装载计数值、计数、技术完成产生中断、等待中断响应、清空中断请求、再次装载;

2.关键也是操作寄存器;

3.唯一固件库函数Systick_Config,首先载入寄存器,其次设置优先级,通过设置设置NVIC,IRQn中断号(内部),将为当前值配置为0,配置时钟源,使能寄存器 ;

4.extern 关键字,在此处调用外部的函数。static 可声明局部变量、全局变量、函数。。

第九阶段:直接存储器访问-DMA

1.外设可直接访问存储器,CPU给DMA一个地址与操作,DMA会自动进行。DMA1外设-内存,内存-外设;DMA2外设-内存,内存-外设,内存-内存;单次最大传输256K;每个DMA有8个数据流,每个流下有8个通道,需要可自由份配。每个通道都有一个仲裁器,当多数据流时,可通过软件配置与硬件配置设置优先级,默认先看软件配置,当软件配置一致时,看硬件配置,编号小的优先级高。

2.每个流有4个字的FIFO,通过PSIZE设置大小,通过SxFCR_FTH寄存器配置FIFO的阈值级别,SxFCR_MBURST配置突发,突发看成节拍,几个节拍发一次,突发在DDR与SDRAM中是常见的概念。

3.每个接口(外设接口与存储器接口)需要对应配置,例如DMA1外设接口只可对应AHB1,DMA事务(给定述目的数据传输序列),具体数目以及宽度由软件编程。

4.传输三个操作:1.加载数据。2.加载的数据存储,3.数据存储结束后DMA计数器递减。

4.寄存器包括:通道/流选择、外设地址、存储器0地址、数据数目、传输方向、外设数据宽度....优先级(PL)等等

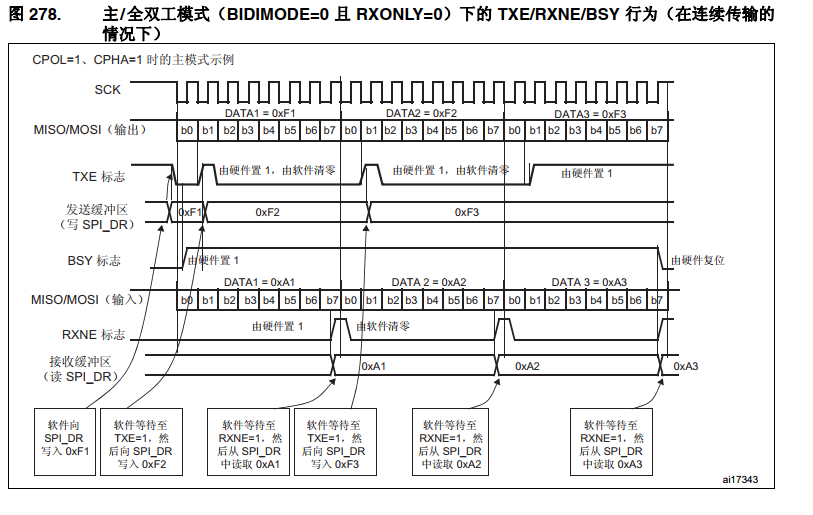

第九阶段:SPI

1.SPI与I2S公用一组接口接口。SPI框图

2.数据发送时并行加载到以为寄存器中,一旦发送缓冲区由数据时,发送序列开始。

3.数据接收时移位寄存器中的数据将传输到接收缓冲区,RXNE置1,将数据从发送缓冲区传输到移位寄存器时, TXE 标志(发送缓冲区为空)置 1表示发送缓冲区已准备好加载接下来的数据。

4.通过读取SPI_DR清零RXNE。

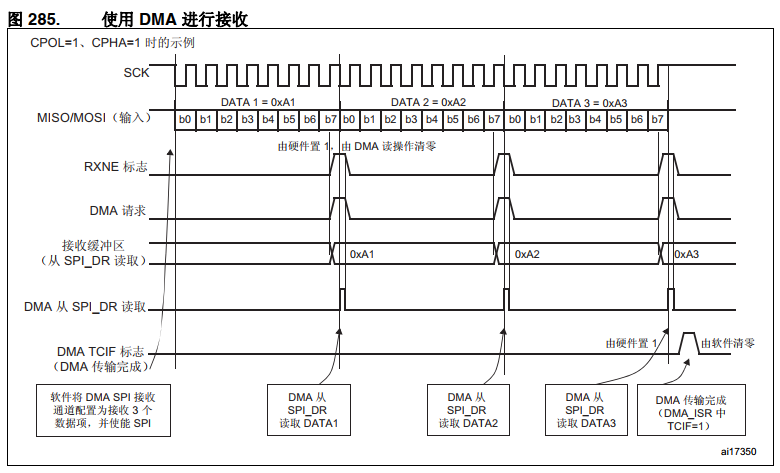

第十阶段、使用DMA进行SPI通信

第十一阶段、SDIO

浙公网安备 33010602011771号

浙公网安备 33010602011771号