##2018-2019-1 20165327 《信息安全系统设计基础》第四周学习总结

学习目标

- 了解ISA抽象的作用

- 掌握ISA,并能举一反三学习其他体系结构

- 了解流水线和实现方式

一、ISA

ISA简称架构(Architecture),是处理器的一个抽象描述,即设计规范,定义处理器能够做什么。其本质就是一系列的指令集综合。当前主流的ISA有X86、ARM、MIPS、Power、C6000。

ISA在编译器编写者和处理器设计人员之间提供了一个抽象层

处理器设计者:依据ISA来设计处理器

处理器使用者:依据ISA就知道CPU选用的指令集,就知道自己可以使用哪些指令以及遵循哪些规范

ISA抽象的作用:

二、流水线技术

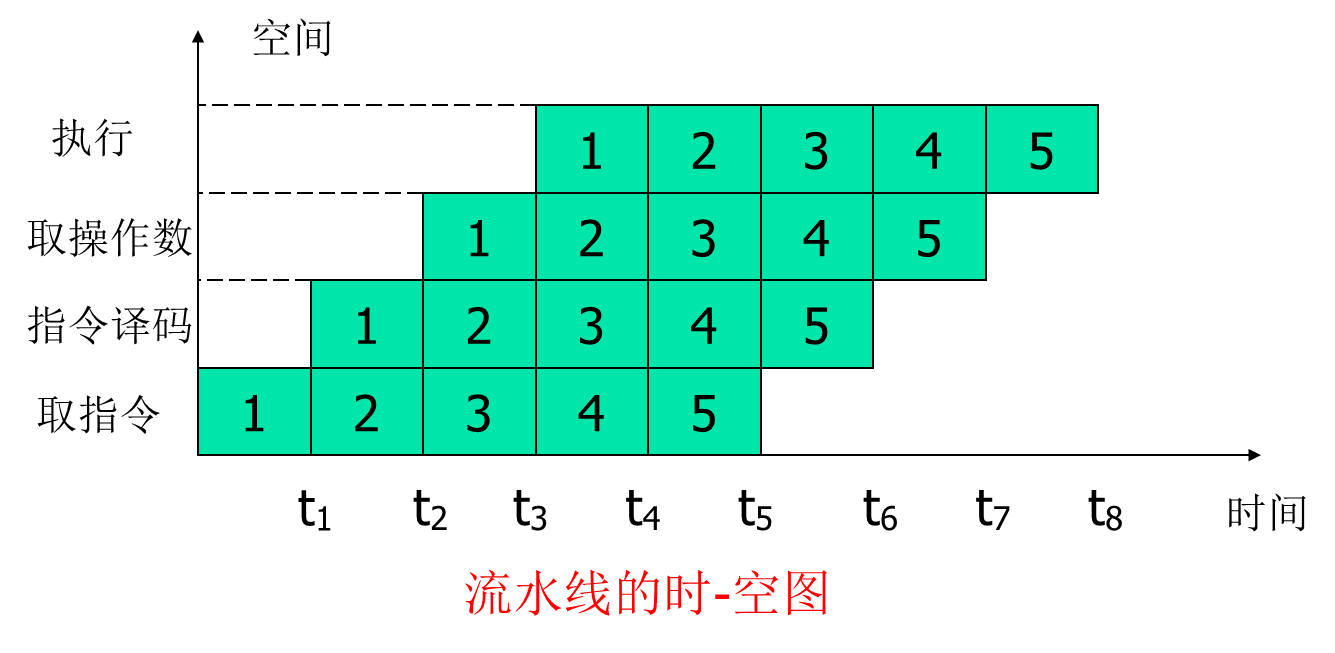

流水线(pipeline)技术是指在程序执行时多条指令重叠进行操作的一种准并行处理实现技术。

在CPU中由5—6个不同功能的电路单元组成一条指令处理流水线,然后将一条X86指令分成5—6步后再由这些电路单元分别执行,这样就能实现在一个CPU时钟周期完成一条指令,因此提高CPU的运算速度。

Y86-64指令体系架构

逻辑设计和硬件控制语言HCL

-

逻辑门是数字电路的基本计算元素,它们产生的输出,等于它们输入位值的某个布尔函数。一旦一个门的输入变化,在短时间内,输出就会跟着变化。

-

将很多逻辑门组合成一个网,就能构建计算块,称为组合电路。

-

通过将逻辑门组合成大的网,可以构造出能计算更加复杂函数的组合电路。能对数据字进行操作的电路,称为字级的组合电路。

-

在处理器设计中,很多时候需要将一个信号与许多可能匹配的信号做比较,一次来检测正在处理的某个指令代码是否属于某一类指令代码。可以用集合关系来表示这样的属性。

-

为了产生时序电路,引入按位存储信息的设备,都由同一个时钟控制。两类存储器设备:时钟寄存器,随机访问存储器。时钟寄存器保存程序计数器(PC)、条件代码(CC)、程序状态(Stat)。

Y86-64的顺序实现

处理一条指令的阶段:

- 取指(fetch)

- 译码(decode)

- 执行(execute)

- 访存(memory)

- 写回(write back)

- 更新PC(PC update)

SEQ硬件结构(顺序的硬件结构)

在SEQ中,所有的硬件单元的处理都是在一个时钟周期内完成的。

SEQ的实现包括组合逻辑和两种存储器设备,遵循处理器从不回读的原则。