Verilog-译码器

Verilog-译码器

学习目的

使用3-8译码器,巩固FPGA设计流程以及基础语法的使用

理论学习

译码器:译码是编码的逆过程,在编码时,每一种二进制代码,都赋予了特定的含义,即都表示了一个确定的信号或者对象。把代码状态的特定含义翻译出来的过程叫做译码,实现译码操作的电路称为译码器。或者说,译码器是可以将输入二进制代码的状态翻译成输出信号,以表示其原来含义的电路。

译码器(decoder)是一类多输入多输出组合逻辑电路器件,其可以分为:变量译码和显示译码两类。

常见译码:n ->2^n 线

显示译码:二进制码 -> 晶码管

实战演练

硬件设计:使用三个按键作为译码器的输入,通过观察LED灯的亮灭来观察输出信号

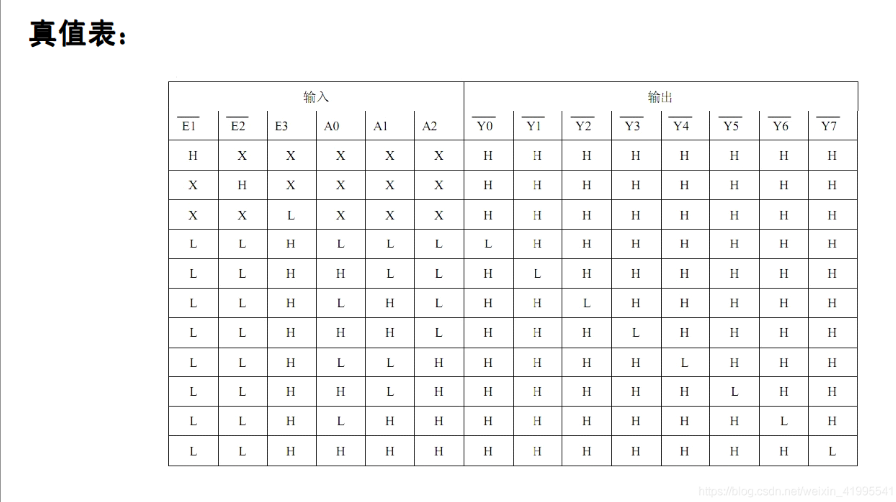

真值表:

嵌入代码

法一.

{

module ic_74138(

E1,E2,E3,

A,

Y

);

input [2:0] A;

input E1,E2,E3;

output reg [7:0] Y;

always@(*)

begin

if(E3==1&&E2==0&&E1==0)

begin

case(A) //这里可以用拼接运算符,case({E3, E2, E1})

3'b000:Y=8'b0111_1111;

3'b001:Y=8'b1011_1111;

3'b010:Y=8'b1101_1111;

3'b011:Y=8'b1110_1111;

3'b100:Y=8'b1111_0111;

3'b101:Y=8'b1111_1011;

3'b110:Y=8'b1111_1101;

3'b111:Y=8'b1111_1110; //这里包含所有情况,不会产生latch,所以不需要加default

endcase

end

else

Y=8'b1111_1111;

end

endmodule

}

法二.

{

module decoder3_8

(

input wire in1 , //输入信号in1

input wire in2 , //输入信号in2

input wire in3 , //输入信号in2

output reg [7:0] out //输出信号out

);

//out:根据3个输入信号选择输出对应的8bit out信号

always@(*)

if({in1, in2, in3} == 3'b000) //使用"{}"位拼接符将3个1bit数据按照顺序拼成一个3bit数据

out = 8'b0000_0001;

else if({in1, in2, in3} == 3'b001)

out = 8'b0000_0010;

else if({in1, in2, in3} == 3'b010)

out = 8'b0000_0100;

else if({in1, in2, in3} == 3'b011)

out = 8'b0000_1000;

else if({in1, in2, in3} == 3'b100)

out = 8'b0001_0000;

else if({in1, in2, in3} == 3'b101)

out = 8'b0010_0000;

else if({in1, in2, in3} == 3'b110)

out = 8'b0100_0000;

else if({in1, in2, in3} == 3'b111)

out = 8'b1000_0000;

else

out = 8'b0000_0001;

}

两种代码的差别

两种代码产生的RTL图不一样

if-else存在优先级,产生了八个二选一的数据选择器

case-endcase语句产生了一个input[2:0]->output[7:0]的译码器

附录

testbeach

{

module tb_decoder3_8();

//********************************************************************//

//****************** Parameter and Internal Signal *******************//

//********************************************************************//

//wire define

wire [7:0] out;

//reg define

reg in1;

reg in2;

reg in3;

//********************************************************************//

//***************************** Main Code ****************************//

//********************************************************************//

//初始化输入信号

initial begin

in1 <= 1'b0;

in2 <= 1'b0;

in3 <= 1'b0;

end

//in1:产生输入随机数,模拟输入端1的输入情况

always #10 in1 <= {$random} % 2;

//in2:产生输入随机数,模拟输入端2的输入情况

always #10 in2 <= {$random} % 2;

//in3:产生输入随机数,模拟输入端3的输入情况

always #10 in3 <= {$random} % 2;

initial begin

$timeformat(-9, 0, "ns", 6); //打印时间格式设置

$monitor("@time %t: in1=%b in2=%b in3=%b out=%b", $time, in1, in2, in3, out); //监测函数设置

end

//********************************************************************//

//**************************** Instantiate ***************************//

//********************************************************************//

//------------- decoder3_8_inst ------------- //实例化

decoder3_8 decoder3_8_inst(

.in1 (in1), //input in1

.in2 (in2), //input in2

.in3 (in3), //input in3

.out (out) //output [7:0] out

);

endmodule

}

浙公网安备 33010602011771号

浙公网安备 33010602011771号