微机原理 Pro Max (第三章 存储器系统)

考点1存储系统层次、类型及特点

1. 存储器:内存【主存】、外存【辅存】

2,半导体存储器的分类: RAM、 ROM

考点:RAM的分类 和 ROM 的分类

3,静态与动态存储器的构成及其特点,SRAM 6264、 DRAM 2164的引脚构成

6264 8kx8 2^13 ——A0~A12 D0~D7

2164动态 64kx1 2^16 D0 一位数据线 在实际中用到的只是 地址线的一半 RAS和CAS共构成16位 分别用到8位 分时复用

考点2存储器的性能指标

1. 概念:

位:

字节:

字:

存储单元的字节编址:

2.容量与地址范围关系:

(1) 88/86主存容量1MB: 2^20个字节(存储单元) 存储单元=8个二进制位=一字节

(2) 中断向量表的1KB:

(3) I/0接口或主存段的容量64KB:

(4)6264芯片容量: 8kx8 存储单元数x 位数

给了地址范围如何计算容量?

末-首+1 或 末地址+1-首地址

A000OH~DFFFFH的内存空间的容量:

末+1-首

=DFFFFH+1-40000H

=C0000H-40000H

=80000H

=8x16^4=2^3(2^4)^4=2^19

=512k

存储单元是指(C)。

A.存放一个二进制信息位的存储元

B.存放一个机器字的所有存储元的集合

c./存放一个字节的所有存储元的集合 [8个存储元构成的]

D.存放两个字节的所有存储元的集合

三、简答题 有两个16位的字31DAH和SE7FH,它们在8086系统存储器中的地址分别为00130H和00134H,试画出它们的存储示意图。

3、芯片容量、地址线、数据线

(1)SRAM6116有3条控制线,他们是( D )。

A. OE、 MREQ、 WE B. MREQ, CS, WE

C. OE, CS、 MREQ D. OE、 CS, WE

【RAM中 有 读 OE 写 WE 片选 CS/CE】

【6264 SRAM 有 OE WE CS 】

[2164 DRAM 有 WE [读=1,写=0] CS ]

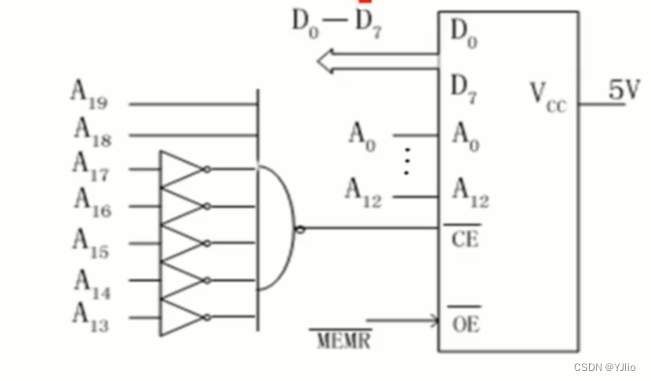

考点3:地址译码方法

1.译码器件:

(1)门电路译码:

先看片选信号CE 低电平为0 连接左边 与非门 与门全1 遇到非门为0

起初地址为1100000 :C0000H

末地址为 1111111 :CFFFFH

地址线 A0~A12 2^13x8 8kb容量

(2)译码器译码

①3:8译码器

3:8译码器应用:

G2A G2B 都为 低电平 0

G1 为 1

G2B接入或门为000000

G1 与门 为111

连接到哪个点 需要看输入端 C B A 的值

C B A

1 0 1 Y5

1 1 0 Y3

1 1 1 Y7②2:4译码器

2.译码方法(后面真题)

(1)线选

(2)部分译码

(3)全译码

考点4主存储器与CPU的连接画图

(1) CPU系统提供的类型、字长、地址线和数据线;

(2)形成主存的单片芯片的类型、容量和引脚;

(3)形成主存的总容量 【8kx8 一般来说指的是8088的cpu 8086的是16位】

(4)字扩展(组数)或位扩展(每组片数)

(5)译码方式的选择

(6)各组地址范围的使用或计算

用2K×8位的存储芯片,组成16K×8位的存储器,需要__字__扩展,需要__8___片2K×8芯片。

16kx8

2kx8 =8x1

1、机器配有一个 ROM 芯片,地址空间 00OOH-3FFFH,现在再用几个 16K×8 的芯片构成一个 32K×8 的 RAM 区域,使其地址空间为 8000H-FFFFH。假设此 RAM 芯片有CS有 WE信号控制端, CPU地址总线为Ais-Ao,数据总线为Dr-Do,控制信号为R/w、MREQ,当且仅当MREQ和R/w同时有效时, CPU才能对存储器进行读(或写),要求选用2:4译码器。

(1)画出此 CPU与上述ROM芯片和RAM芯片的连接图。(9 分)

(2)所用 ROM 芯片容量多大? (2分)

(3)写出图中所用每片RAM的地址范围。(4分)

考点588/86CPU 的内存分配、两种地址变换方法

(1)存储器的分段

例如:

88/86采用分段管理内存,每个段最大可达(64k)字节。

88/86访问主存时的最大物理空间是1MB

88/86访问1/0时的最大物理空间是64KB

(2)两种地址:

逻辑地址: 段地址:偏移地址

DS,CS,SS:EA,IP,SP/BP

物理地址: 段地址x16+偏移地址

1.8086有20地址线,可寻址的地址空间为(D)。A. 4M B. 3M C. 2M D. 1MB

2^20

2. 8086系统中,代码寄存器CS=3000H,指针寄存器IP=2300H,则该寄存器的物理地址为(C)

A. 5300H B. 26000H C. 32300H D. 23000H

考点68086主存的分体结构

偶地址规则字 连接低八位

偶地址规则字 连接低八位

奇地址非规则字 连接高八位

若需访问8086存储体的对准字,则可分几次访问存储器,并且所需控制信号是哪个才能读/写这个字的信息A

A. 1, BHE=0,A,=0

B. 1, BHE=0,A,=1

C. 2, BHE=0,Ao=0

D. 2, BHE=1,Ao=1

1.目前广泛使用的U盘,用的是下列哪种存储器( )。A. 掩模式ROMB.闪速存储器FlashC. PROMEPROM需讠息

2,半导体存储器主要分为两大类,即__RAM__和_ ROM_____

3. 8086的存储器按___字节_____进行编址。

4,在对存储器芯片进行片选时,有全译码方式、部分译码方式及线选方式,简述这3种方式各自的概念及优缺点。

全译码方式:所有的系统地址线都参与对存储单元的译码寻址。其中,低位地址线对片内存储单元进行译码寻址,高位地址线对存储芯片进行译码寻址(片选译码),在此方式下,每个存储单元的地址都是唯一的,无重复地址,但译码电路复杂,连线较多。

部分译码方式:只有部分高位地址线参与对芯片的译码,对于被选中的芯片,这些未参与译码的高位地址可以是0也可以是1,因此,每个存储单元对应多个地址(地址重复),需要选取一个可用地址,按0时使用的地址称为基本地址。此译码方式可简化译码电路的设计,但地址重复,系统的部分地址空间被浪费。

线选方式:只有少数几根高位地址线参与芯片的译码,且每根负责选中一个芯片(组),地址有可能不连续。不需要译码。此方法构成简单,但地址空间严重浪费,有地址重复现象。

5,半导体存储器有哪几个性能指标,简述各自概念。

(1)存储容量:半导体存储器存储信息量大小的指标。半导体存储器的容量越大,存放程序和数据的能力就越强。

(2)存取速度:用存取时间来衡量的,它是指存储器从接收CPU发来的有效地址到存储器给出的数据稳定地出现在数据总线上所需要的时间。

(3)功耗:指它在正常工作时所消耗的电功率。通常,半导体存储器的功耗和存取速度有关,存取速度越快,功耗也越大。

(4)可靠性:指它对周围电磁场、温度和湿度等的抗干扰能力。可靠性较高,寿命也较长,用平均无故障时间来衡量。

(5)集成度: 指它在一块数平方毫米芯片上能够集成的晶体管数目,有时也可以每块芯片上集成的“基本存储电路”个数来表征。

.动态RAM采用(A)及 MOSFET作为记忆元件,要求每隔2ms新一次。A.电容B.电感C.电阻D.电极

DAM由电容组成电容需要刷新

2. 高速缓冲存储器是用价格高昂的双极型【SRAM】RAM制作的,它主要加在

(A.主存储器与辅助主存储器之间

B.CPU与接口之间

c.接口与外设之间

D.CPU与主存储器之间

3.衡量半导体存储器性能最重要的指标是存储芯片的容量和存取速度,其中存储芯片容量__

1_能容纳的二进制位数 2单元数x数据线位数 3 2^mXn

//达存储容量的定义 要多写

4. Intel2164A是一种典型的动态RAM芯片,其引脚如下图所示。8片2164A构成64KB存储器,请问:

(1)如何利用8条地址线在芯片内寻址64K单元?用到哪些信号引脚?

(1)DRAM地址线采用行地址线和列地址线分时工作,DRAM对外部只需引出8条地址线。(2分)

片内部有地址锁存器,(1分)利用多路开关,由行地址选通信号RAS(Row Address Strobe, 4号引脚),把先送来的8位地址送至行地址存器(2分); 由随后出现的列地址选通信号CAS (Column Address Strobe15号引脚)把后送来8位地址送至列地址存器。(2分)

(2) Intel2164A数据读写是如何实现的?用到哪些引脚?

(2)2164A数据的读出和写入是分开的,由WE信号控制读写。(2分)当WE为高电平时,读出,即所选中单元的内容经过三态输出缓冲器在Dout引脚读出, (2分)当WE为低电平时,实现写入。(2分)Din引即上的信号经输入三态缓冲器对经输入三态缓冲器对选中单元进行写入。(2分)

1. 8086CPU的最大内存地址空间是( )A. 1KB B. 1MBC. 256MBD. 64KB

2.当EPROM擦除后,每个单元的内容为()A. 00HB. CCH C. AAH D. FFH

3,需要定时刷新的存储器是()。A. SRAM B. DRAM C. EPROMD. EEPROM

4.256K×8的RAM芯片需要条地址线。_【sram】__18条地址线__ 【dram】 9条地址线

//如果没强调是sram还是dram 默认 按照sram

dram显示的是sram的一半地址线数量

在8086微处理器构成的系统中,什么是存储器的规则字和非规则字? 8086微处理器对一个规则字和一个非规则字读写时,有什么差别?

参考答案:

1规则字是在存储器中存储的起始地址为偶数(地址最低位A0为0)的字数据,非规则字是指在存储器中存储的起始地址为奇数(地址最低位A0为1)的字数据(4分)

②规则字读写需要一个总线周期(2分) ,发送A0为0, BHE为0,一个总线周期读写一个字。(1分)

③非规则字读写需要两个总线周期(2分)。第一个总线周期读写时先读取奇存储体(奇地址)数据,Ao为1,BHE为0,取得低8位数据,第二个总线周期读收偶存储体(或偶地址)数据,Ao为0, BHE为1,取得高8位数据(1分)。

1.若一SRAM芯片的容量是1024×8位,除电源和接地线外,该芯片的其它引脚最少应为(D/C 强调了最少 D)根。

A. 23B. 22C. 21D. 20

//sram考虑常规1024=2^10 + 8位 数据线 共18根 控制线涉及到 OE WE CS

2. 若形成存储字长为8位,空间为6000H~67FFH的存储器系统,则需要1K×4位的存储芯片(B)片。A. 2B. 4C. 6D. 8

//空间范围运用 末地址+1-首地址 =800H 十六进制转换为2进制 8x16^2= 2^3x(2^4)^2=2^11=2kb

2kbX8

_____

1kbx4 =2x2 =4片

3为系统程序区设计一个容量为4096个存储单元的存储器系统,存储字长为8位,现有如下RAM芯片(1K×8位,2K×4位,2K×8位,4K×4位)和ROM芯片(1K×2位,1K×4位,2K×16位)若干,用RD和WR分别作为读、写控制信号,CS为片选信号。请合理选择各种芯片并运用适当的门电路或译码电源,画出该存储器系统的连接结构图。

4·微机系统中,增加高速缓冲存储器CACHE的目的是(A. 提高CPU的运行速度B. 增加内存的存储空间c.缓解通信部件之间的速度矛盾问题D. 提高内存的工作速度

1.堆栈的工作方式是(A. 随机读写B. 先进先出c. 只写不能读 D. 后进先出

2.某存储芯片有地址线12根,数据线8根,则该存储芯片的容量为( )。A. 1K×8B. 2K×8C. зK×8D4K×8

3.SRAM需要定时刷新以保持存储的信息不丢失。(X)

dram才需要刷新

ROM、PROM、EPROM和EEPROM在使用上各有什么特点?

①ROM为只读存储器,制造时数据就已经固化好(1分),使用中不可以改变(1分)。

②PROM为一次可编程只读存储器,出厂时内容为空白(1分),只可以写入一次数据(1分)。③EPROM为可擦除只读存储器,出厂时内容为空白(1分),写入数据后可以通过紫外线照射擦除(1分),可以多次写入和擦除(1分)。

④EEPROM为电可改写只读存储器,出厂时内容为空白(1分),写入数据后可以使用电信号擦除(1分),可以多次写入和擦除(1分)

计算机系统中存储器系统是指(D)

A. RAM存储器B. ROM存储器c.主存储器D,/Cache、主存储器和外存储器

动态RAM的特点是(B)

A.工作中存储的内容动态的变化 B. 每隔一定时间刷新一遍【读时刷,数据不进数据总线,假读时刷】

c.工作中需要动态地改变访存地址 D.每次读出后需根据原存内容全部刷新一遍

SRAM 6116有3条控制线,它们是

A. OE、 MREQ、 WE( B. MREQ、 CS、 WE

C. OE, CS, MREQ D. OE、 CS、 WE

电擦除可编程只读存储器是(B)A. PROMB. E2PROMC. EPROMD. ROM

RAM是一种(B)的内存储器。

A. 永久性、随机性 B.易失性、随机性

c. 永久性、只读性 D. 易失性、只读性

下列RAM芯片中,各需要多少根地址线?多少根数据线?

(1) 512×8RAM,地址线___9___根,数据线 8 根;

(2) 16K×1RAM,地址线 14 根。数据线 1 根

要组成容量为4K×8的存储器,需要__/8___片4K×1位的静态RAM芯片并联,或者需要_ 4___片1K×8位静态RAM芯片串联。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· DeepSeek 开源周回顾「GitHub 热点速览」

· 记一次.NET内存居高不下排查解决与启示

· 物流快递公司核心技术能力-地址解析分单基础技术分享

· .NET 10首个预览版发布:重大改进与新特性概览!

· .NET10 - 预览版1新功能体验(一)