第2章 十六位微处理器(一)

1. 8086/8088CPU的内部结构和外部引线;

2. 8086/8088CPU 的工作方式;

3. 8086/8088CPU 系统总线的形成;

4. 总线操作及时序。

2.1 8088/8086 微处理器

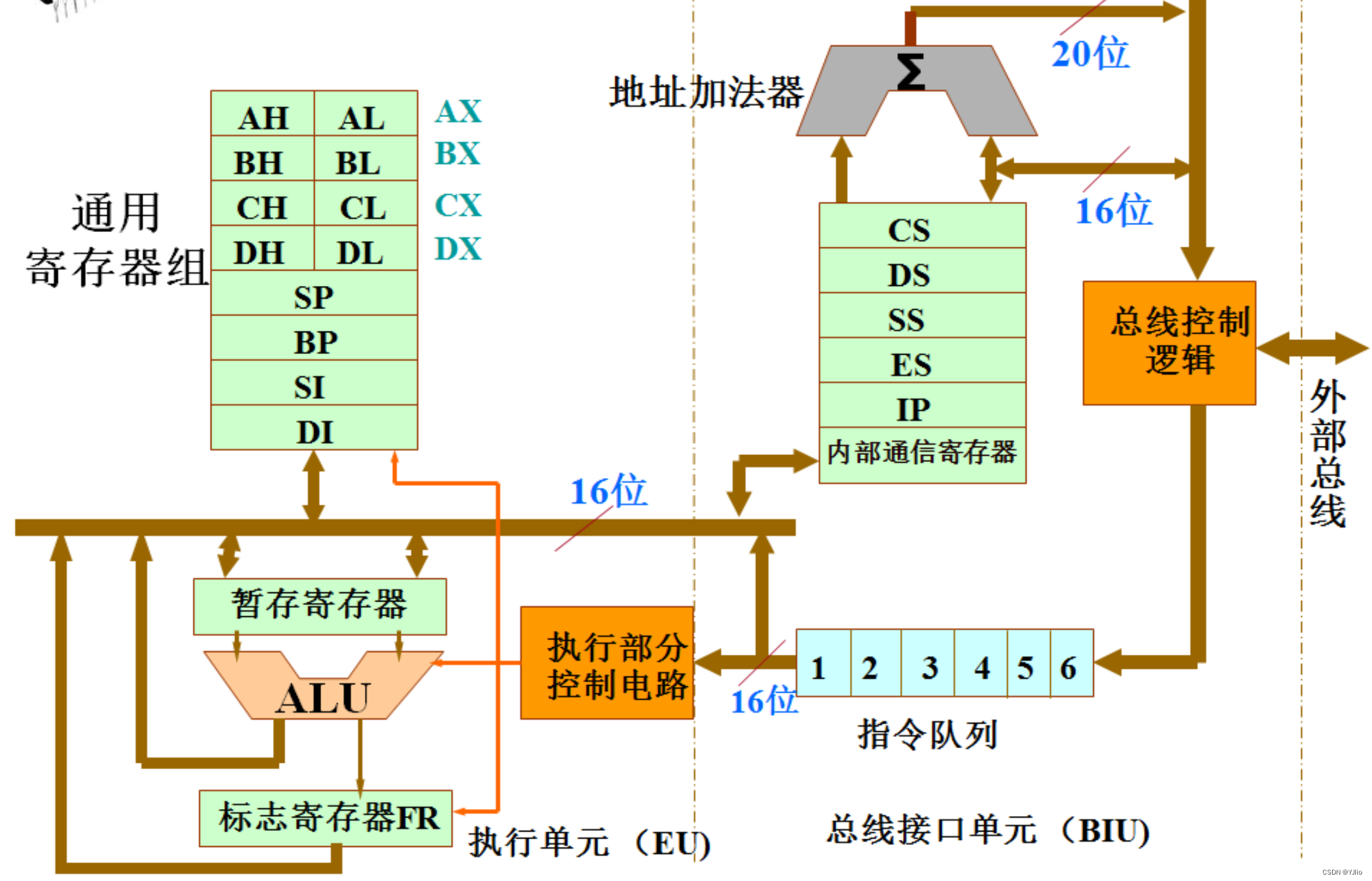

一、8088/8086的功能结构

EU:执行单元

ALU:

算数:

逻辑:

CU:

分析译码产生控制流

BIU:总线接口单元

取数据/指令:与内存进行交互

送结果: 送入到内存/外设

左侧 运算器 ALU算数逻辑单元 控制器作为CPU内部的两大功能部件

寄存器组 共有 16个14位寄存器

标志寄存器用于保存结果的 标志位

左侧 为 EU 执行单元

BIU单元 【总线接口单元】

加法器 用于形成20位物理地址

指令队列 从内存或其他部件,取指令之后,通过系统总线,存入cpu内部的指令队列

8088/8086的执行指令的工作过程

取指令:BIU

分析指令:EU

执行运算/处理(ALU)EU

送结果 :BIU

| T1 | T2 | T3 | 。。。 | |

| EU | 执行1 | 执行2 | ..... | |

| BIU | 取1 | 取2 | 取3 | ..... |

| 并行,流水线技术 | ||||

二、8088/8086的寄存器结构

8088/8086的寄存器组有14个: 【16位】

8个通用寄存器

4个段寄存器

1个标志寄存器

1个指令指针寄存器

1. 通用寄存器

8088有8个通用的16位寄存器(在EU)。

(1)数据寄存器:

| AX | 累加器 | 都是16位寄存器,分为 高8位 H 低8位 L AH,BH,CH,DH AL,BL,CL,DL |

| BX | 基址寄存器 | |

| CX | 计数器 | |

| DX | 数据寄存器 |

(2)变址寄存器

| SI | 源变址寄存器 |

| DI | 目标变址寄存器 |

(3)指针寄存器:

| BP | 基址寄存器 |

| SP | 堆栈寄存器 |

2. 段寄存器(在BIU)使用规定

段地址:段基地址,段首地址

| DS Segment | |

| CS | 代码段(指令) |

| SS | |

| ES | |

| 功能 用法 | |

| DS:EA 对应有效地址 | |

| SS | |

| ES | |

| CS:IP :逻辑地址 | |

3,指令指针寄存器(在BIU)

IP:16位专用于存放:

将要执行的下条指令地址

【AX,BX,CX,DX,SI,DI 保存的是数据的地址 IP保存的是指令的地址】

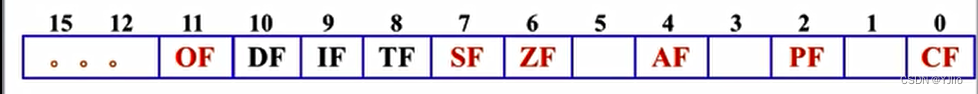

4标志寄在器(在EU)

分为 6个状态位:

OF 溢出标志位

SF:符号标志位

ZF:0标志位

AF:辅助进位标志位

PF:偶校验

CF:进位借位标志位

3个控制位

DF:方向标志

IF:中断标志

TF:单步

思考题

1.写出CPU中的主要寄存器。

2.下面()不是通用寄存器。

A. SS B. AX C. DX D. SI

3.微处理器8086存放当前数据段地址的寄存器是()

A. CS

B. DS

C. ES

D. SS2.2 8088/8086 CPU引脚

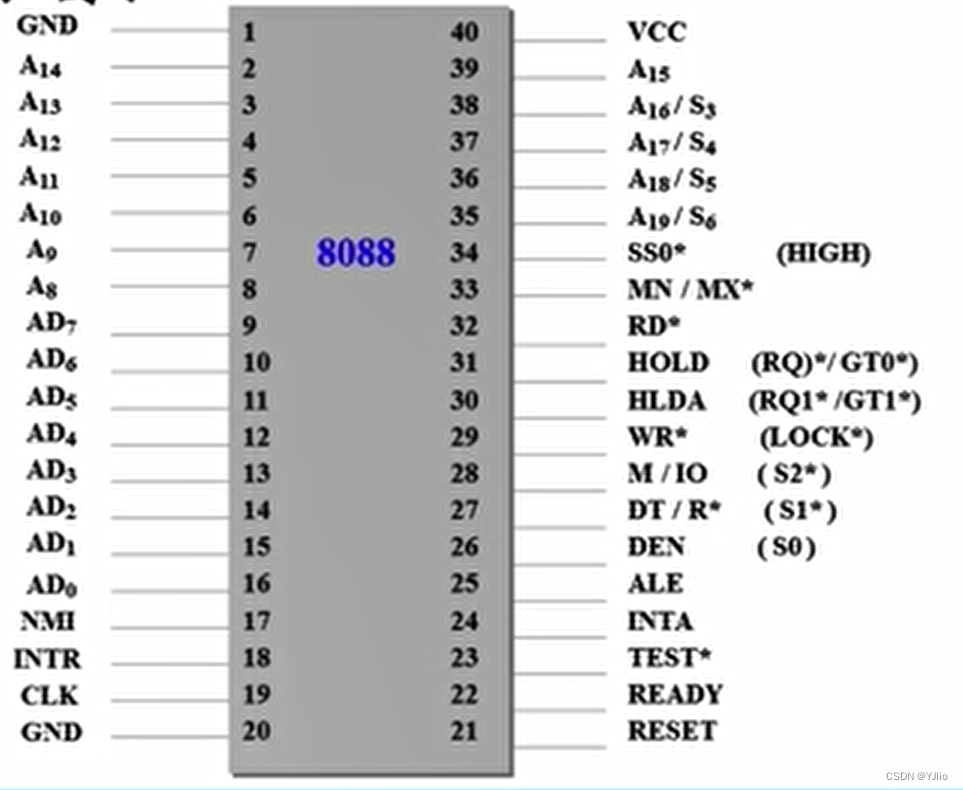

只有40个引脚

挂A的都是 地址总线 地址线是输出的

挂D的都是 数据总线 数据线是双向的

代杠的表示低电平有效

(1)引脚的功能

(2)信号的流向

(3)有效电平

(4) 分时复用

(5) 三态能力

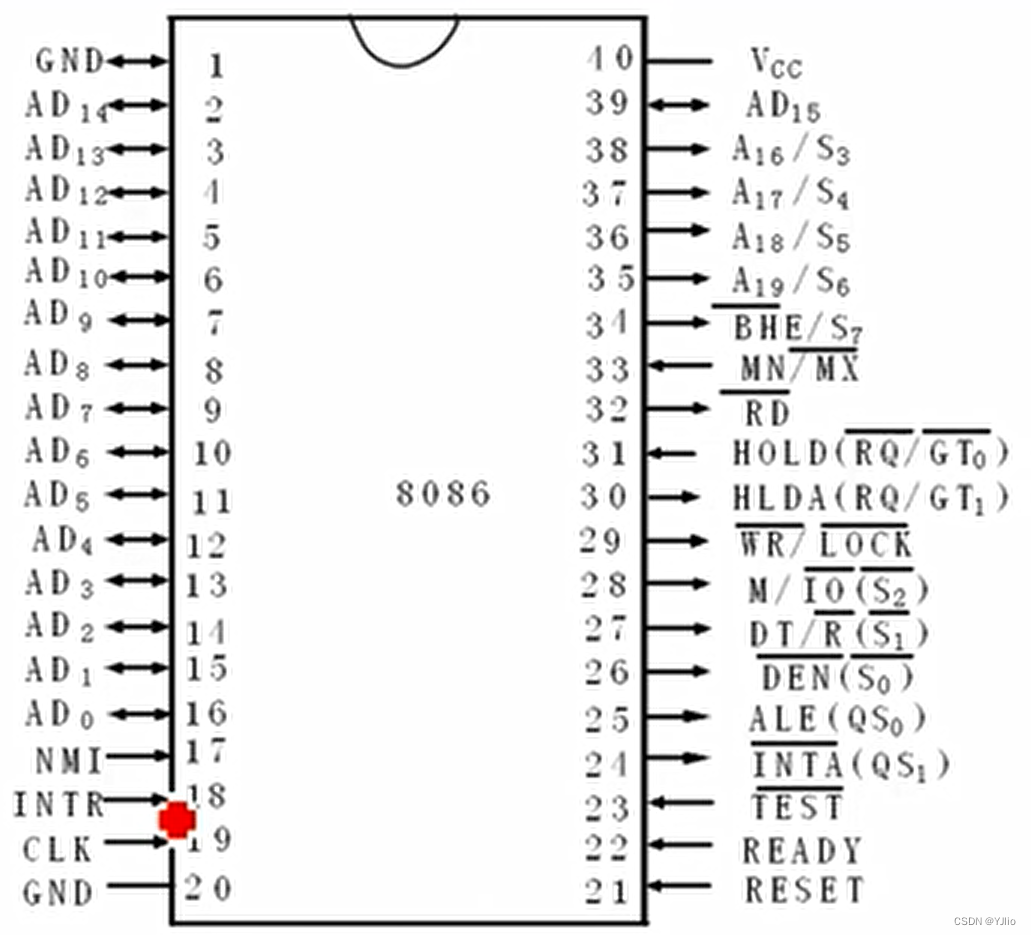

(6) 8088/8086区别

88和86的区别

一、 A和D复用脚 只有8个 AD0到AD7

86上的复用脚 20个 AD0到AD19

二、34号脚

CPU访问主存时总线高允许

![]()

88上没有这个34号脚 因为 88只有8位的数据线

28号脚的高低电平不同

![]()

一、最小工作模式的引脚信号

分类学习40个引脚(总线)信号:

地址总线AB/数据总线 【复用】 CB控制 88 A0-A19 D0-D7 中断,读/写,DMA,最大,最小 86 A0-A19 D0-D15

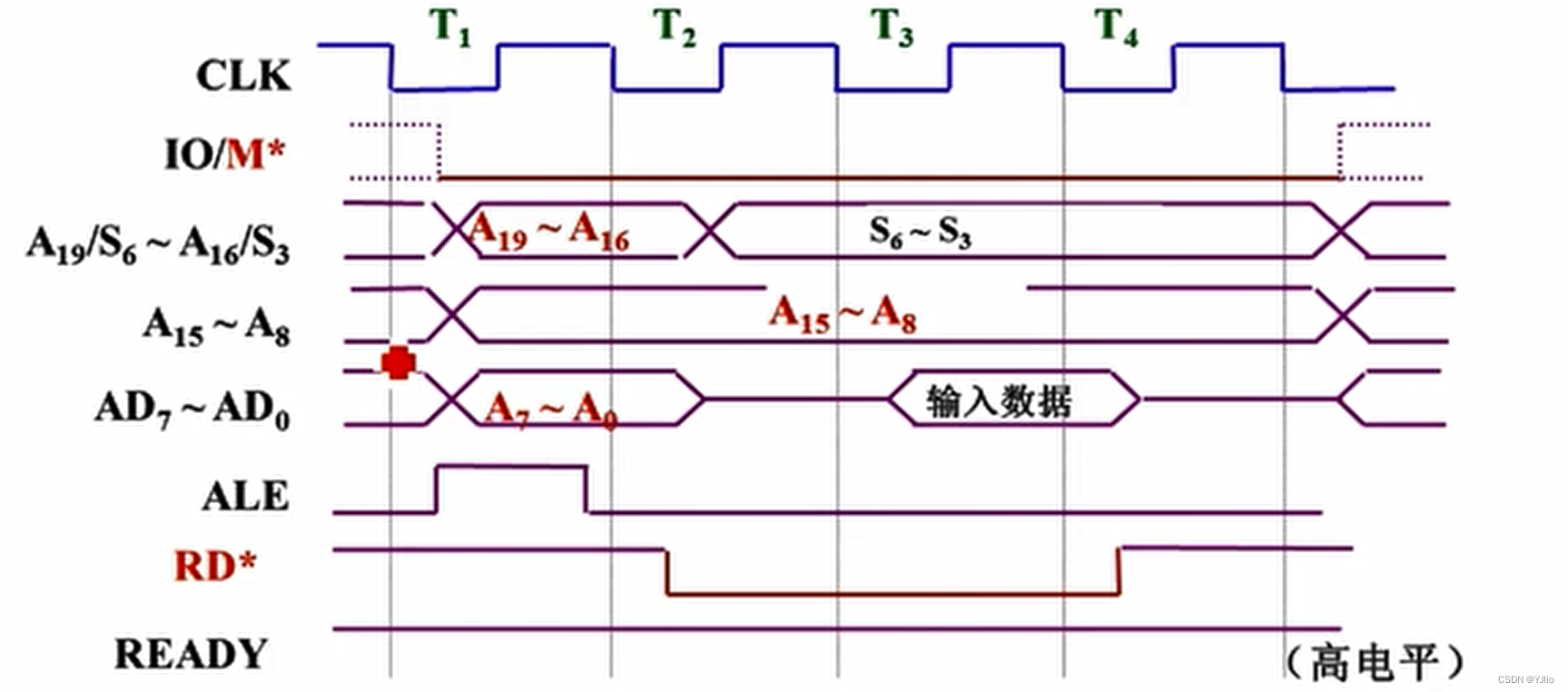

1.8088的数据和地址复用引脚

AD0-AD7: 分时复用 {T1:A0-A19 T2-T4:D0-D7 S3-S6}

A8——A15

A16S3-A19S6 状态线

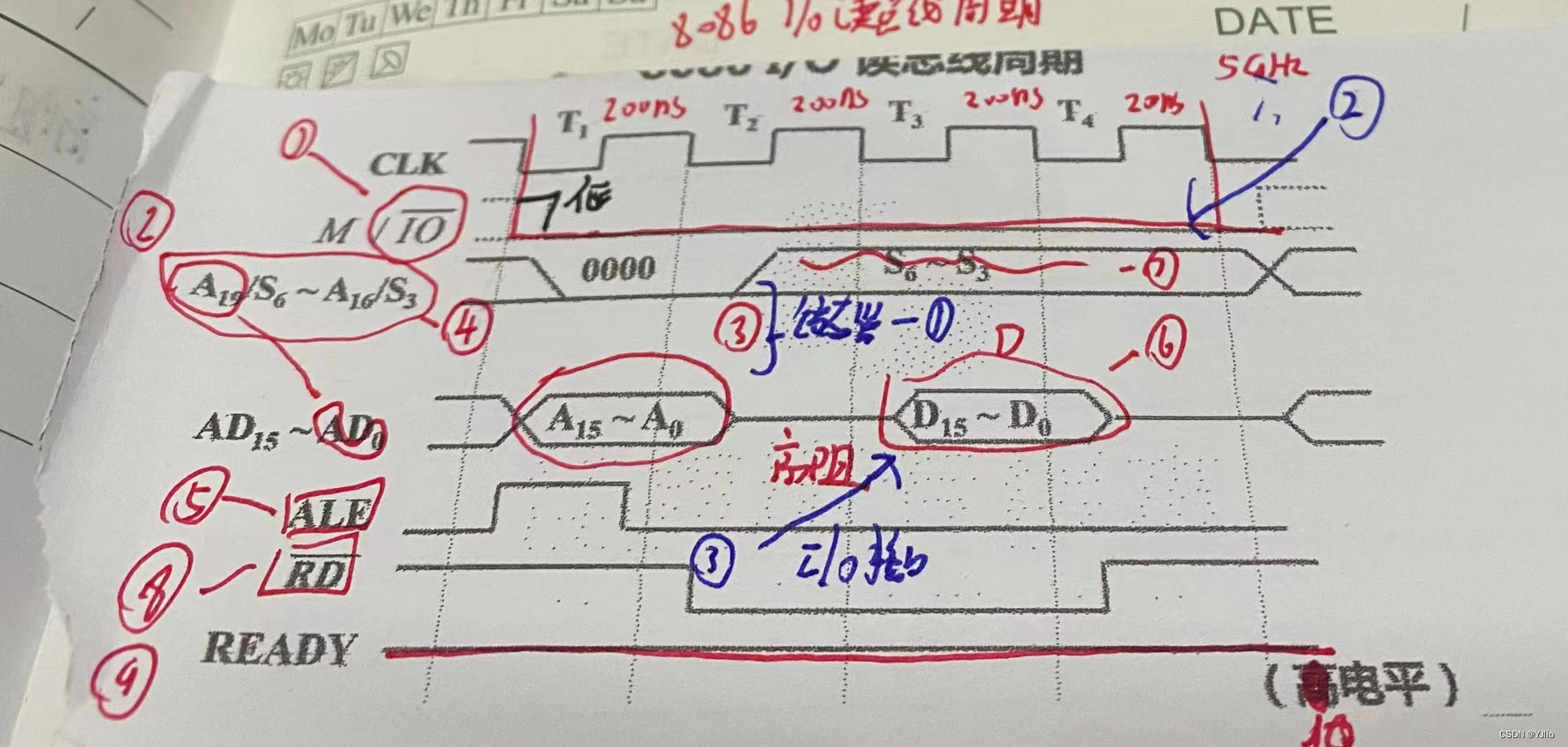

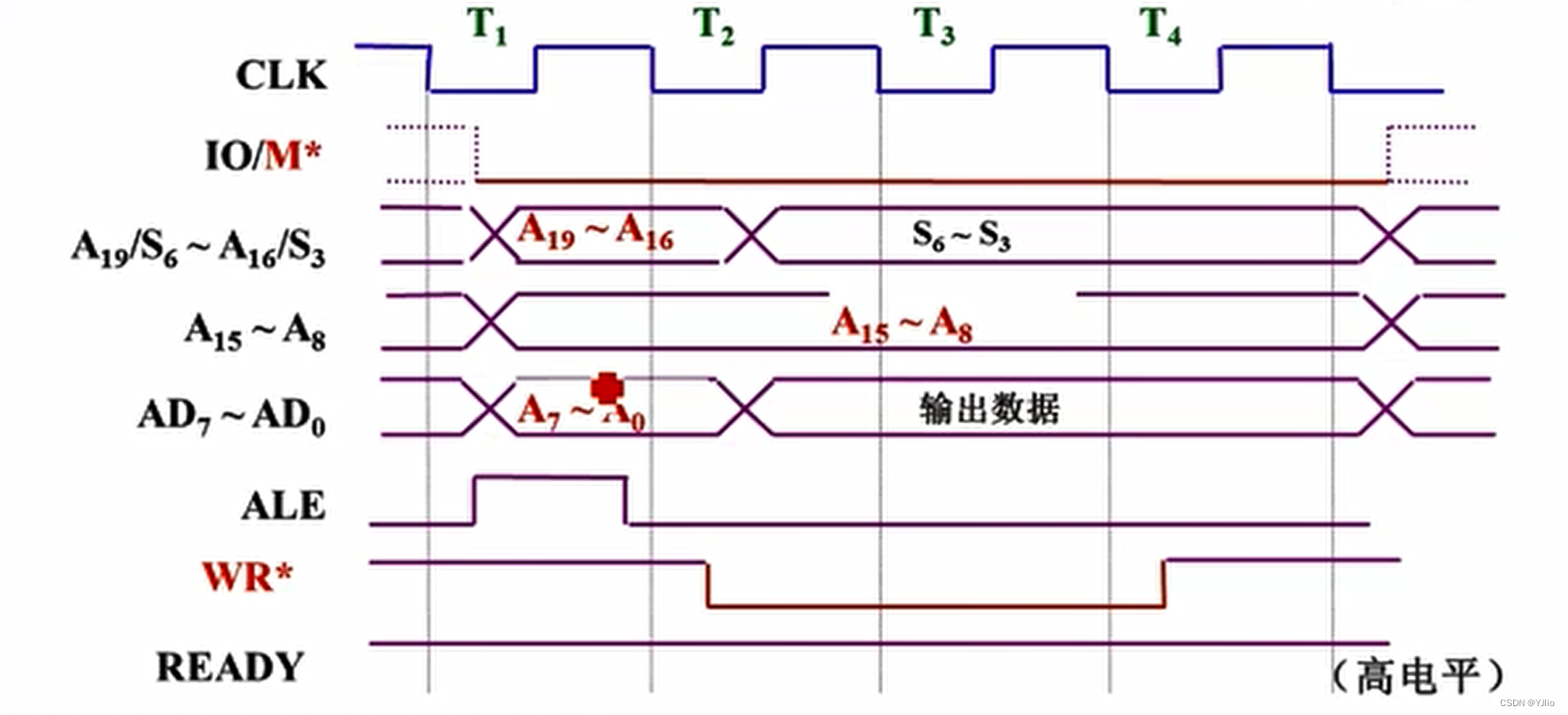

首先看最上方的 T 称作时钟周期,时钟频率的倒数,时钟周期的长度,和cpu的主频有关

5GHZ/1 的时钟周期200ns 5x10^6/1

序号1 低电平有效

T1时期 地址有效

T1时期 ALE有效

2.读写控制引脚

(1) ALE (Address Latch Enable)

T1 锁 A0-A19 【20位】 进入地址锁存器

(2) IO/Μ

CPU访问 外设 I/O =高电平

主存 M=低电平

(3) 写控制

WR,低电平,输出,三态

(4)读控制

RD 输入,主存 34都是高阻态

(5) Ready:

数据和CPU已经准备好。

TW有关

(6) DEN (Data Enable)

数据有效

(7) DT/R (Data Transmit/Receive)

写 读

3.中断请求和响应引脚

(1) INTR (Interrupt Request)

可屏蔽中断请求信号【引脚】

与IF=1 开中断 IF=0关中断

(2) INTA (Interrupt Acknowledge)

响应

3) NMI (Non-Maskable Interrupt)

非屏蔽,与IF无关

中断信号比较

| NMI | INTR | |

| 名称 | 非屏蔽中断请求信号 | 可屏蔽中断请求信号 |

| 中断类型 | 外中断 | 外中断 |

| 中断类型号 | 2型 | 由外设提供n |

| IF | 无关 | IF=1 开 IF=0关 |

| 触发方式 | 边沿(上升沿) | 高电平有效 |

| 响应信号 | 无 | INTA |

| 响应条件 | 当前啊指令执行结束 | 开中断、指令结束 |

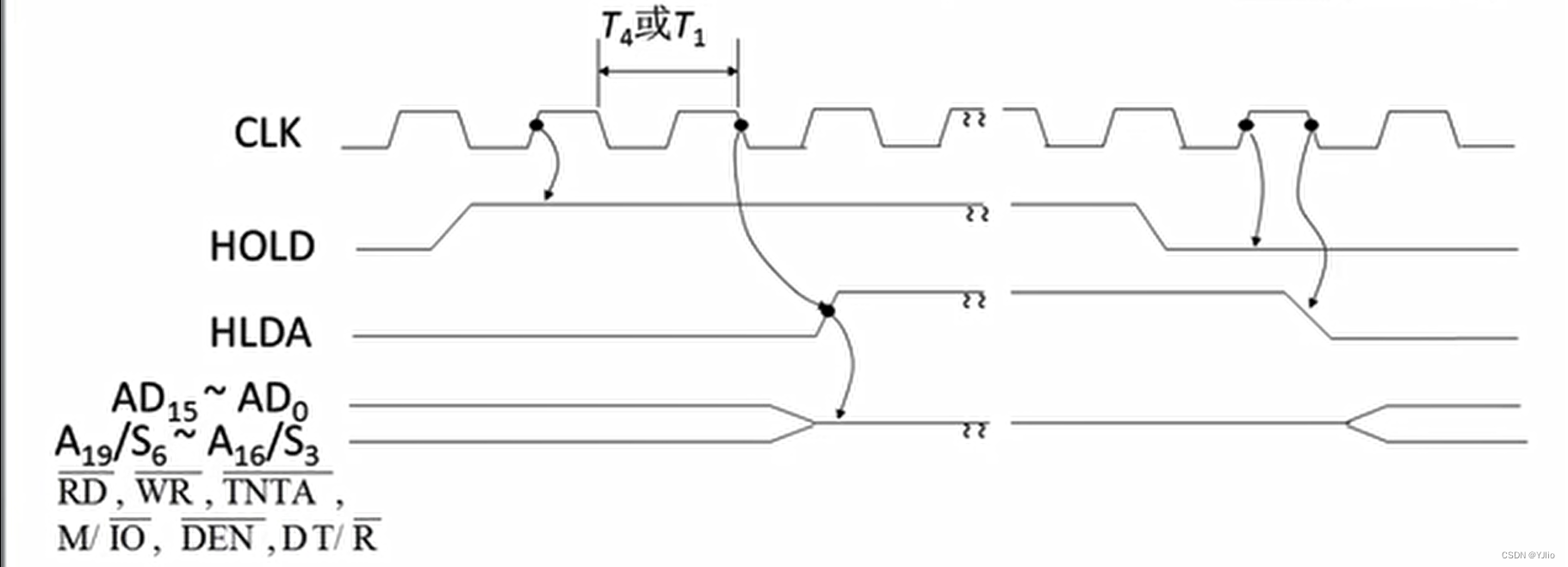

4.总线请求和响应引脚

(1) HOLD

输入 请求总线 高电平

(2) HLDA

输出 响应总线【总线】 高电平

5其它引脚

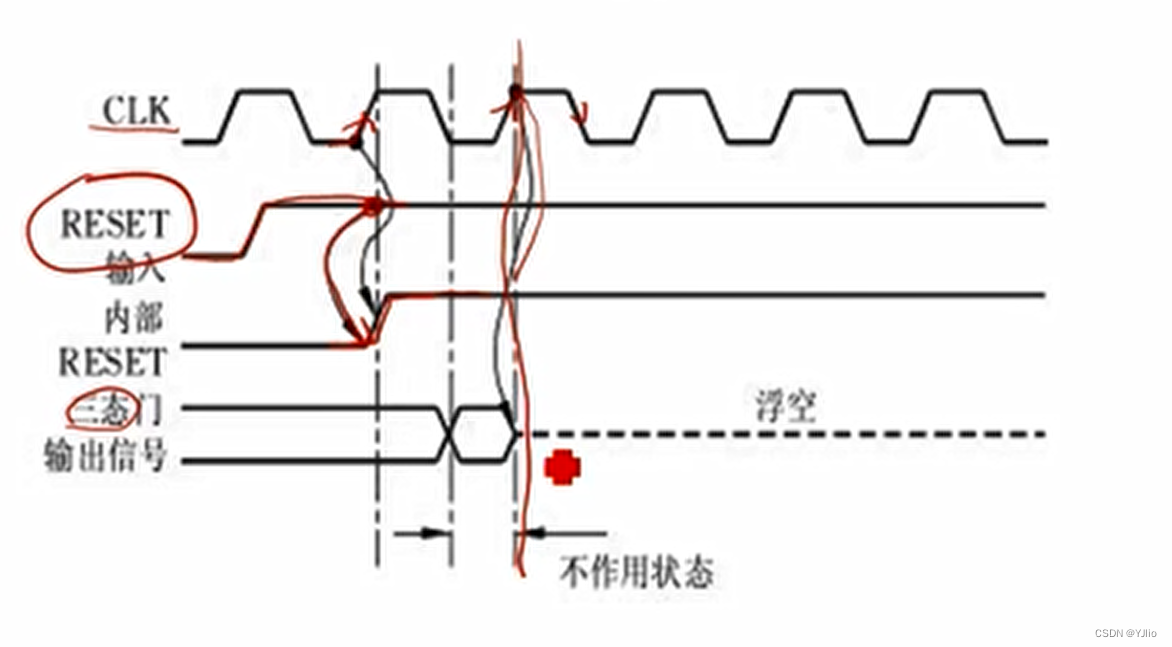

RESET

启动 用于CPU复位 CS:IP 值

CPU内部各位 清0 CS为全1

CLK (Clock)

Vcc:

电源

GND:

接地

MN/MX:

最小工作方式

最大工作方式

‘引脚”小结

AB DB CB

思考: 8088与8086区别:

8位 16位

引脚 24 28

指令队列 4B 6B

2.3 8088/8086 CPU两种工作模式的配置

一、两种工作模式(方式)

33号引脚 MN/MX =1(高电平时)工作在最大

=0(低电平)工作在最小

最小工作模式

构成单机系统,只有8088/86一片主处理器构成单机系统

最大工作模式

多机系统,除了88/86以外,还有协处理器

【协助浮点运算的8087芯片】

【协助I/O的8089芯片】

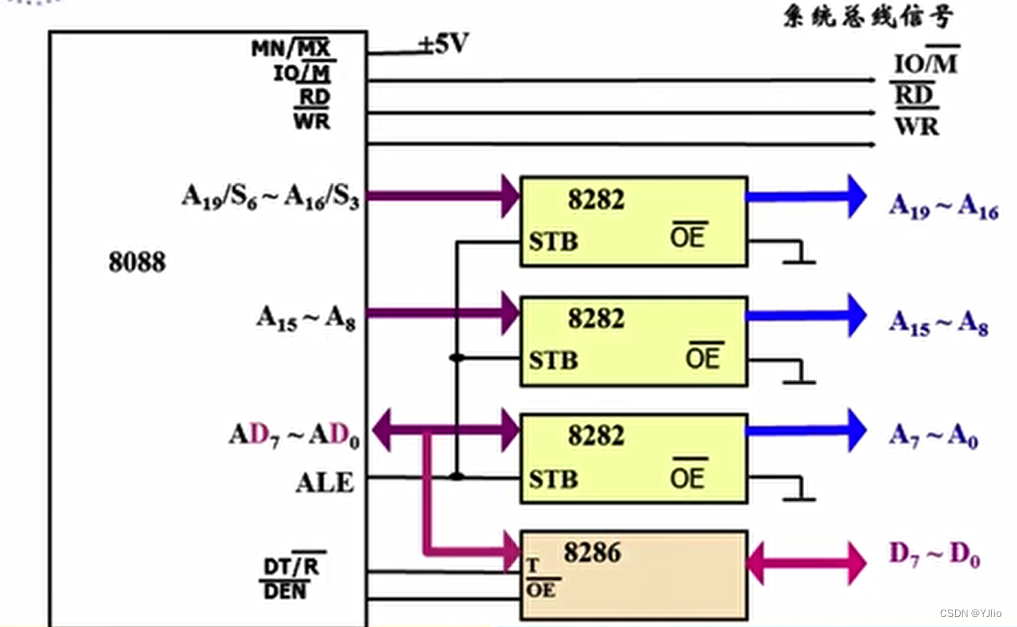

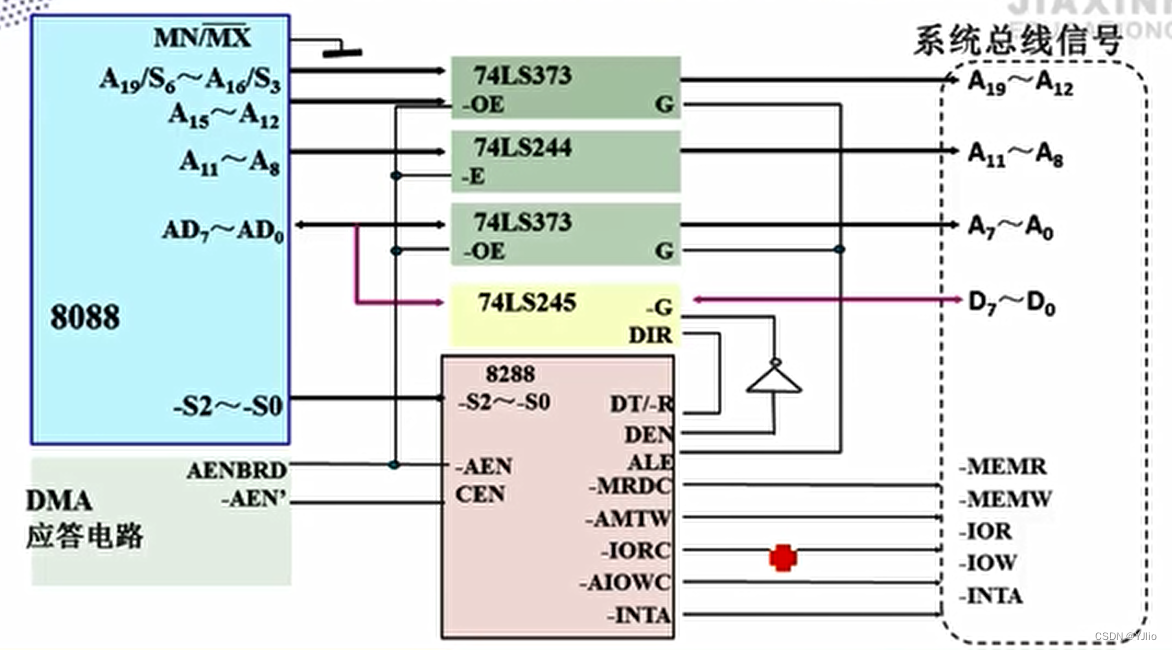

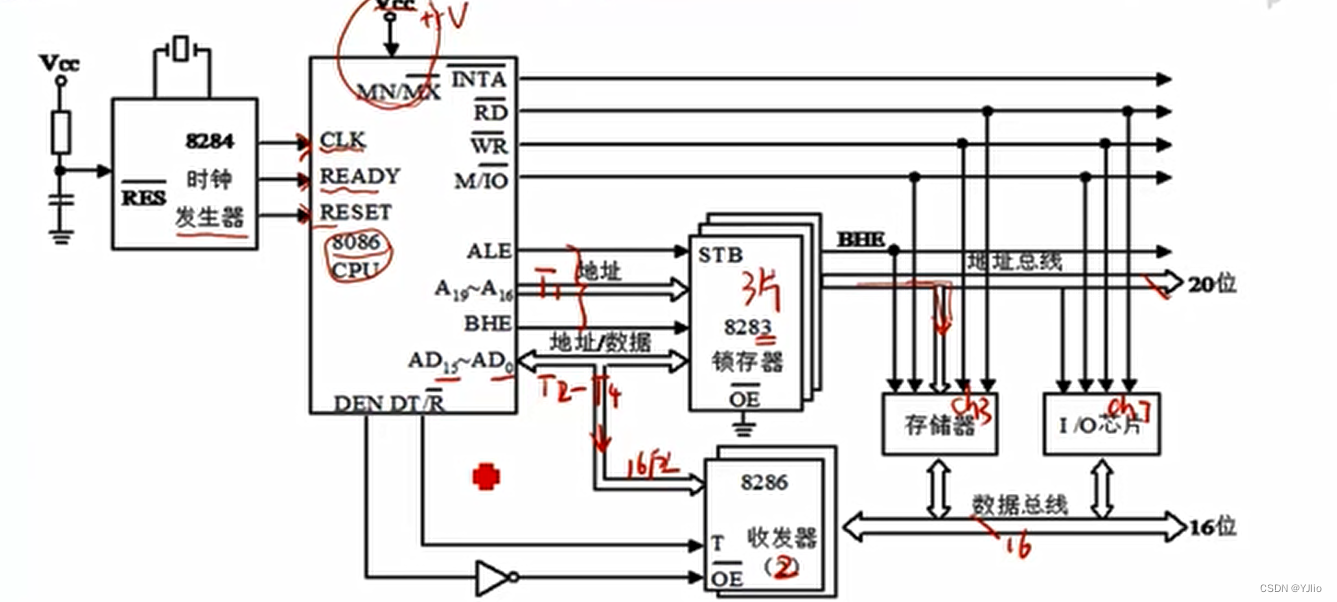

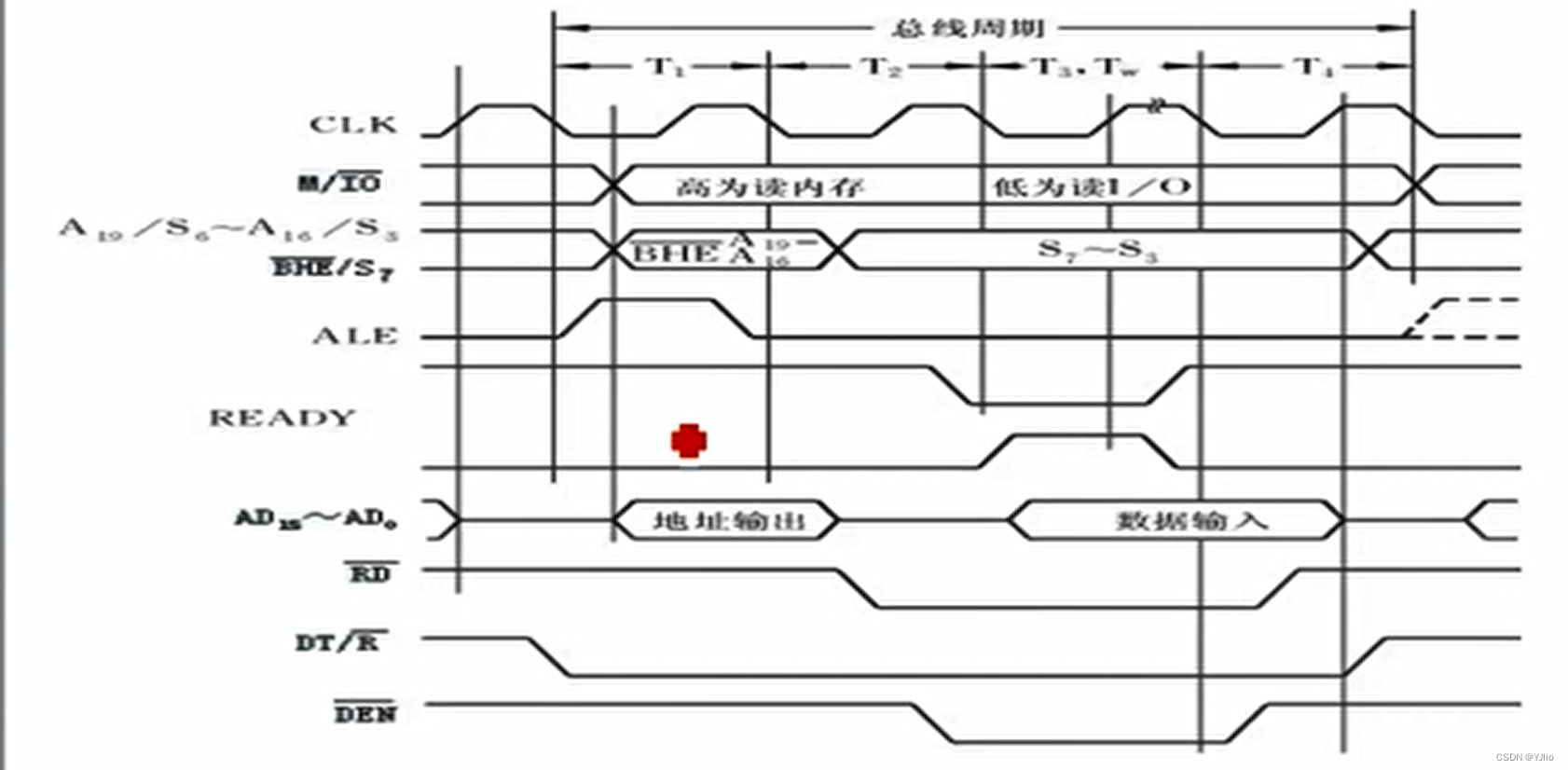

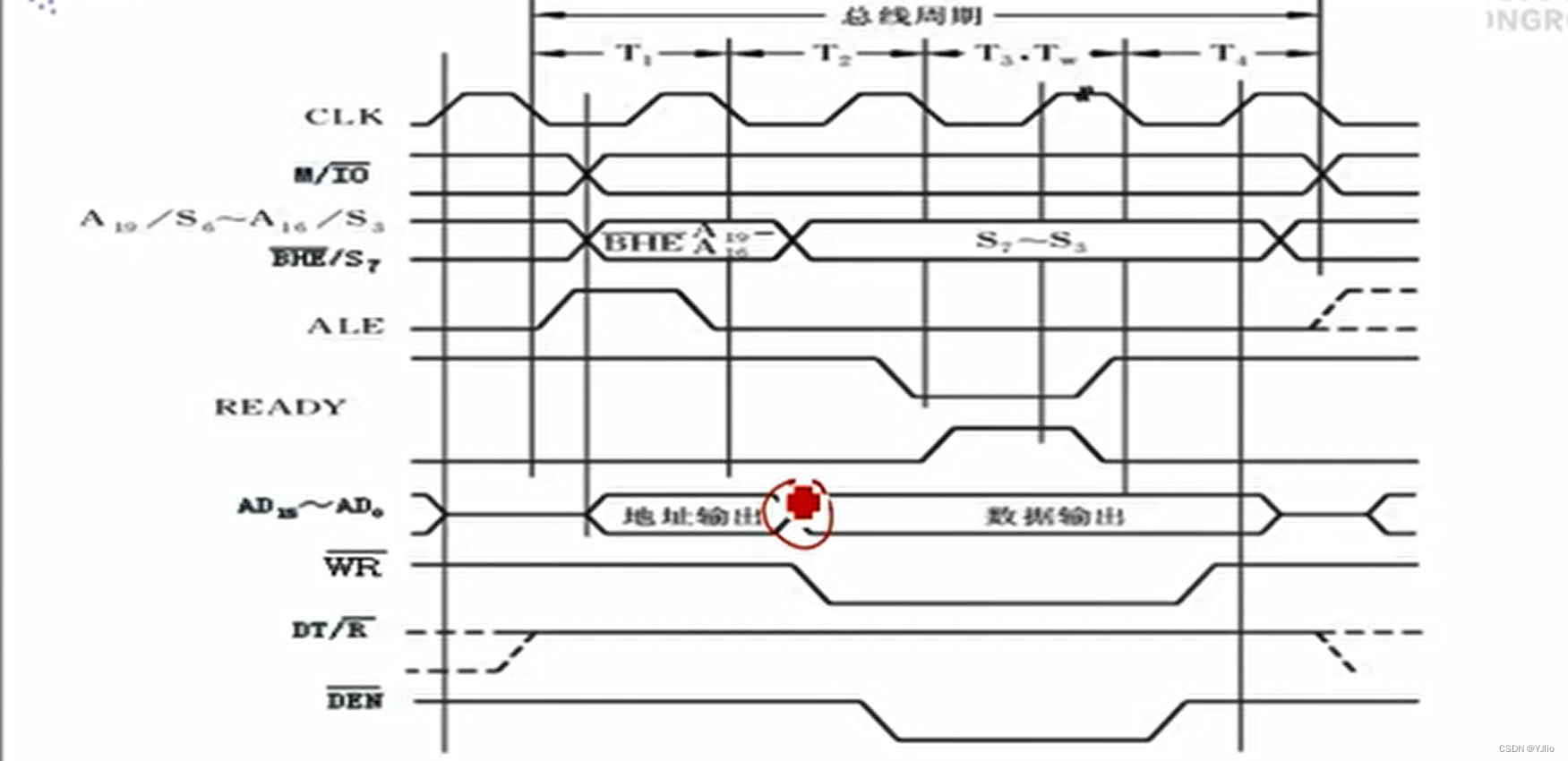

二、8088最小模式的总成线形成

一个88/86芯片,从AD0-AD7可以看出这是一个8088的芯片

如果是8086,因为8086的复用线为16为,故AD0-AD15

这张图按照 总线的类型划分,可以划分为三种,最上面的是 控制总线,中间的是地址总线

最下面的是数据总线 【数据总线是双向线 主存和IO接口 信息可以被CPU读进数据 从右向左】

8282芯片是地址锁存器

总结:8088最小模式的总线形成

1.20位地址总线的形成

需要 3片 8282 (地址锁存器【单向 三态线】【74Ls273,74ls373】,在ALE信号下)锁20位地址

2.8位数据总线的形成

需要1片8286(数据收发器 【双向 三态线】 T2-T4)传输数据

3. 系统控制信号的形成

由8088直接产生【读信号线 RD 写信号线 WR】

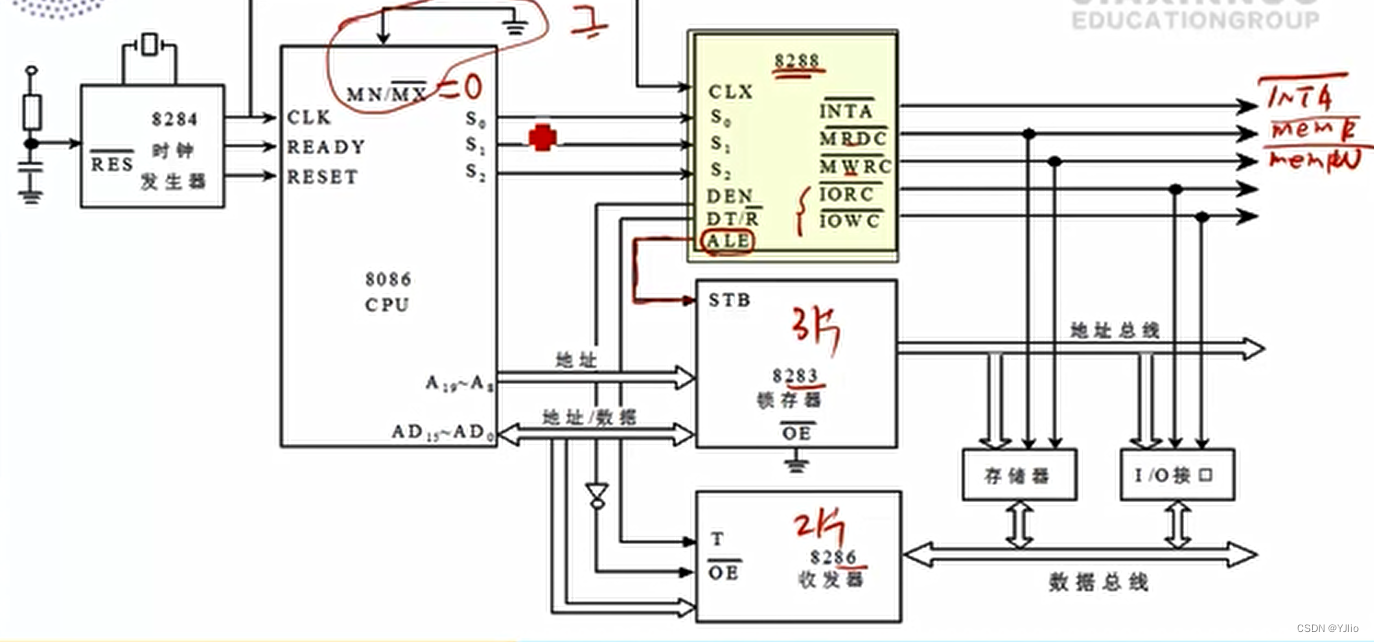

三、8088最大组态下的总线形成

总结:8088最大组态下的系统总线形成

特点:多机系统

2 MN/MX =0(低电平)

3 需要8288 产生控制总线

8289芯片总线仲裁器

四、8086最小组态下的总线形成

五、8086最大组态下的总线形成

总结:8088与8086系统总线形/成比较

1 AB DB CB

2 引脚:BHE对应,D8-D15

3 组成图:芯片的名字 8088/8086,8087,8089 8288 8289 8284 8282/8283【74LS373,273】8286 74L245,244

思考题

1.8086/8088工作模式分为____MN/MX _____

2.8086有最小和最大两种工作模式,最大模式的特点是 A B D

A.需要总线控制器8288

B.由编程进行模式设定

C.不需8286收发器

D. CPU提供全部的控制信号

2.4 8088/8086 CPU主要操作

时序(Timing):

CPU操作时间上的顺序

注意 T1 T2 T3 T4 TW,Ti

各引脚在时序上的有效时刻

一、基本概念

指令周期:

总线周期:

时钟周期:

等待状态:

空闲状态TI:

5个概念关系:

二、最小组态的总线时序

微处理器最基本的4种总线周期:

存储器读总线周期

存储器写总线周期

I/O读总线周期

1/0写总线周期

1. 8088系统存储器读总线周期

2.8088系统存储器写总线周期

3.8086系统读总线周期

4.8086系统写总线周期

三、启动/复位

86/88CPU的RESET引脚用来使CPU复位和启动。

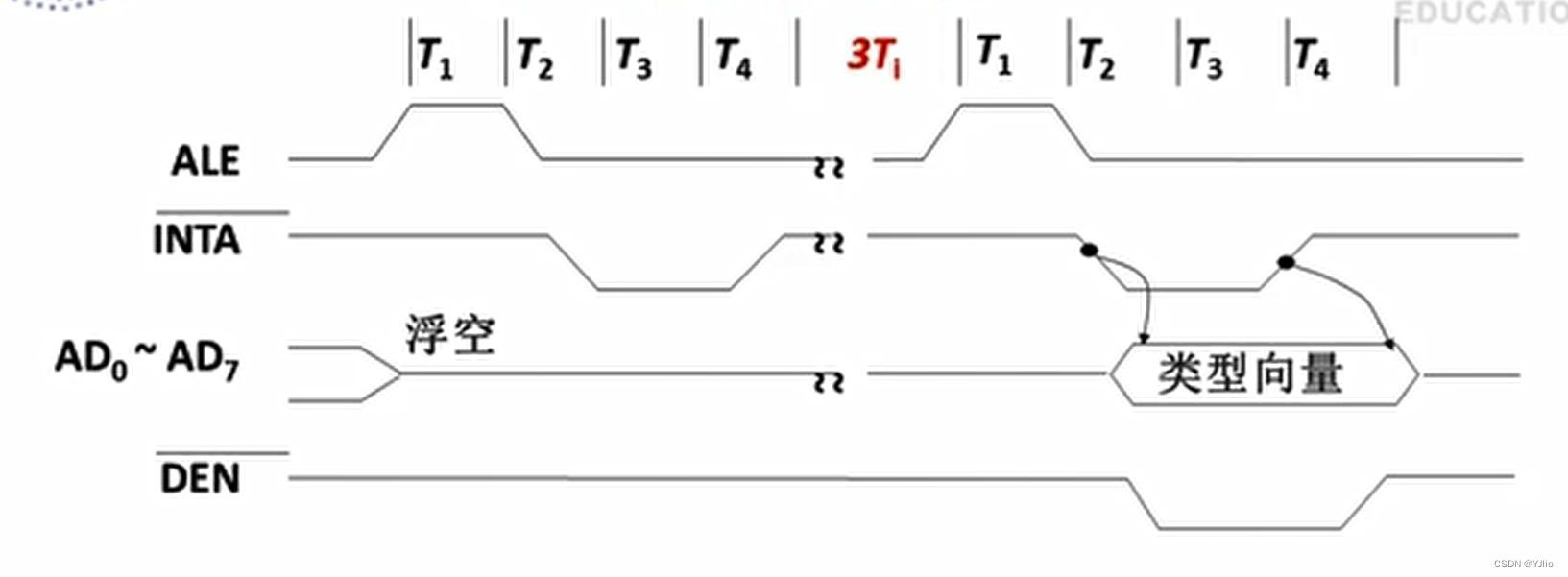

四、中断响应周期

五、总线请求/保持的时序

1. 8088/8086CPU的基本总线周期分为()个时钟周期。A. 6 B. 5 D. 3 C.4

2.8086CPU复位后,它的启动地址是()。

2.5 8088/8086中断系统

1. 深入理解中断的概念

2. 了解 8086 系统中断源的分类,

3.掌握8086CPU对它们的管理方法

4. 掌握中断全过程包含的步骤

5, 掌握 8086CPU 响应中断的条件及响应过程

6. 理解中断服务程序的一般构成

一、概念

1.中断:

中断请求、中断判优、 中断响应、中断处理、中断返回

、 2. 中断源:

软中断,硬中断

3.中断类型

256种【内中断 软中断】

【外中断 外设引发的中断】

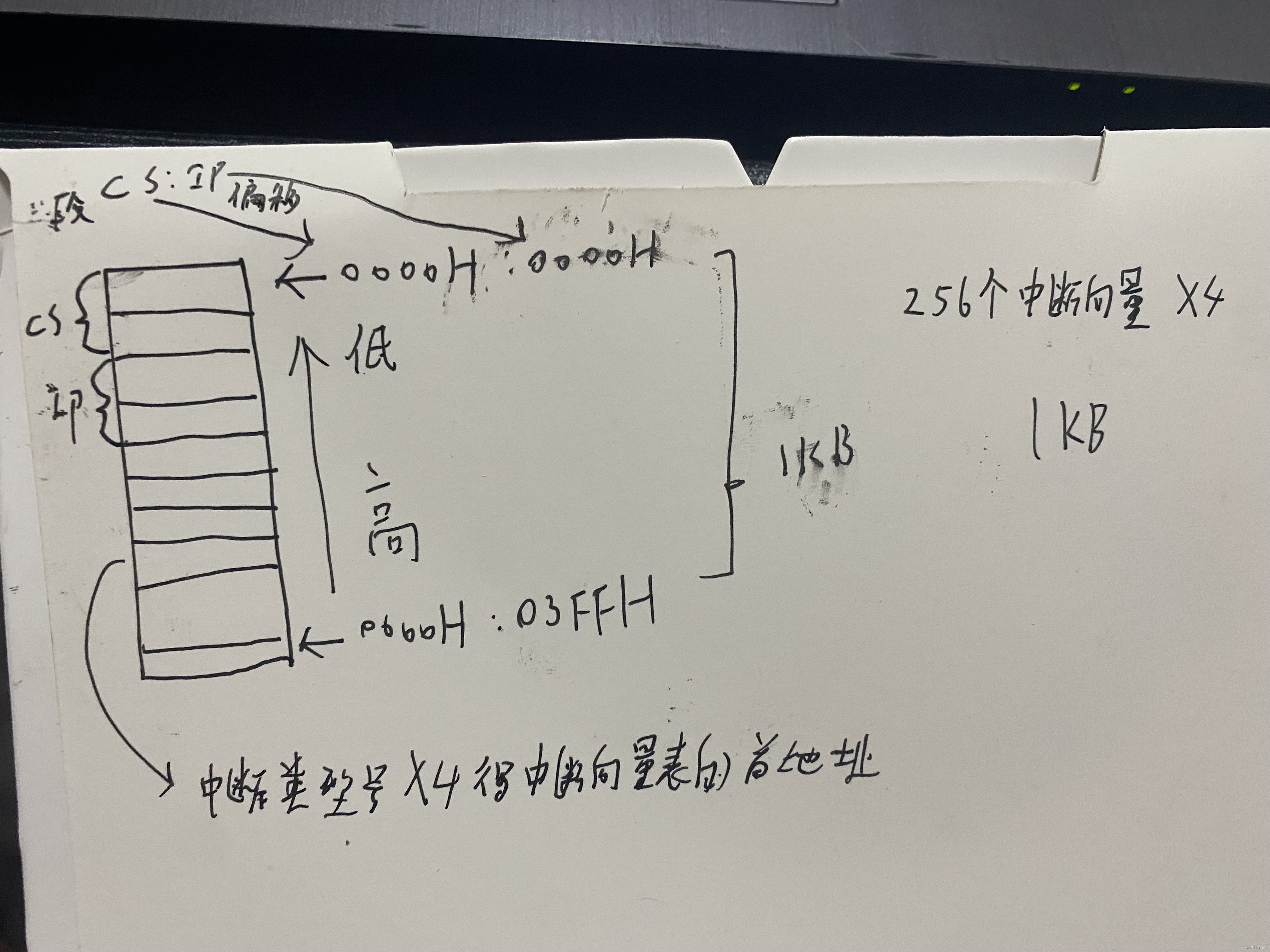

4.中断类型号(中断向量号):

0~255【01234n型】

00~FFH

INT 21H 【DOS功能中断】

5.中断向量:

中断服务子程序的入口地址:用CS:IP表示

每一个中断向量用4个字节(2个字)

保存于内存的中断向量表中

6.中断向量表:

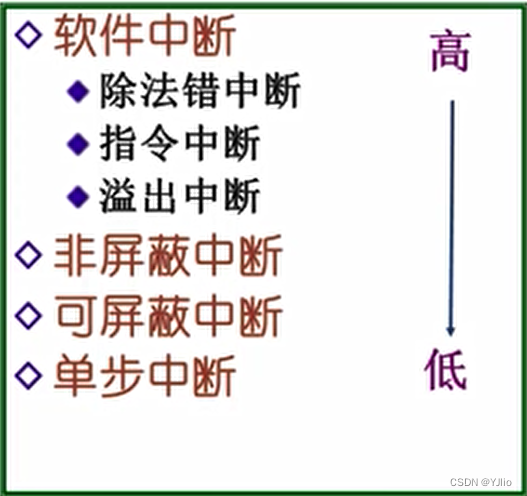

二、中断类型

1.内部中断

(1)除法错中断:向量号为0

(2)指令中断:向量号为n

(3)断点中断:向量号为3

(4)溢出中断:向量号为4

(5)单步中断:向量号为1

2.外部中断

INTR 可屏蔽中断

NMI 非可屏蔽中断

三、中断优先级

1型 单步中断 用TF表示 中断优先级最低

四、中断过程

思考题:以可屏蔽中断为例,说明一次完整的中断过程主要包括哪些环节?

中断请求:

中断响应:

关中断:

断点保护:

中断源识别:

现场保护:

中断服务:、

恢复现场:

开中断:

中断返回:

中断响应过程

①取中断类型号N。

②标志寄存器入栈。

③ 清除IF和TF标志。

④CS和IP入栈。

⑤获取中新向量。

1.8088/8086中断源最多可以为(C)。A. 254 B. 255 C. 256 D. 257

在8088/8086微处理器中,中断源的数量可以最多为256个,所以正确答案是选项 C. 256。这是因为8088/8086使用8位中断向量,所以可以有2^8 = 256个不同的中断源。2.8086/8088CPU响应可屏蔽中断的条件是什么?(B)

A. INTR=1, IF=1

B. INTR=0, IF=1

C. INTR=1, IF=0.

D. INTR=0, IF=0

8086/8088 CPU 响应可屏蔽中断的条件是

B. INTR=0, IF=1。在这个条件下,CPU 允许中断,但仅当外部中断请求信号 INTR 为低电平(0)时才会响应中断。同时,IF 标志位必须设置为 1,表示中断允许。存放中断向量的内存空间被称为————————中断向量表

存放中断向量的内存空间通常被称为"中断向量表"(Interrupt Vector Table)或简称"中断表"。这是一个用于存储各种中断和异常的地址向量的数据结构,当特定的中断事件发生时,处理器会根据中断号或异常码来查找相应的向量地址,以便跳转到相应的中断服务程序或异常处理程序。中断向量表在计算机体系结构中非常重要,它允许操作系统和硬件与各种中断事件进行交互,从而实现响应和处理不同类型的中断。不同的计算机体系结构和操作系统可能会有不同的中断向量表的实现方式和结构。4.8086/8088系统中内存的最低1KB,即O段_________到__________的到建立看中断向量表。

8086/8088系统中内存的最低1KB,即O段(0x00000)到中断向量表(0x003FF),用于建立和存储中断向量表。