FPGA/IC笔试——紫光展锐

一、单选题(共26题,每题2分,共52分)

1.[单选题]Verilog语言与C语言的区别,不正确的描述是( C )

A.Verilog语言可实现并行计算,C语言只是串行计算;

B.Verilog语言可以描述电路结构,C语言仅仅描述算法;

C.Verilog语言源于C语言,包括它的逻辑和延迟;

D. Verilog语言可以编写测试向量进行仿真和测试。

2.[单选题]数据位宽8bit,地址位宽13bit的RAM,其大小为多少?B

A.4KB

B.8KB

C.16KB

3.[单选题]以下哪些是第三代移动通信标准(B)

A.EDGE

B.TD-SCDMA

C.LTE

D.WiFl

解析:W-CDMA(宽带码分多址接入)、CDMA2000(码分多址接入)和TD-SCDMA (时分同步码分多址接入),WiMAX是继W-CDMA、CDMA2000、TD-SCDMA后的第四个3G标准。

4.[单选题]linux下,删除文件命令 B

A.mkdir

B.rm

C.mv

D.del

5.[单选题]在verilog中,以下不属于分支语句的是( C )

A.case

B.if-else

C.repeat

D.casaz

6.[单选题]一个八位D/A转换器最小电压增最为0.011V,当输入10011100时,输出电压为( D )V。

A.1.28

B.1.45

C.1.54

D.1.56

7.[单选题]在verilog HDL的always块语句中的语句是如何执行的( D )

A.顺序

B.并行

C.顺序或并行

D.不一定

8.[单选题]以下哪个不是异步处理的通用方法 D

A.synchronizer

B.fifo

C.handshake protocol

D.sampling by DFF

9.[单选题]Verilog HDL中信号没有定义数据类型时,缺省为什么数据类型 B

A.reg

B.wire

C.tri

D.Z

10.[单选题]项目后仿阶段,不需要哪个文件? D

A.标准单元库

B.网表

C.SDF

D.RTL

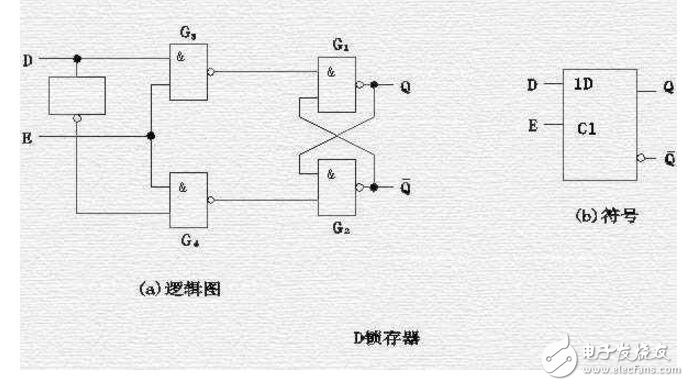

11.[单选题]How many logic gates(only NAND and NOT gate)used in a D latch?(B)

A.4

B.5

C.6

D.7

12.[单选题]以下对hold timing有帮助的是

A.提高时钟频率

B.降低时钟频率

C.提高工作电压

D.降低工作电压

13.[单选题]以下哪项工作需要手工进行门级设计?C

A.行为级描述

B.综合

C.ECO

D.验证

解析:工程变更(Engineering Change Order)

14.[单选题]At which level is STA usually done?C

A.Behavior Level

B.Register Transfer Level

C.Gate Level

D.没拍到不重要

15.[单选题]In Verilog_hdl,a=4'b1011,so &a=?(D)

A.4'b1011

B.4'B1111

C.1'b1

D.1'b0

16.[单选题]'timescale 1ns/1ps

fork

begin #1;end

begin #2;end

join_none

Sdisplay($time);

上述代码中需要等待多长时间?

A.1ns

B.2ns

C.3ns

D.4ns

解析:0ns

17.[单选题]下列语句( D )不能在module中独立存在。

A.task

B.initial

C.always

D.forever

18.[单选题]CMOS工艺中,PMOS的衬底连接;A

A.VDD

B.GND

C.Source

D.Drain

19.[单选题]A=(0.8125)10,十进制转二进制,则A=(A)

A(0.1101)2

B.(0.0101)2

C.(0.1011)2

D.(0.1111)2

20.[单选题]运算assign SUM=a[7:0]+b[7:0] +c[7:0] +d[7:0]+e[8:0],为了SUM没有溢出,SUM的位宽最小为多少 B

A.10

B.11

C.12

D.13

解析:

方法一:将两两分组,优先位宽一样的一组,则该组和位宽+1;题中a、b和9bit,c、d和9bit;然后前面的1个9bit和再与e的和为10bit;最后10bit再和另外一组9bit相加,结果11bit。

方法二(最大值代入):8bit取255,9bit取511,则255*4+511=1531<2048,即11bit。

21.[单选题]下列描述中采用时钟正沿触发且reset异步下降沿复位的代码描述是 C

A.always@(posedge clk or negedge reset) if(reset)

B.always@(posedge clk or reset) if(!reset)

C.always@(posedge clk or negedge reset) if(!reset)

D.always@(negedge clk or posedge reset) if(reset)

22.[单选题]组合逻辑电路通常由( B )组合而成

A.记忆元件

B.门电路

C.计数器

D.以上都对

23.[单选题]以下哪个不是Verilog的keyword?(C)

A.input

B.assign

C.write

D.module

24.[单选题]APR最终输出什么数据给Foundary?A

A.GDS

B.DEF

C.Verilog

D.SPEF

解析:APR (自动布局布线,也就是从 floorplan →布局→布线)。

物理版图以 GDSII 的文件格式交给晶圆厂(Foundary)。

25.[单选题]假设在CRC校验中使用的生成多项式是G(X)=X^3+X+1,4位的原始报文为1010,求编码后的报文(A)

A.1010 011

B.1010 000

C.1011 011

D.1011 000

解:

(1)将生成多项式G(X)=X^3+X+1转换成对应的二进制除数1011。

(2)此题生成多项式有4位(R+1)(注意:4位的生成多项式计算所得的校验码为3位,R为校验码位数),要把原始报文C(X)左移3(R)位变成1010 000

(3)用生成多项式对应的二进制数对左移3位后的原始报文进行模2除(高位对齐),相当于按位异或 得到的余位011,所以最终编码为:1010 011

26.[单选题]AXI4不包括下面哪个接口信号 (C)

A.AWID

B.ARID

C.WID

D.RID

二、多选题(共15题,共48分)

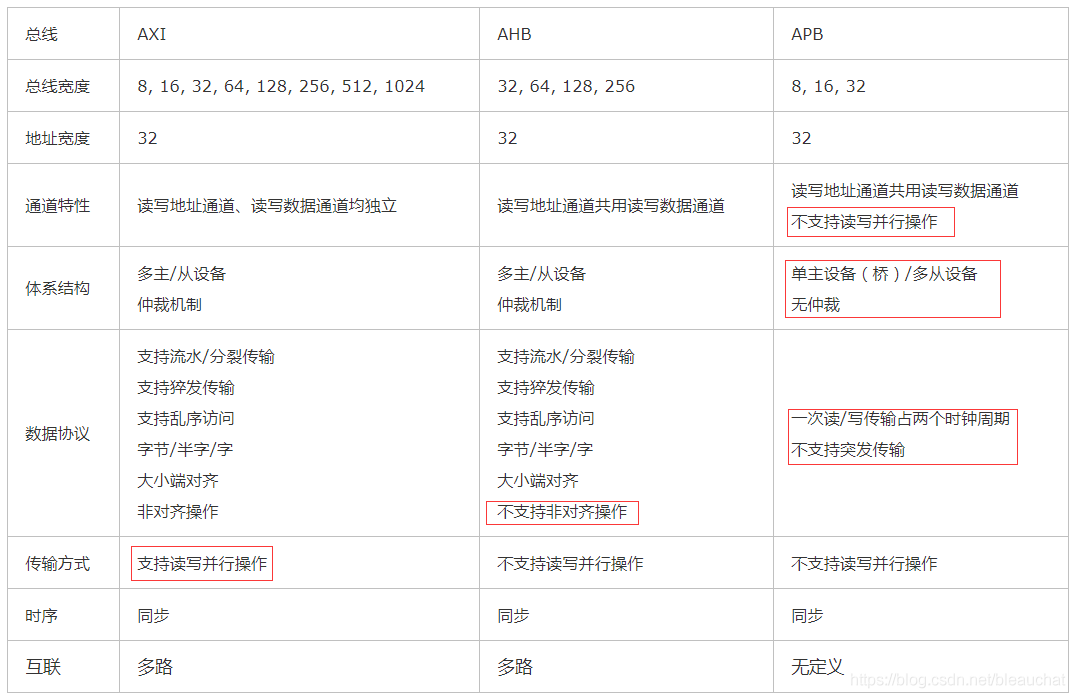

1.[多选题]下面哪些是AHB的特性 ABCD

A.split transaction

B.burst transfer

C.non-tristate implementation

D.out-of-order data transmission

解析:非三态的实现方式;支持突发传输;支持分段传输;支持多个主控制器;

2.[多选题]请选出以下能实现burst传输的片内总线(BD)

A.APB

B.AHB

C.SPI

D.AXI

3.[多选题]以下同步逻辑电路和异步逻辑电路描述正确的是(BD)

A 同步逻辑电路是时钟之间没有固定的因果关系,异步逻辑电路是各时钟之间有固定的因果关系

B 同步逻辑是由时序电路(寄存器和各种触发器)和组合逻辑电路构成的电路,其所有

的操作都是在严格的时钟控制下完成的。

C 异步逻辑电路不同时钟域之间不需要进行时钟同步

D 异步逻辑可能存在多个时钟信号,或者不存在时钟信号,电路中一个逻辑的变化就会

引起整个电路逻辑的变化。

4.[多选题]请找出以下总线中的串行总线(BCD)

A.AXI

B.SDIO

C.UART

D.IIC

5.[多选题]超大规模集成电路设计中,为了高速设计,采取以下哪些措施(AB)

A.流水线设计

B.并行化设计

C.资源共享

D.串行化设计

6.[多选题]Verilog与其他编程语言有哪几种接口机制?(AB)

A.PLI

B.DPI

C.NPI

7.[多选题]UPF描述了以下哪些信息(ACD)

A.power distribution architecture

B.power data

C.power strategy

D.usage of special cell

8.[多选题]芯片设计关注的PPA具体指哪几个方面?(ABD)

A.Performance

B.POWER

C.Architecture

D.Area

9.[多选题]下列哪些方式可以减少亚稳态问题的影响(BCD)

A.提升系统时钟频率

B.用反应更快的FF

C.架构上增加data toggle rate

D.改善时钟质量

10.[多选题]低功耗电路实现的方法有(AC)

A.降低工作电压

B.增加负载电容

C.降低电路面积

D.尽可能提高电路性能

11.[多选题]代码覆盖率主要包含(AB)

A.行覆盖率

B.条件覆盖率

C.toggle覆盖率

D.功能覆盖率

12.[多选题]下列关于Setup/Hold Time说法正确的是?(AD)

A.如果DFF的Hold时间不满足,通常可以通过增加数据路径延时来解决

B.如果DFF的Setup时间不满足,通常可以通过增加数据路径延时来解决

C.如果DFF的Hold时间不满足,通常可以通过增加时钟路径延时来解决

D.如果DFF的Setup时间不满足,通常可以通过增加时钟路径延时来解决

13.[多选题]在验证中下列关于代码覆盖率描述错误的是(CD)

A.代码覆盖率包括语句覆盖率

B.代码覆盖率包括条件覆盖率

C.代码覆盖率包括功能覆盖率

D.代码覆盖率达到100%说明所有Bug已消除

14.[多选题]EDA验证中,下面哪种方式可以对时序进行检查(BCD)

A.即时断言

B.并发断言

C.建立时间约束

D.保护时间约束

解析:时序检查方式如下:

建立时间检查:建立时间检查会验证触发器时钟和数据引脚之间的时序关系,从而满足建立时间要求。

保持时间检查:保持时间检查可确保正在变化的触发器输出值不会传递到捕获触发器、并在捕获触发器有机会捕获其原始值之前重写(overwrite)其输出。

多周期路径:在某些情况下,两个触发器之间的数据路径可能需要一个以上的时钟周期才能传播通过逻辑。在这种情况下,这条组合逻辑路径会被定义为多周期路径(multicycle path)。

伪路径检查:当设计的功能运行时,某些时序路径可能不真实(或不可能)存在。在执行STA时可以将这些路径设置为伪路径(false path),这样就可以关闭这些路径。

半周期路径:如果设计中同时具有负边沿触发的触发器(有效时钟沿为下降沿)和正边沿触发的触发器(有效时钟沿为上升沿),则设计中可能存在半周期路径(half-cycle path)。

撤销时间检查(removal timing check)可确保在有效时钟沿与释放异步控制信号之间有足够的时间。

恢复时间检查(recovery timing check)可确保异步信号变为无效状态的时刻与下一个有效时钟沿之间的时间间隔大于一个最小值。

跨时钟域检查;多时钟检查。

断言的作用:易于调试,提供功能覆盖和模拟速度更快,确保验证完整性。

并发断言:基于时钟的,调度区间按assertion的调度区间,可以在过程块(always initial),模块(module),接口(interface),程序(program)中定义。

即时断言:基于事件的,本质不是时序关系,会立刻求值。进行检查。

15.[多选题]以下哪些是power special cell ( BCD )?

A.buffer

B.level shifter

C.power switch

D.isolation

解析:在低功耗多电压技术包括MSV, DVFS, AVFS和电源门控Power Gating技术中,为了正确的实现多电压或者某个电压域关断,需要特殊的单元,主要包括:

1. Isolation cells

2. Level shifter cells

3. Power switch cells

4. Always-on cells

5. Retention cells

6. Standard cells with PG (power and ground) pins

7. Memories and other IP with PG pins

16.[多选题]关于时序逻辑电路Pipeline设计说法正确是( ACD )?

A.Pipeline可以提高吞吐率

B.Pipeline可以降低单个任务的latency

C.Pipeline可以提高时钟频率

D.Pipeline需要对流水线进行切割,设计时要对流水线进行均衡,以保证时序的接近

参考资料:数字IC打工人