FPGA基础——时序相关概念

一、影响亚稳态产生的因素:

(1)对于时钟和数据信号,分析setup建立时间和hold保持时间

setup建立时间:在有效的时钟沿来临前,数据需要保持稳定的最短时间,简写为Tsu;

hold保持时间:在有效的时钟沿来临后,数据需要保持稳定的最短时间,简写为 Th;

(2)对于时钟和异步复位信号,分析recovery恢复时间和removal移除时间

recovery恢复时间:在有效的时钟沿来临前,异步复位信号撤销后保持稳定的最短时间;

removal移除时间:在有效的时钟沿来临后,异步复位信号有效保持的最短时间;

FPGA中亚稳态【Tsu建立时间】【Th保持时间】【Tmet决断时间】【recovery恢复时间】【removal移除时间】

二、电路内部的建立时间与保持时间

建立时间公式:Tcycle + Tskew > Tco + Tgate + Tsu;

保持时间公式:Thold + Tskew < Tc0 + Tgate

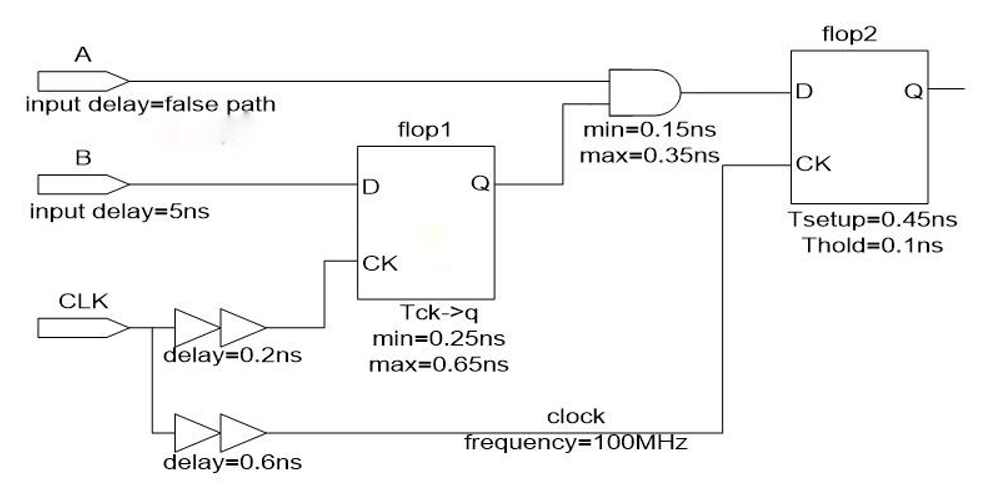

例1. 下图的电路中,flip-flop2 的setup time margin = ()ns

这个题目让求setup time margin,意思大概就是建立时间裕量,就是系统周期减去Tco,Tgate以及Tsu之后还可以有多少裕量,那,Tco,Tgate以及Tsu当然要用最大的来代入,因为要保证系统在最恶劣的情况下,能有多少裕量。

因此:Tsetup_margin = Tclk + Tskew - (Tco + Tgate +Tsu)

Tsetup_margin = 10ns + 0.6ns - 0.2ns - 0.65ns - 0.35ns - 0.45ns = 8.95ns

其中0.6ns - 0.2ns表示的是时钟偏斜量,可见是时钟正偏斜,有利于时钟裕量。

保持时间裕量 HoldSlack = Tcq+Tgate-Tskew-Thold

保持时间裕量 hold time margin = 0.25+0.15-0.6+0.2-0.1 = -0.1

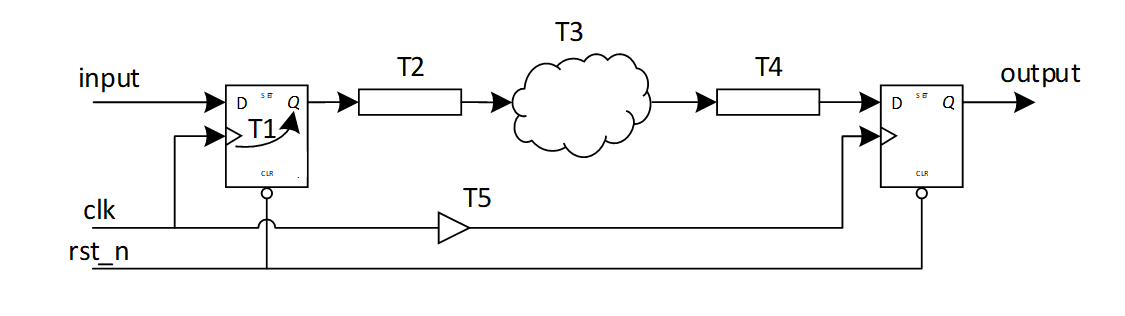

例2. 在同步电路设计中,电路时序模型如下∶T1为触发器时钟到输出延时,T2和T4为连线延时,T3为组合路径延时,T5为时钟网络延时,假设时钟周期为Tcycle ,Tsetup,Thold分别为触发器建立保持时间,为保证正确采样(改路径为multi-cycle路径),下列必须满足的是︰D

A.T1+T2+T3+T4<Tcycle-Tsetup+T5,T1+T2+T3+T4>Thold

B.T1+T2+T3+T4<Tcycle-Tsetup,T1+T2+T3+T4+T5>Thold

C.T1+T2+T3+T4+T5<Tcycle-Tsetup,T1+T2+T3+T4>Thold

D.T1+T2+T3+T4<Tcycle-Tsetup+T5,T1+T2+T3+T4> Thold+T5

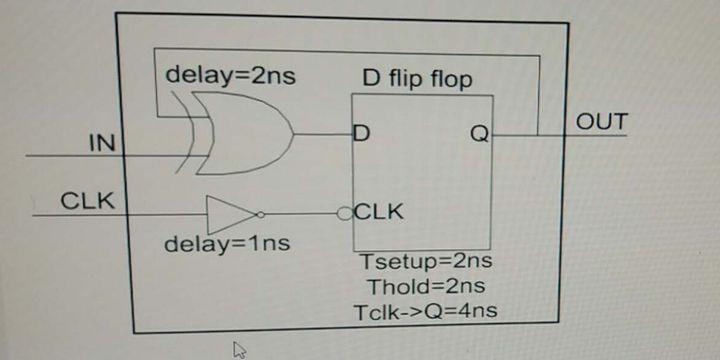

例3. 下图中的电路,器件延迟如图中标注,将框内的电路作为一个寄存器,其有效setup time = ? ns,hold time = ? ns

有效setup time分析:

对于D触发器而言,Tsetup = 2ns,也就是说数据信号需要提前时钟信号2ns到达触发器D端。

考虑时钟路径延迟, Tsetup_valid = Tsetup - 1ns = 1ns ;

在考虑数路径延迟: Tsetup_valid = Tsetup - 1ns +2ns = 3ns ;

有效hold time分析:

对于D触发器而言,Thold = 2ns,也就是说数据信号需要在时钟信号到达后保持2ns

考虑时钟路径延迟, Thold_valid = Thold + 1ns = 3ns ;

在考虑数路径延迟: Thold_valid = Thold + 1ns -2ns = 1ns ;

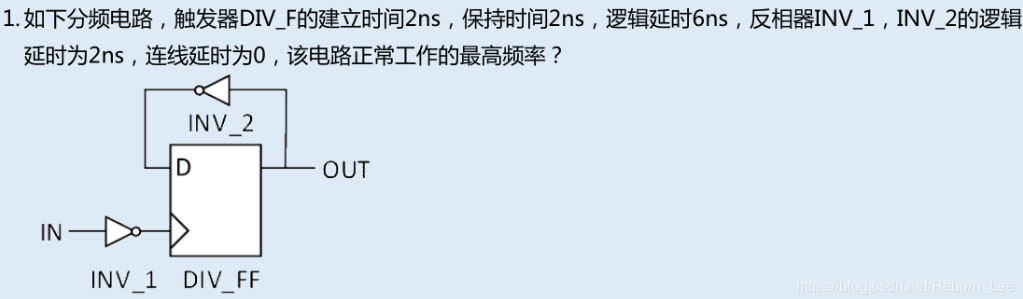

例4. 如下分频电路,触发器DIV_F的建立时间2ns,保持时间2ns,逻辑延时6ns,反相器INV_1,INV_2的逻辑延时为2ns,连线延时为0,该电路正常工作的最高频率?

这是一个触发器到自身的反馈,可以看做两个触发器之间进行数据传输。

需要明白的是,由于时钟到达这个触发器的时间一致,所以不存在时钟偏斜。

给出系统周期满足的关系:

Tcycle > Tco + Tgate + Tsu - Tskew = 6 + 2 + 2 - 0 = 10ns

所以时钟最大频率可以为100MHz。

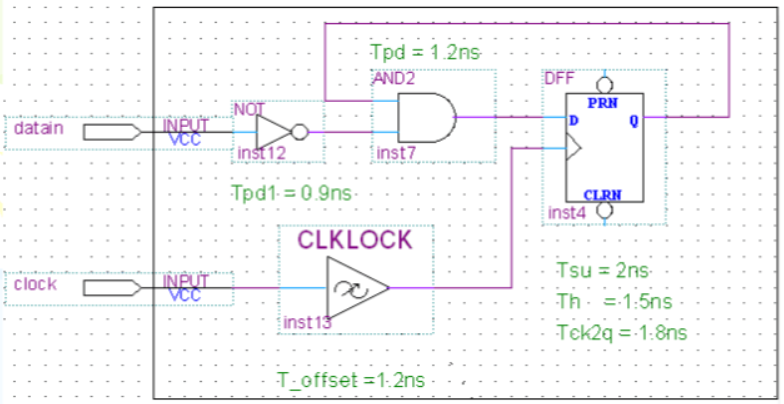

例5. 求该电路的固有建立时间与保持时间以及该电路的最高工作频率。

1. 求该电路的固有建立时间与保持时间?

求电路的固有建立时间和保持时间和上一题的有效建立时间和保持时间是一个意思的。因此:

固有建立时间为:Tsu_valid = Tsu - T_offset + Tpd + Tpd1 = 2 - 1.2 + 1.2 + 0.9 = 2.9ns

固有保持时间为:Th_valid = Th + T_offset - Tpd - Tpd1 = 1.5 + 1.2 - 1.2 - 0.9 = 0.6ns.

2. 该电路的最高工作频率?

先求系统的最小周期,考虑两个触发器之间的路径:

Tmin = Tco + Tpd + Tsu = 1.8 + 1.2 + 2 = 5ns,那么系统最高频率为200MHz。