FPGA/IC笔试——华为

1. 在Verlog HDL中对于initial语句,说法错误的是()

A. 在仿真过程中只执行一次

B. 可用于给实际电路赋初值

C. 在模拟的0 时刻开始执行

D. 多个 initial 块并行执行

答案:B

解析:

initial用于TestBench仿真赋值,无法用于实际电路赋值。

多个initial块在0时刻开始并行执行,只执行1次,且各自独立。

多个always多次执行。

此处需要说明:

对于FPGA,有些编译器是能够综合initial的,且在initial中给寄存器赋的初值,确实能够在实际电路中工作,下载到FPGA上是对的。对于 ASIC 设计中,initial不可综合。所以这里还是选了B,但是存疑。

Xilinx有的例程就是给的这种赋初值的方式,我自己写代码试了一下,确实能够综合并且布局布线。

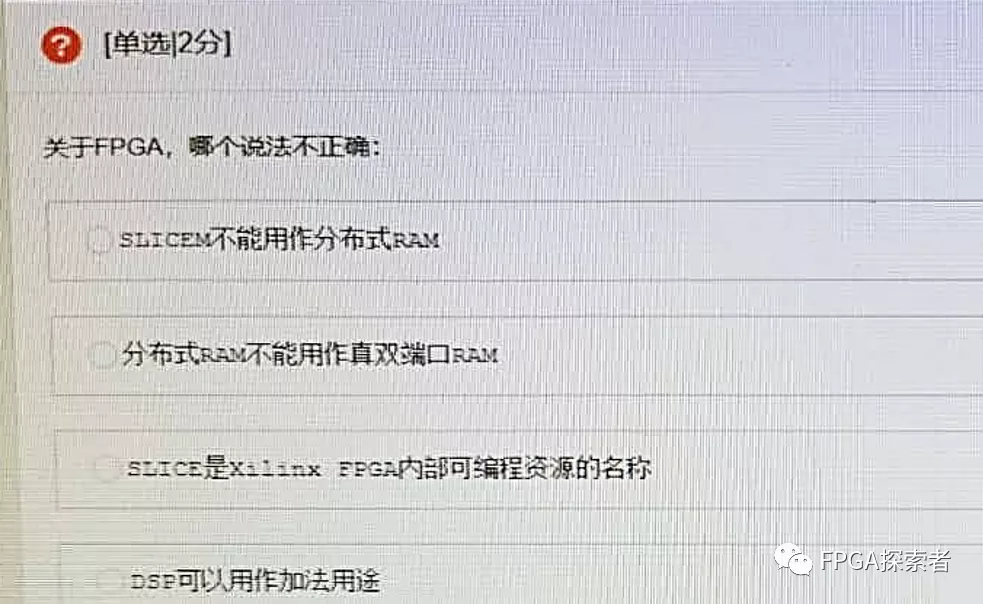

2. 关于FPGA,哪个说法不正确?【Slice】【分布式RAM】【DSP】

答案:A

解析:

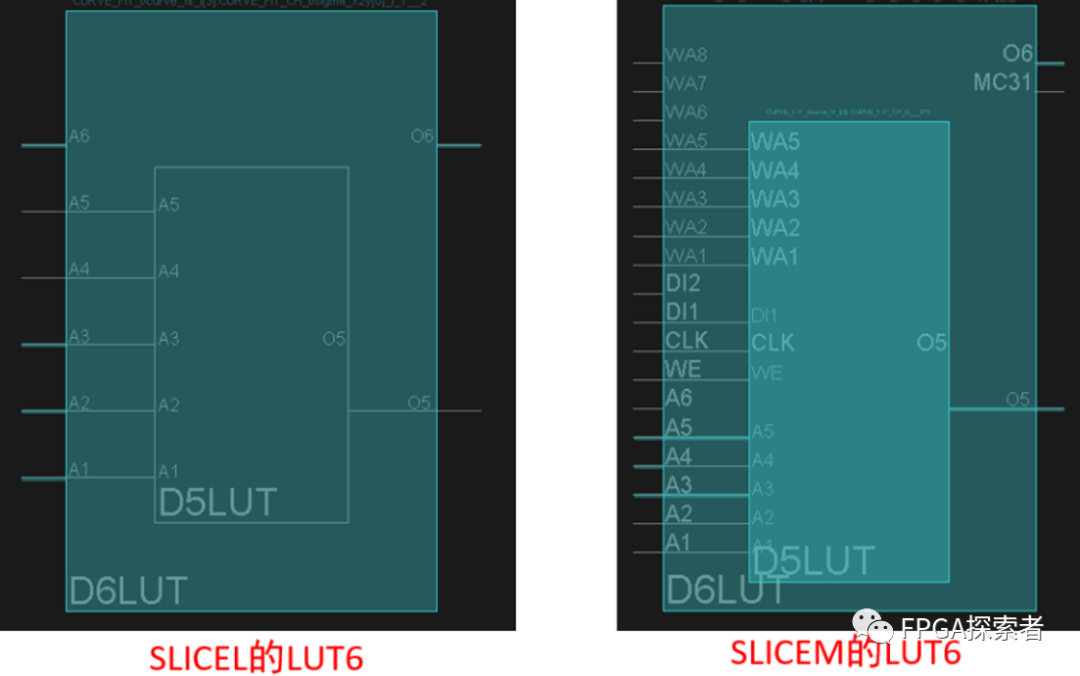

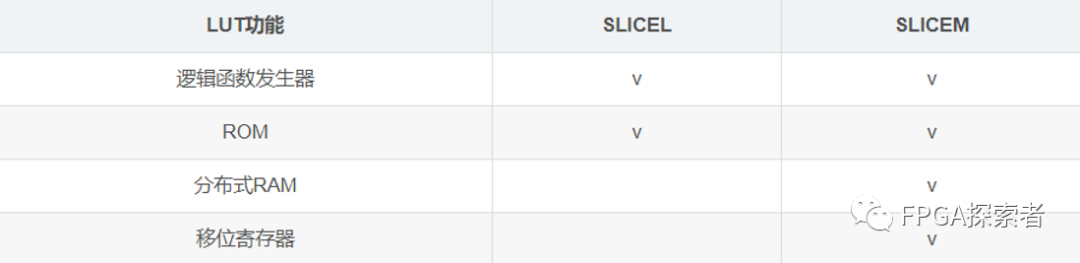

A:Xilinx 的 7 系列 FPGA 内部有 CLB 可编程配置块(Configuration Logic Block),每个 CLB 里有 2 个 Slice。Slice 有 2种,一种是 SliceL(Logic逻辑),一种是 SliceM(Memory存储),SliceM 相比 SliceL 多出的功能在于可以配置成 Distribute RAM(分布式RAM)。

B:分布式 RAM 不可以配置成真双端口RAM;

C:在前面提到,Slice 是 FPGA 内部的可编程资源;

D:DSP 主要是用于乘法、除法和快速加法;

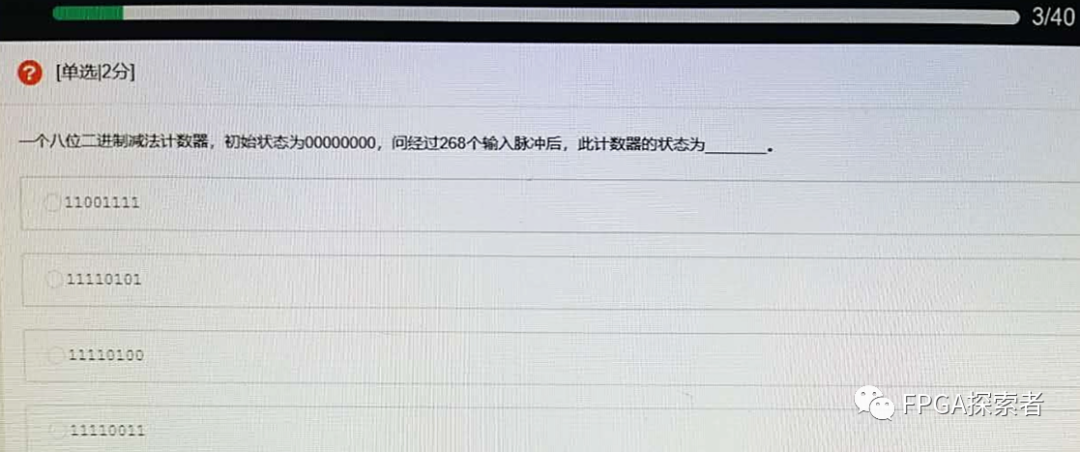

3. 一个八位二进制减法计数器,初始状态为00000000,问经过268个输入脉冲后,此计数器的状态为()【计数器】【减法计数器】【二进制减法】

答案:C

解析:

(1)8 位二进制,计数一周是 256 次(2^8),所以先输入256个脉冲,计数值从00000000回到00000000,此时还需要输入268-256=12个脉冲;

(2)再输入1个脉冲,减法计数,得到11111111,此时还需要输入11个脉冲;

(3)11111111是十进制的255,减去11是244,换算成二进制是 11110100;

第(3)步简便算:

11的二进制是0000_1011,在1111_1111中减去0000_1011,就是1111_0100。

4.当一根导线上的部分信号能量传输到相邻导线上时就出现了()的情形?【扇出fanout】【互调干扰】【串扰】【耦合】

答案:C 串扰

解析:

扇出:FPGA里面,扇出是一个输出端连接/驱动的后级资源的个数,比如驱动10个LUT查找表;

互调:由于器件的非线性,不同频率的信号互相调制,形成一个新频率信号;在通信中的接收机中常出现交调干扰和互调干扰,交调干扰是幅度失真,互调干扰是频谱失真;

串扰:一个信号的部分能量传输到相邻导线上,常出现在多路并行的高速传输线上,所以对于Gbps传输,常常使用 GT 高速串行收发器,而不采用并行(原因之一);

耦合:两个有依赖,彼此作用;

5. A='b0001,那么~A=('b1110)?【按位取反】【逻辑取反】

解析:

“~”按位取反,原来多少位,取反后还是多少位,A = ’b0001,那么~A = ’b1110;

“!”逻辑取反,结果是逻辑0或者逻辑1,1-bit,这里 A 不为 0,所以 !A = 1’b0,也可以写成 ’b0;

对于单bit信号,两个的结果没有区别,比如1-bit的复位,!rst_n 和 ~rst_n 的结果一样。

6. 已知信号f(t)的频带宽度为带塔w,则f(3t-2)的频带宽度为()

答案:A

知识点:【傅里叶变换性质】【尺度变换】【平移】【频谱】【时域压缩】【频域展宽】

解析:

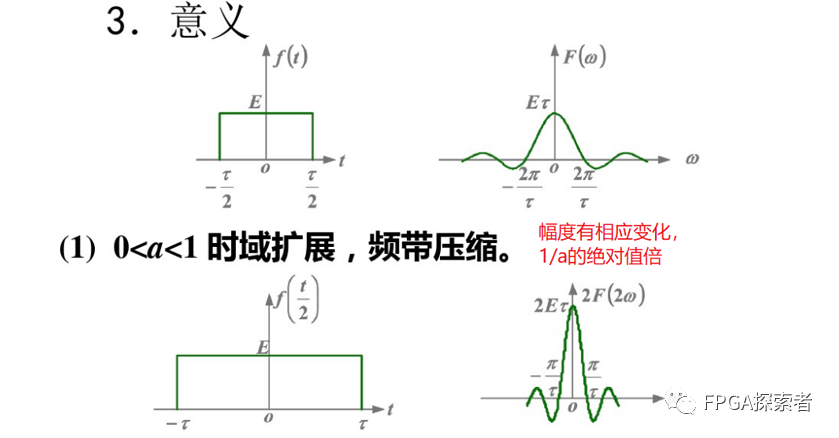

涉及到傅里叶变换的性质,包括平移和尺度变换,其中平移不影响频带的宽度,尺度变换影响频带宽度。

在一个域的扩展,对应另一个域的压缩,反之亦然。

这里,时域是变窄,压缩为原来的1/3,对应频域要展宽为原来的3倍。

7. 对于 D 触发器,若现态Qn=0,要使词条Qn+1=0,则输入D为(0)?

解析:D 触发器逻辑表达式Qn+1 = D,所以输入D为0,次态Qn+1=0。

8. 下列关于译码器描述错误的是()

答案:C

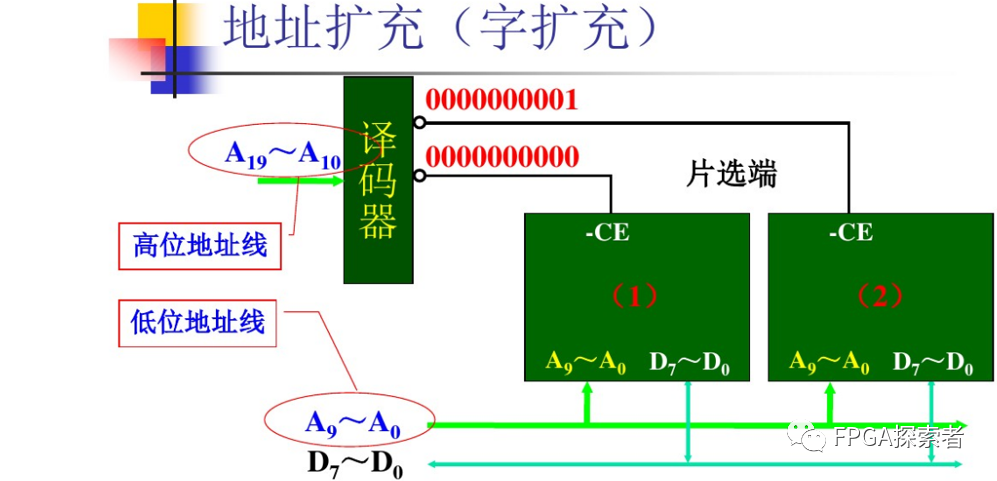

知识点:【译码器】【组合逻辑】【高位译码】

解析:

译码器,常见的3-8译码器,组合逻辑,可能会出现竞争冒险,不可以作为时序电路的时钟端。

对于B,高地址译码作为片选,低地址直接寻址,想具体了解的可以去看微机原理。

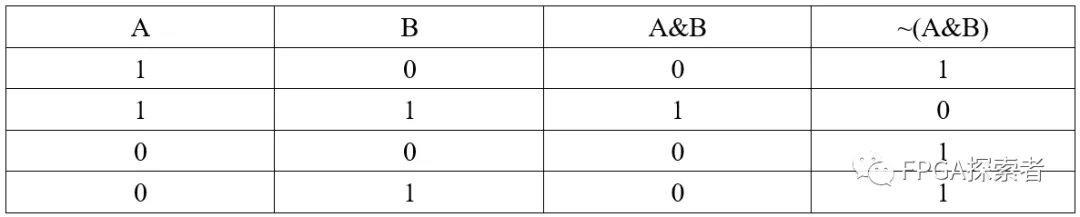

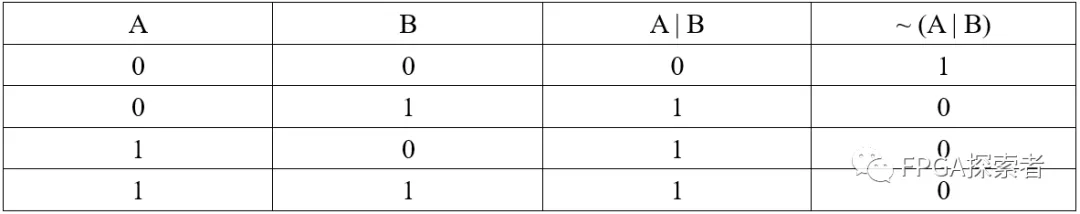

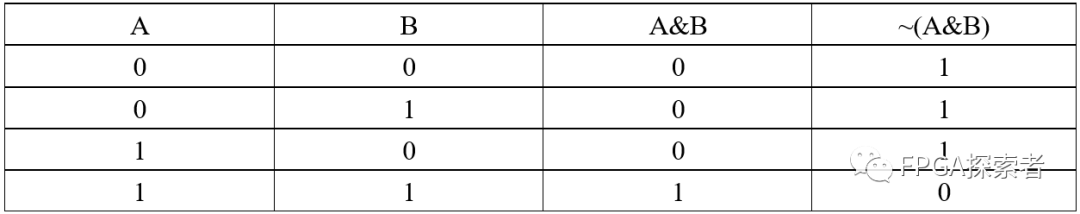

9. 在何种输入情况下,”与非“运算的结果是逻辑0?(全部输入1)

知识点【与非门】【或非门】

解析:

与非,2个输入A、B,输入A固定为1时,相当于非门;输入A固定为0时,相当于固定输出1。

A、B全为1的时候输出0,A、B中只有0就输出1。

或非门类似分析,一个输入接0时,相当于非门;2 输入全为0输出1,输入中只要有0输出就为1。

10. 异步控制信号在有效的时钟沿到达之前必须保持稳定的最短时间是指(recovery恢复时间)

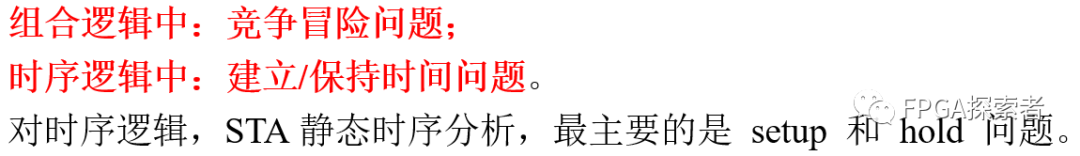

知识点:【STA静态时序分析】【setup建立时间】【hold保持时间】【recovery恢复时间】【removal移除时间】【异步复位】【时序】

解析:

(1)对于时钟和数据信号,分析setup建立时间和hold保持时间

setup建立时间:在有效的时钟沿来临前,数据需要保持稳定的最短时间,简写为 Tsu;

hold保持时间:在有效的时钟沿来临后,数据需要保持稳定的最短时间,简写为 Th;

(2)对于时钟和异步复位信号,分析recovery恢复时间和removal移除时间

recovery恢复时间:在有效的时钟沿来临前,异步复位信号保持稳定的最短时间;

removal移除时间:在有效的时钟沿来临后,异步复位信号保持文档的最短时间;

FPGA中亚稳态【Tsu建立时间】【Th保持时间】【Tmet决断时间】【recovery恢复时间】【removal移除时间】

11. Verilog中的标识符可以是任意一组字母、数字和_(下划线)的组合,单标识符的第一个字符不能是(数字)

解析:Verilog HDL中的标识符(identifier)可以是任意一组字母、数字、$符号和_(下划线)的组合,但标识符的第一个字符必须是字母或者下划线,标识符是区分大小写的。

12.判断以下哪个电路不是时序逻辑电路(B)

A.计数器

B.译码器

C.寄存器

D.状态机

解析:

时序逻辑电路特点:在任意时刻的输出,不仅取决于当前的输入,还取决于电路中原有的状态(组合电路+存储电路,能保存电路状态,比如寄存器)。

组合逻辑电路特点:输出仅取决于当前的输入。

显然,译码器是组合电路,计数器、寄存器、状态机是时序电路。

13.二输入与非门当输入变化为(C)时,输出可能有竞争冒险。

A.00—>10

B.10—>00

C.01—>10

D.11—>01

解析:2输入与非。

对A:00—>10,如果有延时产生,可能会出现00、10两种状态,输出均为1,没有输出冒险;

对B:10—>00,如果有延时产生,可能会出现10、00两种状态,输出均为1,没有输出冒险;

对C:01—>10,如果有延时产生,可能会出现01、00、10、11四种状态,输出本应该为1,但是可能会出现0(11状态),输出冒险;

对D:11—>01,如果有延时产生,可能会出现11、01两种状态,输出有延时,没有输出冒险;

14. 在设计一个15进制的计数器时,则至少需要(4)bits的状态变量?

解析:2^4 =16。

15. a=1'b1,b=5'h10,那么{a, b} = 6'h30

16. 多数时序问题,归根结底是(建立-保持时间)

知识点:【时序】【STA静态时序分析】【建立时间】【保持时间】【竞争冒险】

17. 下列表达式逻辑关系错误的是(D)

A. ~(x&y) = (~x) | (~y)

B. x|(y&z) = (x|y) & (x|z)

C. ~(x|y) = (~x) | (~y)

D. x&y&z = (x&y) | (x&z)

18. 在时序电路的状态转换表中,若状态数N=3,在状态变量数最少为(2)

解析:二进制或者格雷码编码,2^2 = 4,2和状态变量最多可以支持4个状态;

独热码编码,N个状态需要N个状态变量(3’b001,3’b010,3’b100)。

独热码(One-Hot),只有1位是1。

19. 下列几种 TTL 电路中,输出端可实现线与功能的门电路是()

A. 或非门

B. 异或门

C. 与非门

D. OC门

解析:线与:OC门和OD门。

OD门:漏极开路门(open-drain),直接线与

OC门:集电极开路(open-collector),必须接电源和上拉电阻

20. 在 Verilog HDL 中,定义变量并进行运算如下,在第9个时间单位结束后,x与y的值分别为(0,0)

解析:多个 initial块并行从时刻0开始执行。

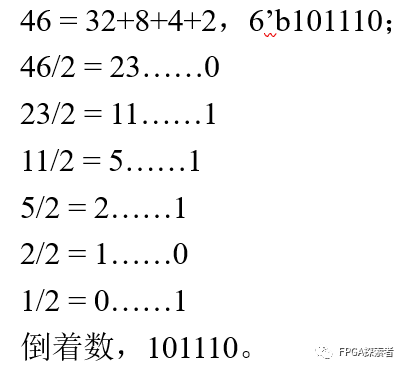

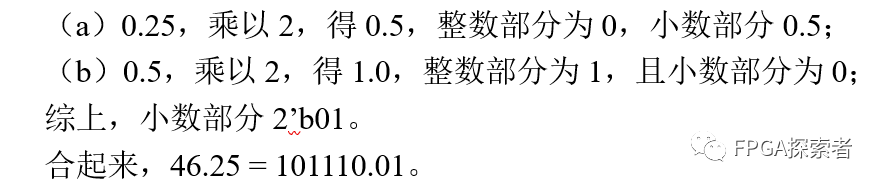

21. 十进制46.25对应的二进制表达式为(101110.01)

解析:十进制转换成二进制:

(1)整数部分:不断除以2,直到商为0,倒着取余数;

(2)小数部分:不断乘以2,直到积的小数部分为0,正着取整数部分。

22. 对于Intel(Altera)的FPGA,下面哪一个等级速率最快(-6)

解析:

Intel(Altera)的FPGA:-6/-7/-8,-6最快,-8最慢;

Xilinx的FPGA:-1/-2/-3,-1最慢,-3最快。

现在还有-1/-L1/-2/-L2/-3,L是低功耗Low power。

23. 集成运算放大器的一个结构特点是采用差动放大输入级,其目的是为了()

A. 抑制电源噪声

B. 提高放大倍数

C. 增强带负载能力

D. 抑制温漂

答案:D

知识点:【差动放大器】【共模抑制比】【温漂】

解析:

差动放大,也叫差分放大,相比直接放大,能抑制温漂(零漂)。

零点漂移:电压或者温度影响,集电极电流发生变化,相当于在2个输入端加入了共模信号。差分放大电路有很好的共模抑制比CMRR,即有很强的输出漂移抑制能力。

减少温漂的措施:1.用非线性元件进行温度补偿;2.调制解调方式;3.采用差分放大电路

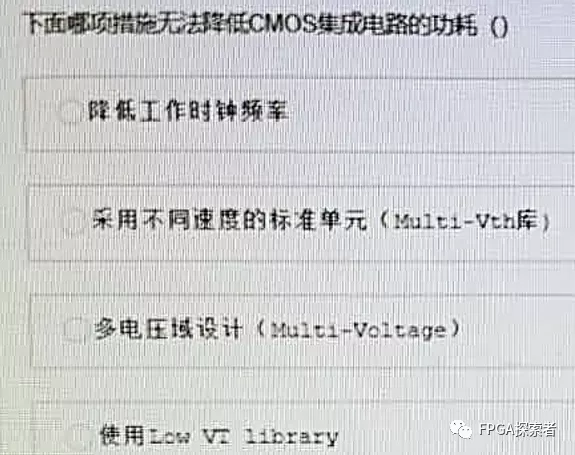

24.下面哪项措施无法降低CMOS集成电路的功耗?

解析:CMOS集成电路低功耗:

降频; 降压;多电压;多阈值;门控时钟;

D 中的 Low VT libaray,低阈值库,漏电流大,运算速度快,静态功耗大。

对于非关键路径,对延时不敏感,可以使用高VT(高阈值)的器件,则可以在满足时序的前提下,减小静态功耗。

25.在时序电路中,时钟频率为100M,计数器位宽为3bit,那么计数器的翻转周期是(80)ns?

解析:

100MHz 时钟对于 10 ns 时钟周期。

计数器位宽3-bit,8进制计数器,计8个时钟周期,80 ns。

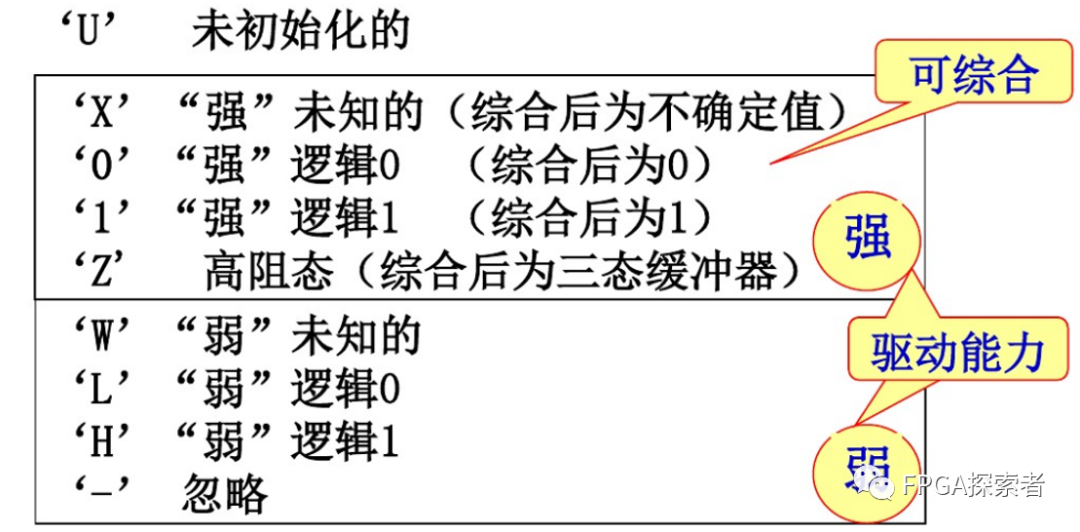

26. H和X分别别是哪种逻辑状态?(VHDL、Verilog)

解析:

在Verilog中,只有0、1、X、Z四种逻辑,其中X不定态,Z高阻态(X、Z不区分大小写)。

在VHDL中,H是弱逻辑1,X是不定态。

27. K=M&N,如果M为‘x’态,那么K为(x)态?

解析:

输入是X不定态(红线),输出就是X不定态。

输入是高阻态Z(蓝线)和0,输出是0;

输入是高阻态Z(蓝线)和1,输出是X不定态。

28. 属于组合逻辑的电路是(C)

A. 触发器

B. 移位寄存器

C. 全加器

D. 计数器

解析:

时序逻辑电路的特点:在任意时刻的输出,不仅取决于当前的输入,还取决于电路中原有的状态(组合电路+存储电路,能保存电路状态,比如寄存器)。

组合逻辑电路特点:输出仅取决于当前的输入。

全加器、译码器、编码器是组合电路;计数器、寄存器(触发器)、移位寄存器、状态机是时序电路。

29. {3{4'b1011}} = (12'b1011_1011_1011)

30. 加减、积分、微分、乘除等模拟运算电路要求集成运放工作在()状态?

A. 正反馈

B. 虚断

C. 线性放大区

D. 负反馈

答案:C

知识点:【集成运放】【线性放大区】【负反馈】

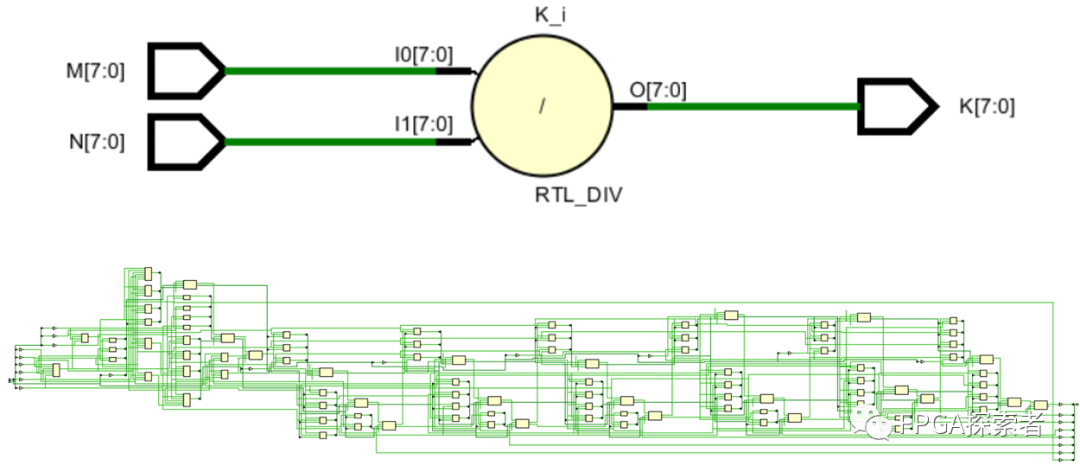

31. 在Verilog HDL中,下面哪个是在RTL代码中不可以直接使用的运算符()

A:异或"^"

B:除法"/"(最好是调用除法器IP)

C:或运算"|"

D:加法"+"

除法在综合和布局布线后,可以看到,是利用很多LUT和进位链搭出来的。

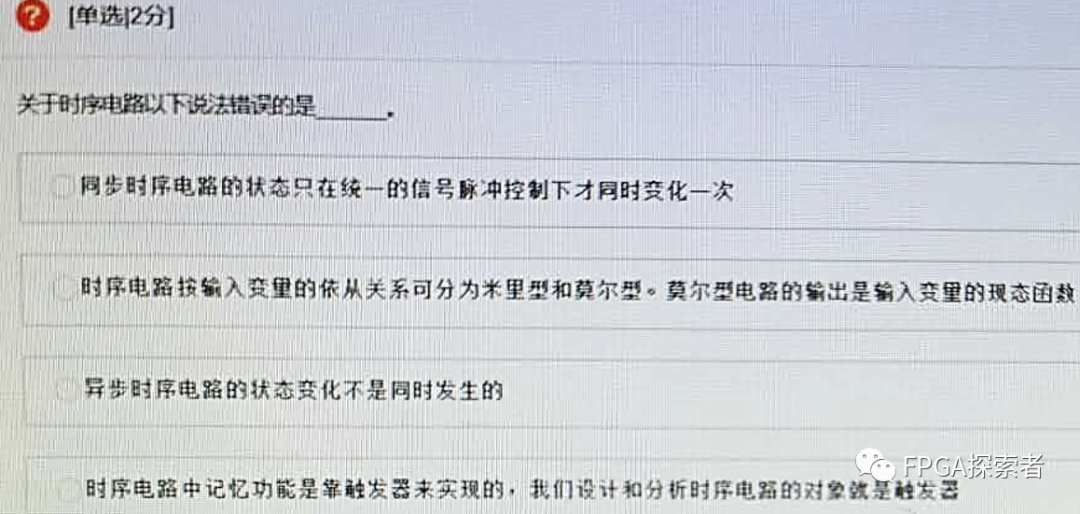

32. 关于时序电路,以下说法错误的是(B)

解析:

莫尔型输出:输出只和当前的状态有关;

米里型输出:输出除了和当前状态有关,还和输入有关。

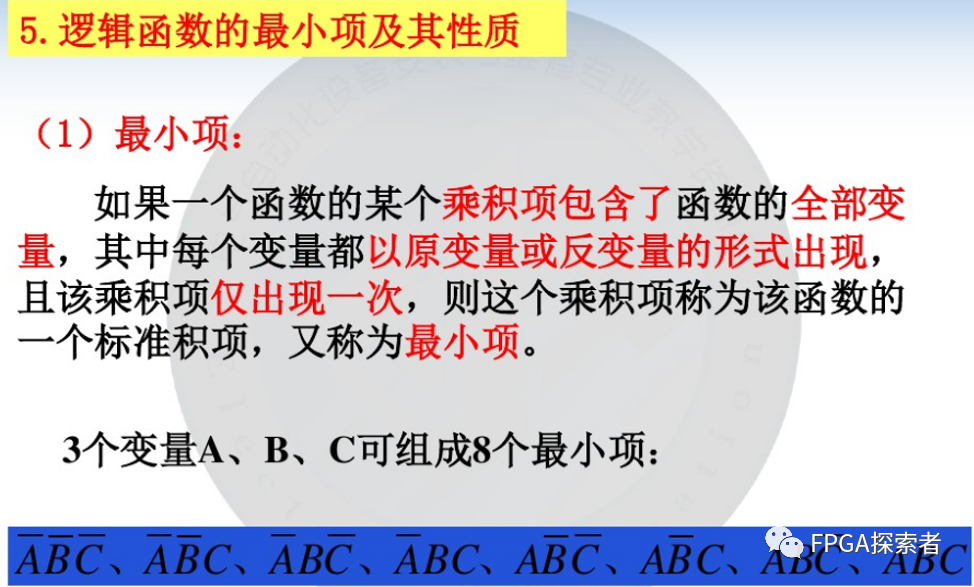

33.n变量的逻辑最小项有(2^n)项

解析:n变量的最小项有2^n项。

34. 若一模拟信号为带限,且对其抽样满足奈奎斯特条件,则只要将抽样信号通过(理想低通滤波器)即可完全不失真恢复原信号。

解析:低通滤波器,滤除高频噪声,保留到带限信号的有用信号的最高频率,此时使用奈奎斯特采样,可以无失真恢复信号。

35. 15位二进制数100111001110010,用10进制表示是(20082)

解析:2^14+ 2^11 + 2^10 + 2^9 + 2^6 + 2^5 + 2^4 + 2^1 = 20082。

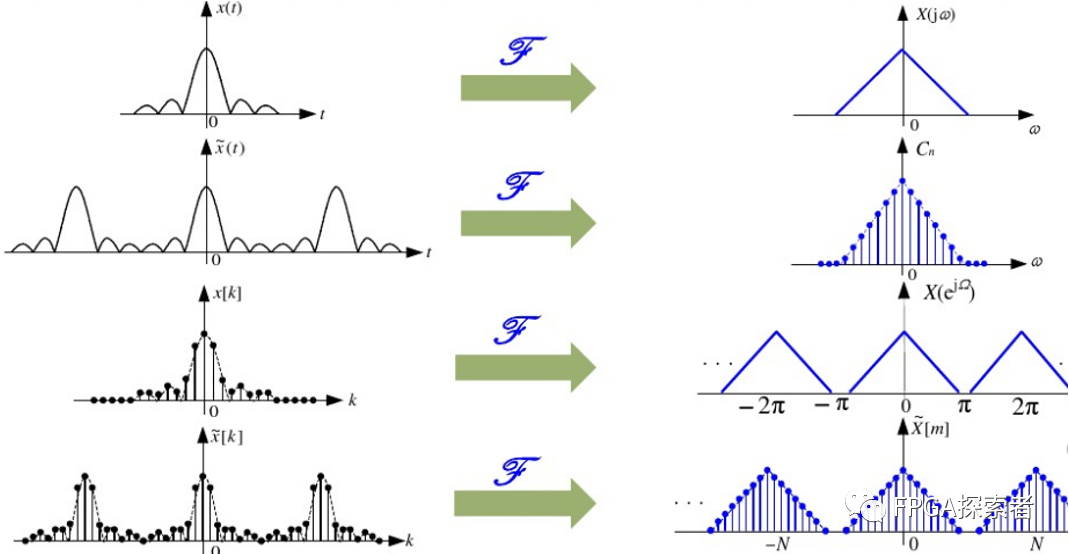

36. 连续周期信号f(t)的频谱特点是(离散、非周期频谱)

解析:

时域连续,频域非周期。

时域离散,频域周期。

时域周期,频域离散。

时域非周期,频域连续。

所以,连续周期时域信号对于离散非周期的频谱。

37. 卡诺图上变量的取值顺序是采用(循环码)

解析: 格雷码是循环二进制码。

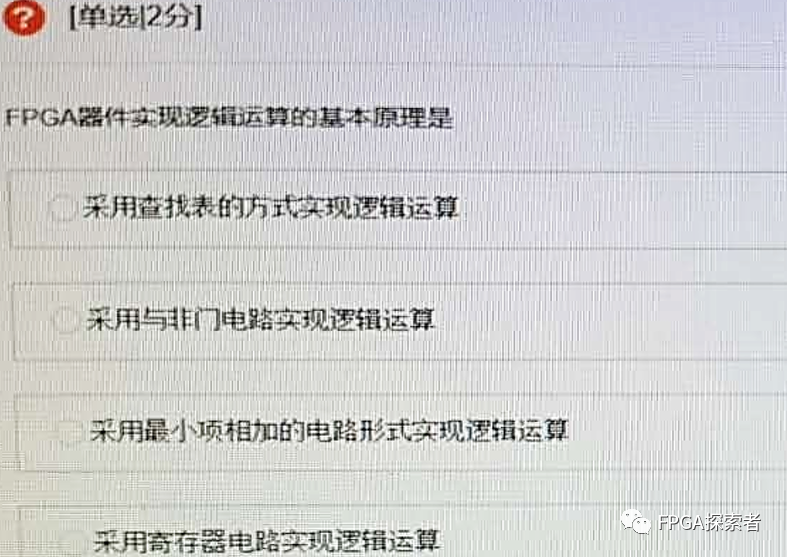

38. FPGA器件实现逻辑运算的基本原理是(A)

解析:FPGA底层是LUT查找表(Look up Table),与非门等门电路在综合后会使用 LUT 实现这些门电路运算逻辑。

39. -55用8bit二进制补码表示为(1100_1001)

解析:

补码,先求原码,取反,+1。

(1)55的二进制原码表示为0011_0111;

(2)取反,得到1100_1000;

(3)加1,得到1100_1001。

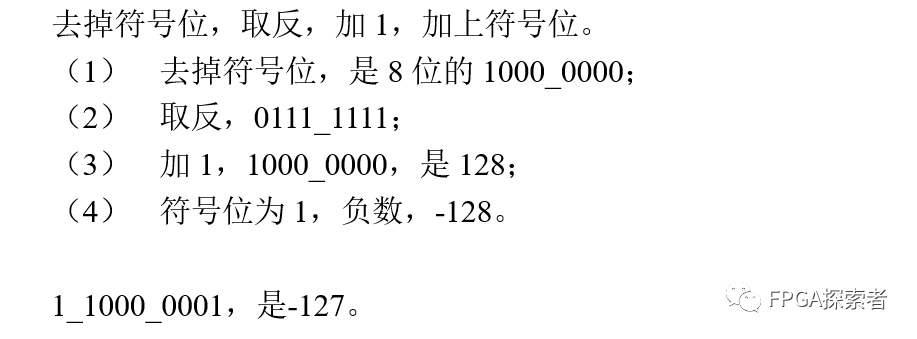

40.带符号数的9位二进制数110000000表示(-128)

解析:

41.使用DMA的好处不包括( C )。

A 减少数据的传输延时

B 一定条件下可以降低系统的功耗

C 软件复杂度肯定会降低

D 降低CPU占用

降低软件复杂度,那是有可能的,但说肯定那就不对了。

不定项:

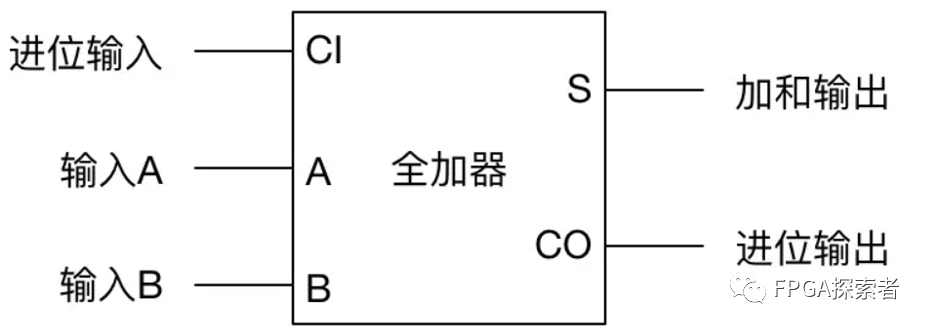

1. 全加器包含(加数、被加数、进位输入、进位输出、加和)

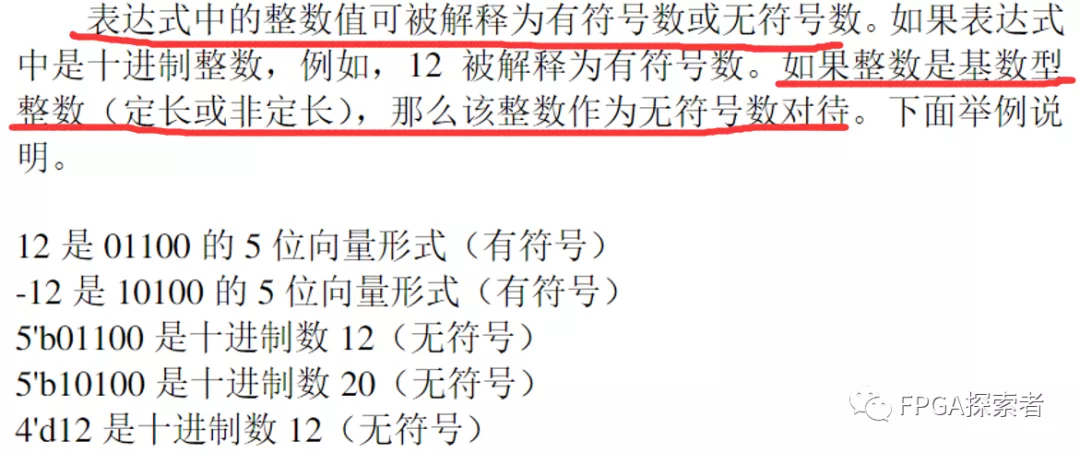

2.在Verilog HDL中,下列关于表达式的描述正确的是(ABCD)

A.表达式由操作数和操作符组成

B.表达式中可以使用函数调用

C.表达式可以使用数值

D.表达式中整数值可以解释为有符号数和无符号数

函数使用:FPGA手撕代码——CRC校验码的多种Verilog实现方式

3. 集成电路保护措施有()

【限幅输入保护电路】【二极管单向导电保护】【输出端对地保护】【输出端限流保护】

解析:

(1)输入电压限幅:限幅输入保护;

(2)输入电流限流:输入限流电阻,二极管;

(3)电源对地保护:限流,防止短路;

(4)输出限流保护:过载限流;

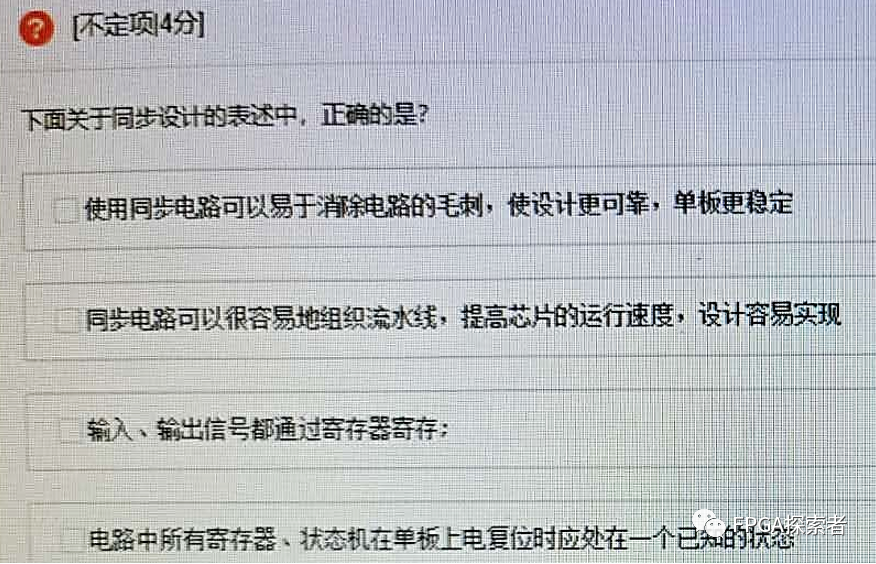

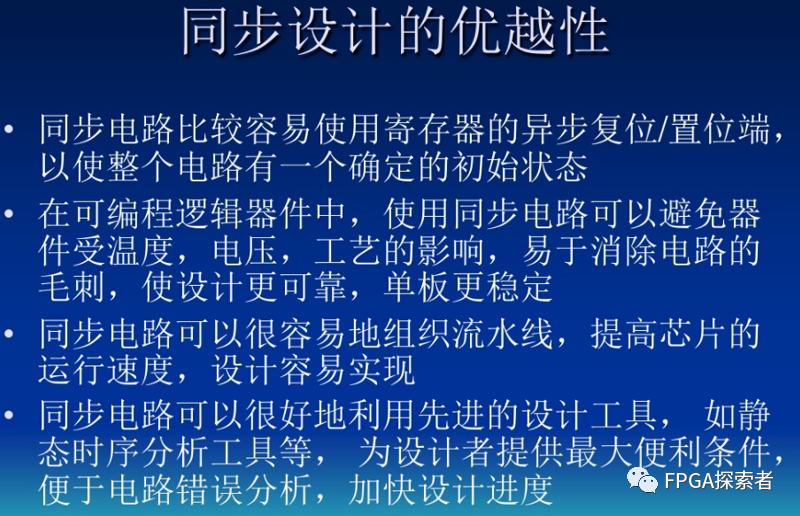

4. 下面关于同步设计的表述中,正确是是?(ABCD)

解析:

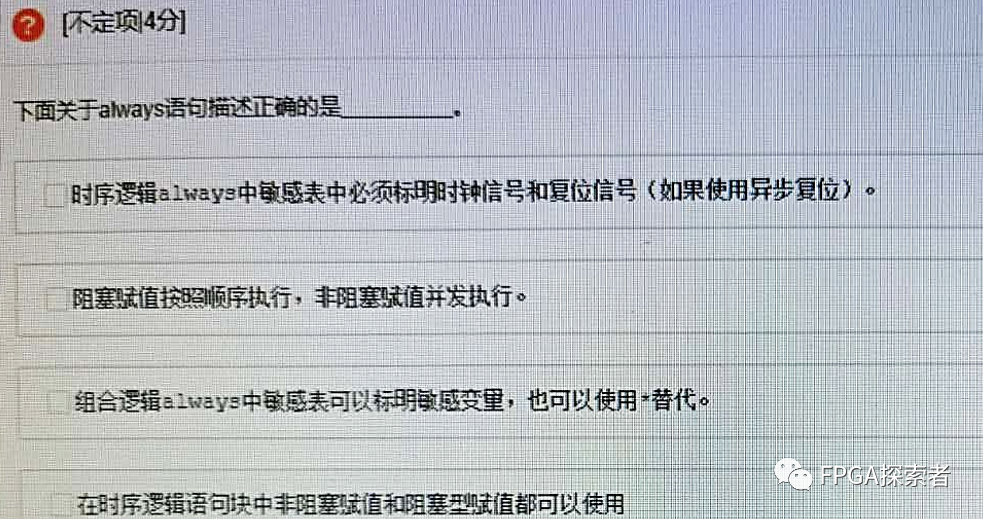

5. 下面关于 always 语句描述正确的是(ABCD)

6.一个VHDL程序,至少要包括(AC)。

A 实体 B 子程序 C 结构体 D 进程

一个完整的VHDL程序包含结构体,实体,配置,程序包,库。