FPGA/IC笔试——商汤科技

1、如果线网类型变量说明后未赋值,起缺省值是(z)?

2、电子系统设计优化,主要考虑提高资源利用率减少功耗(即面积优化)以及提高运行速度(即速度优化) ,下列方法 ( A)不属于面积优化。

A、流水线设计

B、资源共享

C、逻辑优化

D、串行化

3、reg[7:0] mema[255:0]正确的赋值是(A)

A、mema[ 5]=3'd0

B、mema[ 5][3:0]=4'd1

C、mema [8][8]=8'd0

D、都正确

4、某设计中使用了DDR3-1066,数据位宽32bit,FPGA工程中实现的DDR3 controller时钟为800MHz, 应用端时钟为200MHz, 数据位宽为128bit,请问,应用端DDR3可用的理论带宽为(B)

A、4264MB/ s

B、3200MB/ s

C、6400MB/ s

D、2132MB/ s

【解析】三种频率:内核频率(内存的真实运行频率);时钟频率(即I/O Buffer输入输出缓冲的传输频率);等效频率(数据传输频率)。

DDR3-1066数据位宽为32bit,则等效频率为1066Mbps,内核频率为1066/8 = 133Mbps

DDR3-1066 理论带宽 = 1066 * 32 / 8 = 4264;FPGA内存带宽 = 800 * 32 / 8 = 3200;应用端带宽 = 200 * 128 / 8 = 3200取瓶颈3200

5、解释名词:建立时间,保持时间和亚稳态。

建立时间:时钟脉冲沿到来之前,数据保持稳定不变的时间。

保持时间:时钟脉冲沿到来之后,数据保持稳定不变的时间。

亚稳态:亚稳态是指触发器无法在某个规定的时间段内到达一个可以确认的状态。

6、异步FIFO设计注意事项有哪些?

(1)在地址信号跨时钟域时需要对其进行二进制码转格雷码的转换并进行目标时钟域的时钟打两拍同步,以防止亚稳态的产生。

(2)写满信号由读地址同步到写时钟域并与写地址进行比较产生,读空信号由写地址同步到读时钟域并与读地址进行比较产生。这样可以在第一时间得到读空与写满的信息,并对异步fifo进行操作。

(3)异步fifo的深度需要考虑到写状态的背靠背写入状态以得到最适合的深度。

(4)读写地址需要扩展一位来判断是读空还是写满,当扩展后的读写地址的格雷码相等时为读空,若其前两位不同,后面相等时为写满。

设计难点:读写指针和空满信号的处理

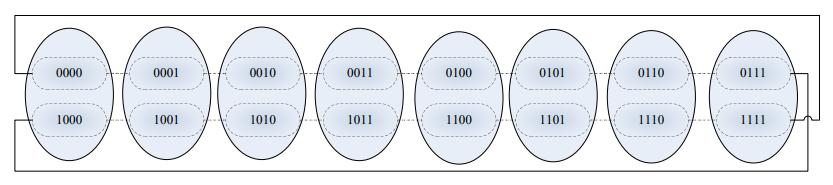

FIFO的读写指针是指读写地址,但是读写指针一般比真正用来读写的Memory地址要多一位,用来判断空满信号。多一位的读写指针周期性如下图所示,verilog代码为 assign gray = (bin>>1) ^ bin;

写指针总是指向下一个要写入的地址。写操作到来时,数据写入写指针指向的地址,然后指针指向下一个要写入的地址。

读指针总是指向下一个要读取的地址。要读的数据会提前准备在输出数据端口的缓存中,读操作到来时,数据发送至端口,读指针指向下一个要读取的地址。

产生空满信号:

空信号用来防止FIFO的underflow(下溢),当读指针追上写指针的时候表示空信号,写指针需要同步到读指针时钟域之后的写指针。

满信号用来防止FIFO的overflow(上溢),当写指针追上读指针的时候表示满信号,读指针需要同步到写指针时钟域之后的读指针。

由于是异步FIFO的设计,读写时钟不一样,在产生读空信号和写满信号时,会涉及到跨时钟域的问题,在读写指针上可能会产生亚稳态。需要通过两级寄存器同步和格雷码进行跨时钟域处理。

分别将写时钟域的写指针同步到读时钟域,将同步后的写指针与读时钟域的读指针进行比较产生读空信号;将读时钟域的读指针同步到写时钟域,将同步后的读指针与写时钟域的写指针进行比较产生写满信号。

同步会消耗至少一个时钟周期的延迟,可能会引起保守的判断,比如写指针同步到读时钟域,同步后的写指针小于等于当前实际的写指针,此时判断的FIFO为空不一定是真空;同理读指针同步到写时钟域,同步后的读指针小于等于当前实际的读指针,此时判断的FIFO为满不一定是真满。于是同步的延迟虽然比较保守,但是可以保证FIFO的特性,不会出错。

举个例子:大多数情形下,异步FIFO两端的时钟不是同频的,或者读快写慢,或者读慢写快,慢的时钟域同步到快的时钟域不会出现漏掉指针的情况,但是将指针从快的时钟域同步到慢的时钟域时可能会有指针遗漏,举个例子以读慢写快为例,进行满标志判断的时候需要将读指针同步到写时钟域,因为读慢写快,所以不会有读指针遗漏,同步消耗时钟周期,所以同步后的读指针滞后(小于等于)当前读地址,所以可能满标志会提前产生,满并非真满。进行空标志判断的时候需要将写指针同步到读指针 ,因为读慢写快,所以当读时钟同步写指针 的时候,必然会漏掉一部分写指针,我们不用关心那到底会漏掉哪些写指针,我们在乎的是漏掉的指针会对FIFO的空标志产生影响吗?比如写指针从0写到10,期间读时钟域只同步捕捉到了3、5、8这三个写指针而漏掉了其他指针。当同步到8这个写指针时,真实的写指针可能已经写到10 ,相当于在读时钟域还没来得及觉察的情况下,写时钟域可能偷偷写了数据到FIFO去,这样在判断它是不是空的时候会出现不是真正空的情况,漏掉的指针也没有对FIFO的逻辑操作产生影响。

通过格雷码也可以降低亚稳态的发生,将添加一位后的二进制地址吗转换成格雷码,格雷码是带有镜像对称的编码,低三维管委中心对称,分成两部分的低二位关于各部分的中心对称,如下图所示:

如图可观察出,写满和读空两种状态可以根据最高位来判断:

Ⅰ、当两个最高位相反,后三位相同时为写满;

Ⅱ、当两个完全相等时为读空。

原文链接:https://blog.csdn.net/persistlzy/article/details/107692874

7、在一个FPGA项目中,既有建立时间异常(setup violation),也有保持时间异常(hold violation),应该如何修改设计以使其正常工作?

对于建立时间异常的路径,可以适当降低时钟频率,修改组合逻辑电路以减少组合逻辑的延时,选择传输延时更少的寄存器,并可以适当增大时钟延时;

对于保持时间异常的路径,修改组合逻辑电路以增加组合逻辑的延时,选择传输延时更长的寄存器,并可以适当增大时钟延时,数据有效状态各增加一个或几个(根据建立和保持时间而定)时钟周期。

8、一个32bit浮点的累加器,A = A + data, A初始化为0, data为串行输入数据流,包含数据使能信号,加法器延迟5个时钟周期。请问如何用verilog语言实现一个累加器。

module MULTY_ADD(

input clk,

input rst_n,

input [8:0]data,

output [31:0]A

);

parameter IDLE = 3'b000;

parameter T1 = 3'b001;

parameter T2 = 3'b010;

parameter T3 = 3'b011;

parameter T4 = 3'b100;

reg [31:0]mid;

reg cur_state,nxt_state;

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

cur_state <=IDLE;

nxt_state <=IDLE;

end

else begin

cur_state <= nxt_State;

end

end

always@(*) begin

if(data[0] == 1) begin

case(cur_state)

IDLE: begin

nxt_state <= T1;

end

T1: begin

nxt_state <= T2;

end

T2: begin

nxt_state <= T3;

end

T3: begin

nxt_state <= T4;

end

T4: begin

nxt_state <= IDLE;

end

default :begin

nxt_state <= IDLE;

end

endcase

end

end

always@(posedge clk or negedge rst_n) begin

if(!rst_n ) begin

mid <= 32'b0;

end

if(data[0] == 1) begin

case(cur_state)

IDLE: begin

mid <= mid + {24'b0,data[8:1]};

end

T1: begin

mid <= mid + {16'b0,data[8:1],8'b0};

end

T2: begin

mid <= mid + {8'b0,data[8:1],16'b0};

end

T3: begin

mid <= mid + {data[8:1],24'b0};

end

default:begin

mid <= mid;

end

endcase

end

end

assign A = mid;

endmodule

9、用D触发器实现2倍分频的Verilog描述?

module Div(

input clk,

input rst_n,

output Q

);

reg Q;

always @(posedge clk or negedge rst) begin

if (!rst_n) begin

Q <= 0;

end

else begin

Q <= ~Q;

end

end

endmodule

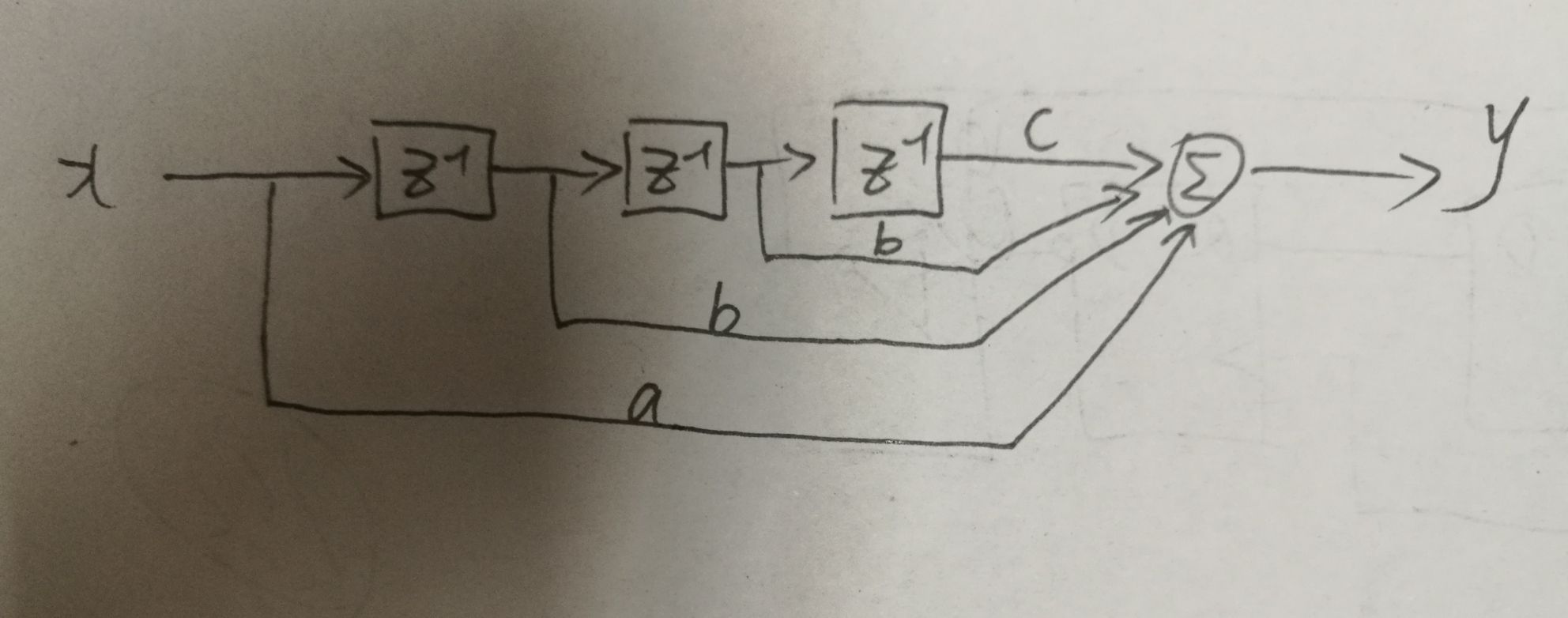

10、某FIR滤波器的频率响应为H(z)= a + bz-1+bz-2+cz-3。现需要对某采样输入信号x(n)滤波,滤波器和输入信号同属于一个时钟域,频率300MHz。

a) 请画出滤波器的实现框图;

b) 假如乘法器输出延迟5个时钟周期,加法器延迟7个时钟周期,输入到输出的最小延迟是多少?

c) 若输入都是定点数据,如何做量化处理?

如上图所示,输入数据x先延时3个周期,再并行乘以各自的系数,再前两个和后两个并行相加,最后再加一次:

总公式为:y(n) = ax(n) + bx(n-1) + bx(n-2) + c*x(n-3);

第一步:延时三个周期分别得到x(n-1)、x(n-2)、x(n-3)和当前数据x(n);

第二步分别乘以各自系数:ax(n)、bx(n-1)、bx(n-2)、cx(n-3);

第三步第一次加法:ax(n) + bx(n-1)和bx(n-2) + cx(n-3);

第四步第二次加法:ax(n) + bx(n-1) + bx(n-2) + cx(n-3)

所以总周期数为3+5+7+7 = 22clk