数电第四章总结——《组合逻辑电路》

数电第四章总结——组合逻辑电路

1. 编码器

(1) 普通编码器:一次只能有一个输入,就是将一个十进制编码成二进制。

(2) 优先编码器:允许同时有多个输入,但是只对优先级最高的进行编码。

如:74HC148

附加端

选通输入端(s‘):当s’为0时才导通,编码器才工作。

选通输出端(Ys’):当其为0时,表示编码器工作,但是没有输入,就是s’为0,但是其他没输入

输出扩展端(Yex’):当其为0时,表示编码器工作,且有输入。

选通输出端可以用来将一个3/8优先编码器变成4/16优先编码器。当高位有输入,选通输出端就会变成1了,它连在后面的选通输入端上,就让后面的不工作了。

- 译码器

和编码器相反,将一个二进制数转换为对应的十进制编号的那个输出。

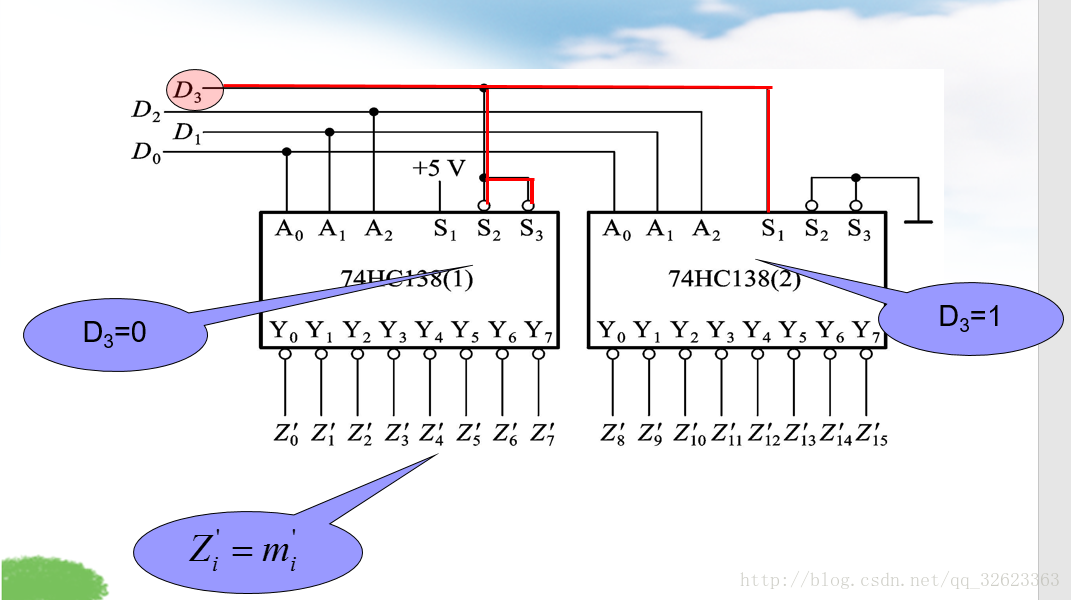

典型的是74HC138,其也有控制端,也是为了将3/8译码器变成4/16的,如图

二-十进制译码器7448

灯测试信号LT’ = 0 时,输出全部置1,全亮

灭零输入RBI’ = 0时,如果A0=A1=A2=A3=0,那么这个灯就灭了

灭零输出RBO’,如果灭零成功了,那么就等于0

灭灯输入BI’ = 0时,灯灭。

数据选择器

加法器

竞争冒险

当存在A+A’时,有0型冒险,如果存在AA’时,有1型冒险

消除竞争冒险的方法:接入电容、加入选通信号、修改电路设计