日本人教的AXI4-Lite总线课程

地址:https://www.bilibili.com/video/BV1364y117ZB/?spm_id_from=333.788.recommend_more_video.-1&vd_source=7a1a0bc74158c6993c7355c5490fc600

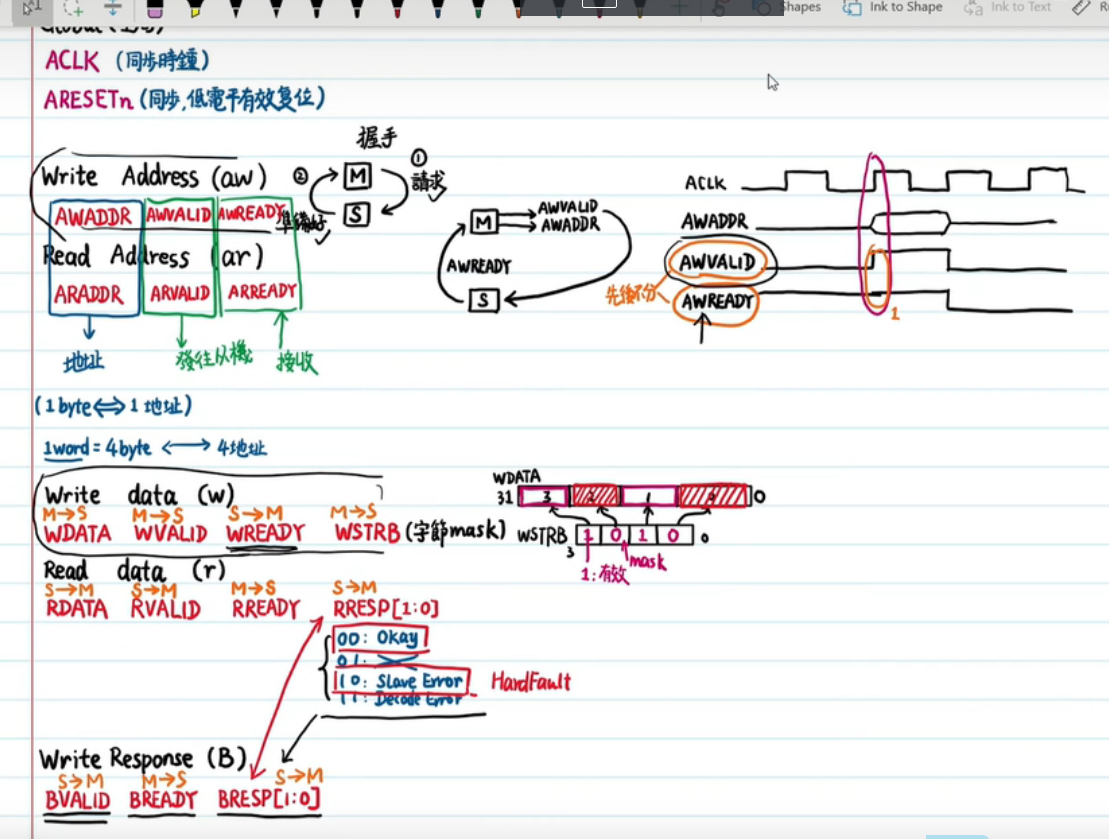

AXI4-Lite 传输的三种时序情况:

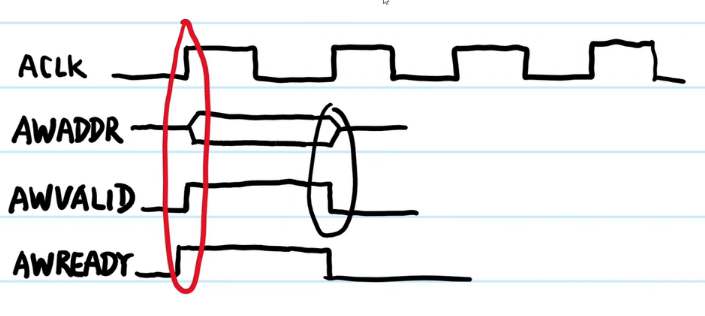

1. 主机 valid 了,但是 从机还没 ready,等待从机 ready

个人认为,从机ready后,主机其实可以在下一时钟周期更新地址,然后继续拉高valid信号

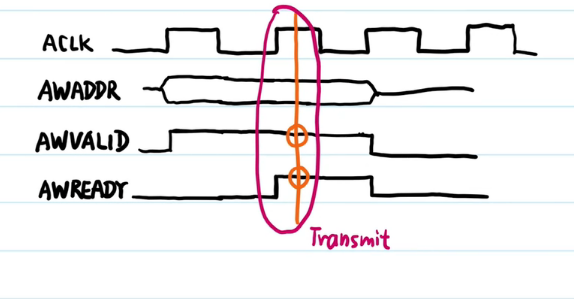

2. 主机 valid,同时 从机 ready,数据在这一周期内完成传输

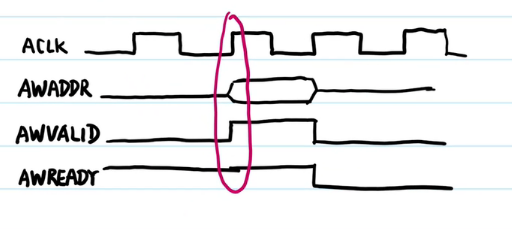

3. 从机ready, 等待 主机 valid

综合三种情况,主机的valid和从机的ready顺序不分先后,只要它们同时为1,传输则发生(且在一周期内完成)

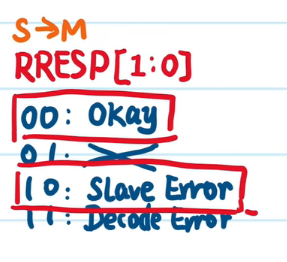

在 AXI4Lite 中,RRESP只有三种情况,分别是 Okay, Slave Error(从机错误,表示非法访问), Decode Error(总线桥上的解码错误)

看看总览:

接下来我们讨论一下 AXI4Lite 的写流程

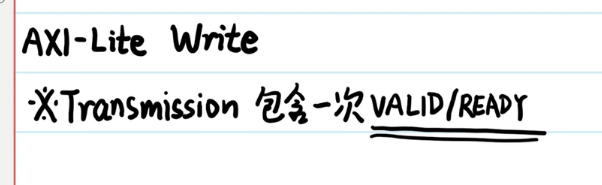

注意:在总线中,我们说传输,通常指一次完整的 VALID/READY 握手

这里有三种写数据的流程

1. 先完成写地址传输,再完成写数据传输,再完成写回馈传输。(最基本的传输方法,比较常用)

2. 先完成 写数据传输,。。。。(用得不多,很少有这种情况)

3. 同时完成写地址和写数据传输,再完成写回馈传输 (最常用,因为快)

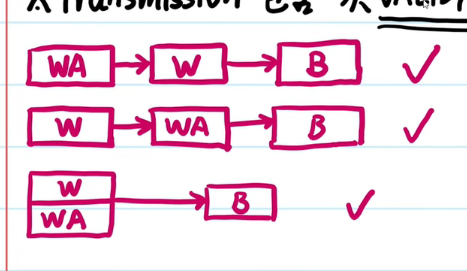

读的过程只有一种(不可能没有地址就有数据)

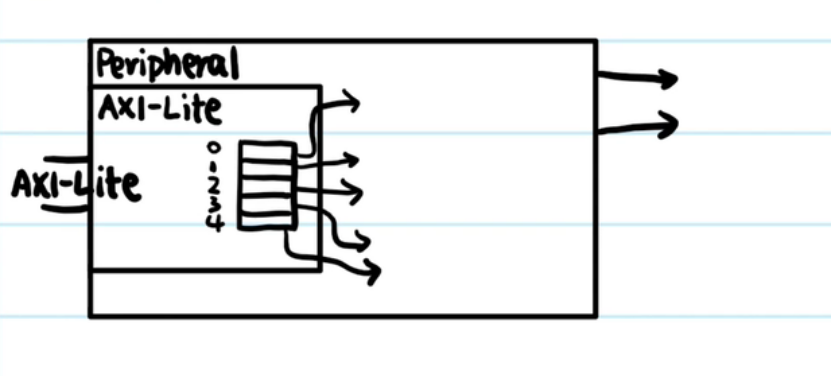

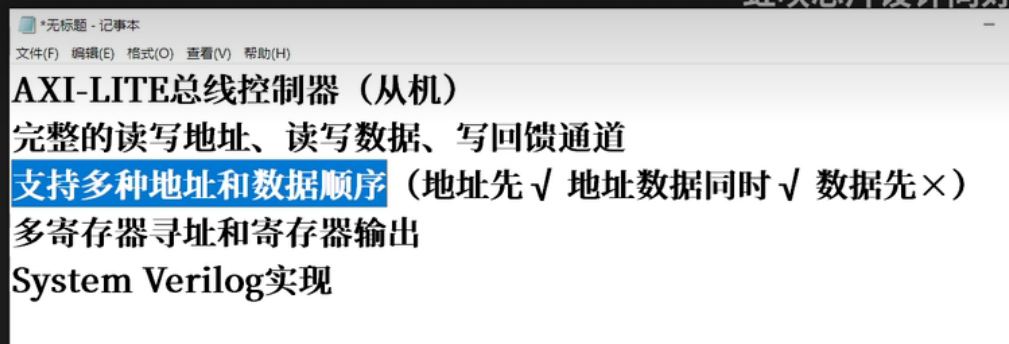

接下来我们讲解一个,使用 AXILite 接口的外设。

第二个视频:https://www.bilibili.com/video/BV1Vy4y1T7U5/?spm_id_from=333.788.recommend_more_video.3&vd_source=7a1a0bc74158c6993c7355c5490fc600

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· DeepSeek 开源周回顾「GitHub 热点速览」

· 物流快递公司核心技术能力-地址解析分单基础技术分享

· .NET 10首个预览版发布:重大改进与新特性概览!

· AI与.NET技术实操系列(二):开始使用ML.NET

· 单线程的Redis速度为什么快?

2022-03-06 The Missing Semester of Your CS Education(第六课,git)笔记