ATPG原理及实现——3.SPF & Quick STIL

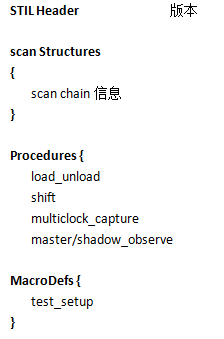

一、STIL Protocol文件基础结构

包含的内容:

- scan input和output的名称

- 哪些pin充当“clock”

- pins、clock、measures的时序定义

- 端口约束、等效关系

- test setup sequence、test_setup macro

- Scan enable sequence、load_unload procedure

- Scan shift sequence、Shift procedure

- 其他与设计有关的过程:master_observe,shadow_observe

示例:

STIL; ScanStructures{ ScanChain "chain1" { ScanIn “SDI[1]"; ScanOut SDO[1] ; } ScanChain "chain2" { ScanIn "SDI[2]"; ScanOut SDO[2] ; } Procedures { "load unload" { // clocks & resets off; enable scan V{CLOCK=0; RSTB=1; SCAN_EN=1; CONF_ENABLE=0;} shirt { V { _si=##; _ so=##; CLOCK=P;} //pulse shift clock; ##会用实际的pattern替代 } } } MacroDefs { "test setup" { V {CONF = 1; CONF ENABLE = 1 ; CLOCK = P;} V {CONE = 0; CONE ENABLE = 1; CLOCK = P;} V {CONF = 1; CONE ENABLE = 1; CLOCK = P;} V (CONF _ENABLE = 0; CLOCK = 0;} } }

二、创建SPF方法

①使用DFTC创建SPF(常用,首选)

②使用快速STIL命令

③手动创建SPF

在DRC或TEST模式下,可以使用以下命令来编写模板SPF文件:

write_drc_file <file> [-replace]

[-generic captures] (默认设置,将针对所有故障模型的单周期通用捕获过程写入带有单个协议文件的输出drc文件中)

[-nogeneric_captures]

常规/慢周期:multiclock_capture

at-speed周期:allclock_launch,allclock_capture

如果SPF可用,读入spf:

run_drc <spf_file>

set_drc <spf_file> run_drc

三、手动定义

1.定义PI

定义PI约束

-- 在整个测试程序中保持端口恒定,定义Pl(原输入)约束:

add_pi_constraints 1 ASIC_TEST

-- 查看现有的PI约束列表:

report_pi_constraints

-- 查看输入、输出、输入输出、所有端口的列表:

report_primitives [-pis l -pos l -pios l -ports]

定义PI Equivalences

-- 端口上的PI equivalences:

add_pi_equivalences [list P1 P2 P3]

add_ pi_equivalences ENA_P -invert ENA_N

-- 定义差分时钟:

add_clocks 0 CLKP -shift

add_clocks 1 CLKN -shift

add_pi_equivalences CLKP -differential CLKN

-- 查看现有的P1 equivalences:

report_pi_equivalences

2.quick STIL clock(一般不用,使用DFTC自动生成已经有了)

手动定义时钟:

add_ clocks <off_state> <port_name> -shift

-timing <[list period leading trailing strobe]>

//Examples: add clocks 0 [ list c1k1 c1k2] -timing [list 100 45 55 40] -shift //-shift使时钟在scan shift期间在load_unload过程中产生脉冲 add_clocks 1 SLAVE_CK -timing [ list 100 30 90 95]

定义OCC(internal clock):

add clocks <0 | 1> <pirgoames_list> -intclock

-pll_source <node_name>

-cycle <<<cycle_id> always_on l always_off l<int_node_name> <0 l 1 >>>

//example add_clock 0 "my_pll_ctrl/intclk" -intclock -pll_source u_pll/clka -cycle { 0 "my_pll_ctrl/u_clock_chain/launch_enable" 1 \ 1 "my_pll_ctrl/u_clock_chain/capture_enable" 1 }

注意:

在定义内部时钟之前,请先指定set_drc -num pll_cycles选项(定义capture模式下允许的PLL时钟周期数)

定义ATE时钟:

add_ clocks <0 l 1> <pin_names_list> -shift

-refclock

-timing {<<period><LE><TE><measure_time>>}

add_clocks 0 ate_clk1 -refclock -shift -timing {100 45 55 20}

如果在capture过程中需要产生脉冲,则ATE时钟也必须定义为TetraMAX的参考时钟。

定义异步set/reset:

①TetraMAX要求将影响时序设备的存储状态、测试仪周期内执行脉冲操作的所有port定义为“clocks”

②TetraMAX时钟包括: 传统clock、flip-flops和latch的异步set和reset、 RAMS的write/read控件

③用作同步和异步的reset不应定义为时钟。 使用以下drc选项: set_drc -allow_unstable_set_reset

3.SPF Capture procedures

//Capture procedure for stuck-at patterns "multiclock_capture" { W "_default_wET_"; F { "TEST_MODE"=1;} V ( "_pi" = \r169 #; " po"=r164 #; }} //Capture procedures for Transition or Path Delay patterns "allclock_launch" { w "_launch_WFT_"; F {“TEST_MODE"=1;} V{ "_pi"= \r169 #; "_po"=\r164 #; }} "allciock_capture" { w "_capture_WET_"; F {"TEST_MODE"=1;} V {"_pi"= \r169 #; "_po"=\r164 # ; }} "allclock_launch_capture" { w "_launch_capture_WFT_" F {"TEST_MODE"=1 ; } v {"_pi"= \r169 #; "_po"= r164 #;}} //Clocks pulses are controlled as part of the _pi signal group

4.在SPF中定义scan chain

add_scan_chains chain1 SDI2 SDO2

add_scan_chains chain2 SDI1 D1

add_scan_enables 1 SCAN_EN

add_scan_enables Z BIDI

Scanstructures { scanchain "chain1" {ScanIn SDI2; ScanOut SDO2; } scanchain "chain2" {ScanIn SDI1; ScanOut D1; } } Procedures { " load_unload"( V {CLOCK = 0;BIDI =Z ; SCAN EN=1;}” shift { V {_si=##; _so=##; CLOCK=P;) // pulse shift clock } } }

四、TetraMAX获取时间信息

TetraMAX使用基于周期的模拟器进行DRC分析。模拟器本身没有定时功能,但是事件按特定顺序发生,并在特定时间应用于测试仪

- 事件顺序和时间来自测试协议,测试协议可以来自多个地方:

从DFTC写入的SPF文件

使用Quick STIL命令指定的时间

TetraMAX中的默认计时

手动输入到SPF中的时间

- TetraMAX在此期间的定时的作用:

DRC:使用timing值和事件顺序进行DRC检查。

ATPG和故障模拟:不使用timing信息

pattern:timing与输出向量相关联

1.在已存在的UPF中更新timing

read_drc

update_ *

read_drc <original_SPF_file> update_wft -wft <name> -period <d> -force <d> -strobe <d> update_clock -wft <name> -clock <name> -pulse {<le><te>) update_scale -wft <name> -unit <nslps> write_drc_file <new_SPF_file> ………… run_drc <new_SPF_file>

2.SPF中的波形表和信号组

在STIL文件中把定义的时序保存为WaveformTable

Timing { WaveformTable "_default_MFT_" { Period "100ns" ; Waveforms { "_default_In_Timing_" { 01ZN {'0ns' D/U/z/N; }} "_default_cLk0_Timing_" {P {'0ns' D; '45ns' U; '55ns' D;}} //D高电平 U低电平 "_default_Out_Timing_" {X {'0ns' X; }} "_default_Out_Timing_" {HTL {'0ns'; '40ns' H/T/L; }} } } }

STIL文件用SignalGroups节省空间

SignalGroups { "_default_clk1_Timing_" = '"prst_n"'; "_default_clk0_Timing_" = '"sdr_clk"+"sys_clk"' ; "_default_In_Timing_" = '"pframe_n"+ ..."pad[0]"'; "_default_out_Timing_" ='"pframe_n" + ... "pad[0]"'; "_si" = '"pad[0]" + ... "pad[5]"' {scanIn;} "_so" = '"sd_ A[0]" + ... "sd_A[5]"'{scanout;} ; }

五、不同的Bond-outs

功能引脚的不同bond-outs可以完全在TetraMAX中处理,2个步骤:

step.1 在build之前从网表中删除未绑定的pin

add_net_connections PI {pi_list} -remove

add_net_connections PO {po_list] -remove

add_net_connections PIO {bidir_list} -remove

step.2 从协议文件中删除引脚:

从信号部分删除

从相关的signalGroups中删除(_pi_po等)

减少procedures中signalgroups更改中的重复计数

注意:如果使用Quick STIL命令,则不需要第二步

- 如果未绑定测试端口,则应更改设计的测试方法,而不是更改ATPG

查找扫描链的最低配置

尽可能在内部限制恒定信号并通过初始化序列进行驱动

考虑多模式扫描设置(用于晶圆测试的完整链条的测试模式、在封装测试时重新配置以减少链条;注意:每种模式需要单独运行的ATPG)

使用压缩逻辑减少对顶层引脚的需求(自适应扫描可以通过有限的引脚驱动许多链)

- 如果无法访问链,则会影响pattern质量,覆盖范围,运行时间和pattern数