ATPG原理与实现——2.TetraMAX Flow

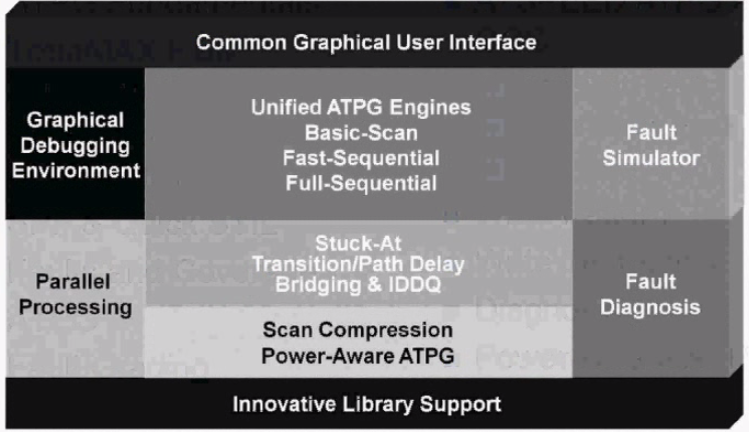

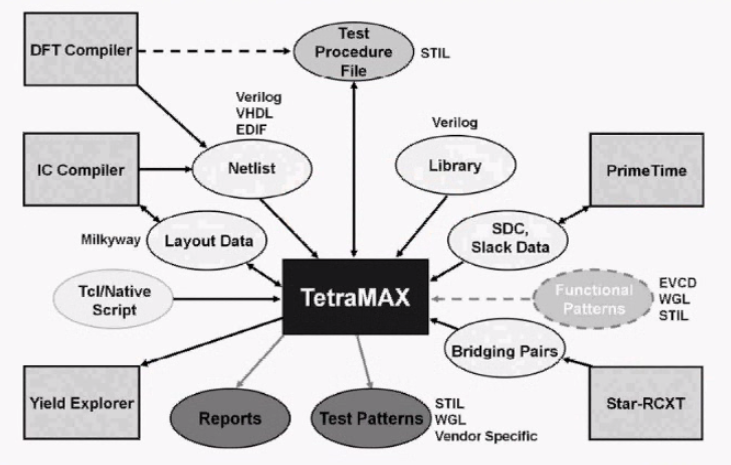

TetraMAX Overview

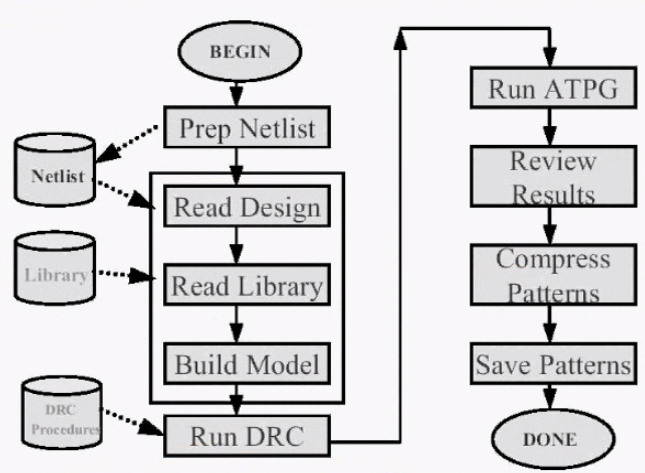

TetraMax Flow

TetraMax的启动

tmax [file] 如果要执行file直接跟file路径即可

tmax -notcl(基本不用)

tmax -shell (不启动图形界面,一般用这个)(如果启动64位就加-64)

1.读入library与netlist

保存log文件

BUILD-T> set_messages -log tmax.log -replace

读入library和netlist

BUILD-T> read_netlist mylibrary.v (读verilog的library)

BUILD-T> read_netlist my_asic.v (支持以下格式:Verilog、EDIF、VHDL)

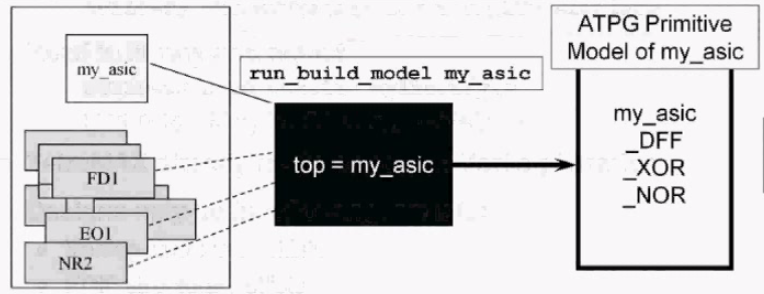

2.Build ATPG Design Model

build mode

BUILD-T> run_build_model my_asic

3.DRC

DRC-T> run_drc DUT.spf

(S rules)在shift mode下检查扫描链的工作顺序,并确保逻辑连接扫描输入到输出路径

(C rules)检查连接到扫描触发器的clock和异步set/reset端口,以确保它们仅由主输入控制

(C rules)从扫描capture mode切换到扫描shift mode并再次返回时,将检查clocks/set/resets的关闭状态

(Z rules)检查多驱动程序网络是否存在争用

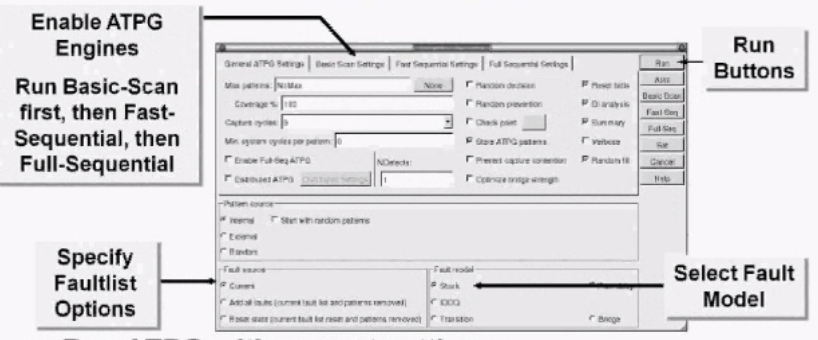

4.setup and run ATPG

TEST-T> run_atpg -auto (推荐用auto,在覆盖率和pattern数之间提供最佳起点和折中点)

5.保存ATPG pattern

TEST-T> write_pattern mypat.stil -format stil

| Format |

Binary、STIL、WGL、WGL_flat、FTDL、TDL91、TSTL2 |

| Pattern Type | Basic、Fast-Seq、Full-Seq |

| Pattern Range | First-Last |

| Splitting patterns | Multiple Files |

| Compression | Binary、GZIP |

6.参考脚本

#save TetraMAX transcript to log file set_messages -log lab1.log -replace #Reading libraries and design read_netlist ../libs/ libs_tmax.v.gz read_netlist ../libs/rams.v read_netlist ../design_data/orca_final .v #set undefined modules as black boxes set_build -black_box PLL set_build -black_box CLKMUL #Run Build run_build_model # Perform scan Design Rules check run_drc ../ design_data/orca_final.spf #setup and run ATPG add_faults -a1l set_atpg -capture 4 #Run ATPG engine run_atpg -auto #Review Test Coverage report_summaries analyze_faults -class au report_patterns -summary #save Test Patterns write_patterns all_pats.stil -foimat stil -replace