top down flow实践

1.compile

将rtl转换为网表文件

dc_shell | tee ./log/1compile.log

######################## # Read RTL # ######################## # Read the design set hdlin_enable_presto_for_vhdl true #读取VHDL设计时,它会检查代码 set acs_hdl_source {../ref/rtl/ORCA_init/vhdl} #设置vhdl来源 acs_read_hdl -f vhdl ORCA #读取设计ORCA,格式vhdl # DC will add generic info to the name of the design!! UGLY... fix: rename_design [get_designs SDRAM_RFIFO*] SDRAM_RFIFO rename_design [get_designs SDRAM_WFIFO*] SDRAM_WFIFO rename_design [get_designs PCI_RFIFO*] PCI_RFIFO rename_design [get_designs PCI_WFIFO*] PCI_WFIFO rename_design [get_designs SDRAM_IF*] SDRAM_IF rename_design [get_designs PCI_CORE*] PCI_CORE rename_design [get_designs ORCA_TOP*] ORCA_TOP current_design ORCA link #write -f ddc -hier -o unmapped/ORCA.ddc ################################# # Setup for compile # ################################# suppress_message {UID-401 TIM-111 TIM-103 OPT-1006 DDB-74 DDB-72} #不要打印以下warning source -echo -verbose scripts/constraints.tcl;#将非测试约束应用于设计 # Make all reset signals ideal set_ideal_network -no_propagate [get_nets I_ORCA_TOP/pci_rst_n] set_ideal_network -no_propagate [get_nets I_ORCA_TOP/sdram_rst_n] set_ideal_network -no_propagate [get_nets I_ORCA_TOP/sys_rst_n] set_ideal_network -no_propagate [get_nets I_ORCA_TOP/sys_2x_rst_n] #设置dont_touch属性,以防止在优化过程中修改或替换这些对象 set_dont_touch [get_cells *_iopad*] set_dont_touch [get_cells I_CLK_SOURCE*] set_ideal_network [get_pins I_CLK_SOURCE*/Z] #set_dont_touch [get_cells I_RST_SOURCE*] group_path -name INS -from [all_inputs] group_path -name OUTS -to [all_outputs] # Freeze all SDRAM DDR output muxes set_dont_touch [get_cells I_ORCA_TOP/I_SDRAM_IF/sd_mux*] # I WANT only the mux on the SDRAM outputs!! # Note: STA will not see the port cap!! set_ideal_network [get_pins I_ORCA_TOP/I_SDRAM_IF/sd_mux*/Z] # 防止DC在最终Verilog网表中写出Assign或tran语句。 set_fix_multiple_port_nets -all -buffer_constants [get_designs *] set_auto_disable_drc_nets -all # Using compile instead of compile_ultra to avoid unexpected optimizations on the init_regs compile -scan #compile_ultra -scan 更多的优化策略 # Simplify design hierarchy: ungroup -all -simple -start_level 3 # In bottom-up HSS flow, something below causes problems at top-level insertion set_critical_range 2.0 [current_design] set_fix_multiple_port_nets -all -buffer_constants [get_designs *] compile -scan -incremental #compile_ultra -scan -incremental #remove_unconnected_ports -blast [get_cells -h *] change_names -rules verilog -hierarchy write -format ddc -hier -o mapped/ORCA.ddc #report_constraint -all > reports/constraint.rpt #report_timing > reports/timing.rpt

2.read_design

set hdlin_enable_rtldrc_info true;# enable rtl code checking in DV set test_simulation_library "./tmax/rams.v" # Read the mapped ORCA design read_ddc mapped/ORCA.ddc current_design ORCA link

3.create_test_protocol

# Read the design from the unmapped flow #read_ddc mapped/ORCA.ddc #set current_design ORCA #link set test_simulation_library ../ref/tmax/libs.v remove_test_protocol # Setup timing set test_default_delay 0 set test_default_bidir_delay 0 set test_default_strobe 40 # Declare signals for the protocol set_dft_signal -view existing_dft -type ScanClock -timing {45 55} -port {pclk sdr_clk sys_clk} set_dft_signal -view existing_dft -port prst_n -type Reset -active_state 0 set_dft_signal -view existing_dft -port scan_en -type ScanEnable -active_state 1 #set_dft_signal -view existing_dft -type Constant -active_state 1 -port test_mode set_dft_signal -view existing_dft -type Constant -active_state 0 -port conf_ena ## read_test_protocol -section test_setup ./scripts/test_setup.spf -verbose write_test_protocol -output output.spf # From the above specifications, create the test protocal create_test_protocol dft_drc

test_setup.spf

test_setup.spf

4.preview_dft

report_scan_state report_dft_signal -view exist report_dft_signal -view spec source settings_protocol.tcl preview_dft preview_dft -show scan_clocks preview_dft -show scan_summary set_scan_configuration -clock_mix mix_edges preview_dft -show scan_clocks set_scan_configuration -clock_mix mix_clocks preview_dft -show scan_clocks set_scan_configuration -chain_count 6 preview_dft -show scan_clocks

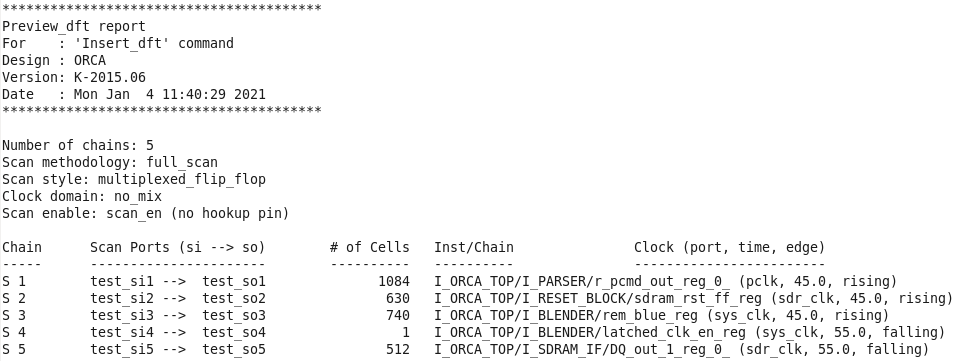

no mix时:

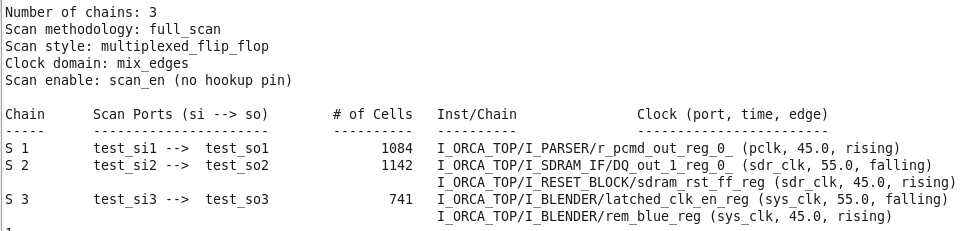

mix_edges时:

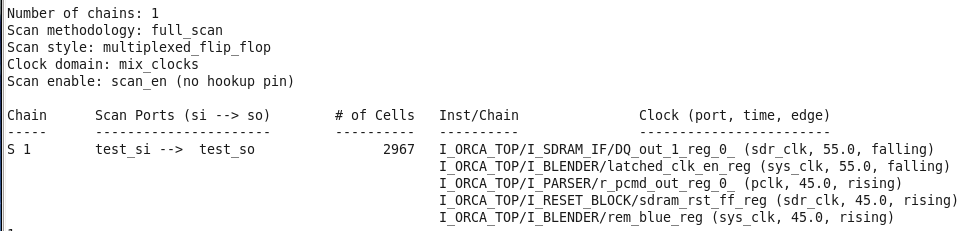

mix_clocks时:

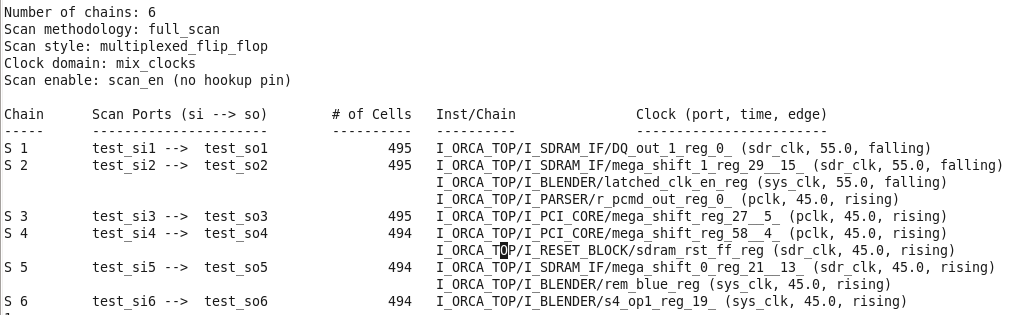

设置6条chain时:

5.insert_dft

# Allow clock domains to be mixed together on same chain #add_lockup设置为默认值true时,在扫描链的时钟域边界之间插入锁定锁存器。 set_scan_configuration -chain_count 6 -add_lockup true -clock_mixing mix_clocks # Specify all scan ports for {set i 0} {$i < 6} {incr i} { set hookup_cell pad_iopad_$i set_dft_signal -view spec -port pad[$i] -type ScanDataIn -hookup_pin $hookup_cell/CIN set hookup_cell sdram_A_iopad_$i set_dft_signal -view spec -port sd_A[$i] -type ScanDataOut -hookup_pin $hookup_cell/I set_scan_path chain$i -view spec -scan_data_in pad[$i] -scan_data_out sd_A[$i] } #保留设计名称;关闭所有优化 set_dft_insertion_configuration -preserve_design_name true -synthesis none # Set a variable to identify logic added by insert_dft set compile_instance_name_prefix DFTC_ # Insert scan logic insert_dft # Run post-DFT DRC check and get a coverage estimate dft_drc -coverage_estimate

6.handoff

# Change names change_names -rule verilog -hierarchy # Generate some reports report_scan_configuration > reports/scan_config report_dft_signal -view exist > reports/dft_signals report_dft_signal -view spec >> reports/dft_signals report_scan_path -view existing_dft -chain all > reports/scan_chains report_scan_path -view existing_dft -cell all > reports/scan_cells # Write a Verilog netlist set test_stil_netlist_format verilog write -f verilog -h -o tmax/ORCA_scan.v # Write the STIL protocol file for TetraMAX write_test_protocol -o tmax/ORCA_scan.spf # Write the SCANDEF file for reordering in ICC (write_scan_def *before* writing a ddc) write_scan_def -output mapped_scan/ORCA.scandef # Check the scandef contents check_scan_def # Write the ddc design write -format ddc -hierarchy -output mapped_scan/ORCA.ddc

write_scan_def SCANDEF:扫描链信息,以在物理实现流程中执行扫描链重排序。