scan chain的原理和实现——8.AT SPEED Test & OCC

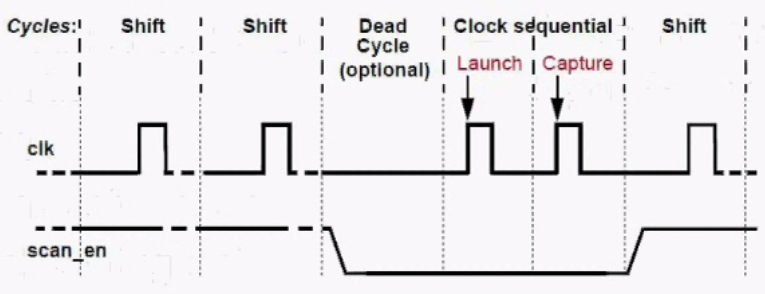

AT SPEED Test

last_shift launch mode (低速测试)

system_clock launch mode ( launch on capture)

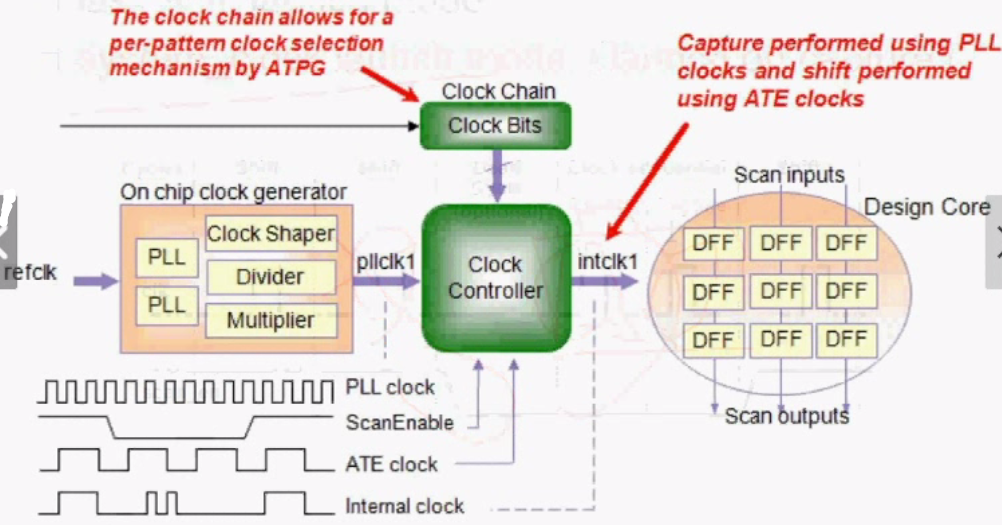

1.at speed test structure and OCC Controller

2.OCC Controller

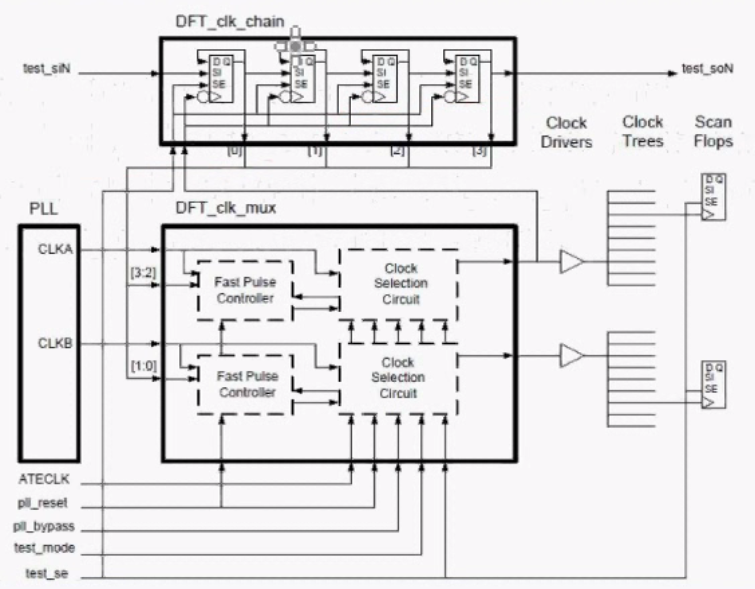

当使用set_dft_configuration -clock_controller enable运行insert_dft

DFT编译器会将DFT_clk_mux和DFT_clk_chain组件添加到网表中。

2.1OCC Controller的结构

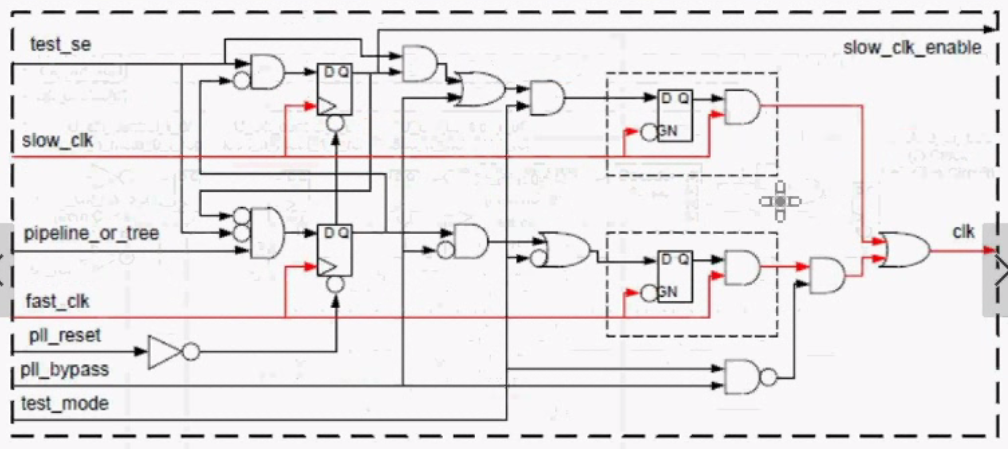

①fast pulse controller

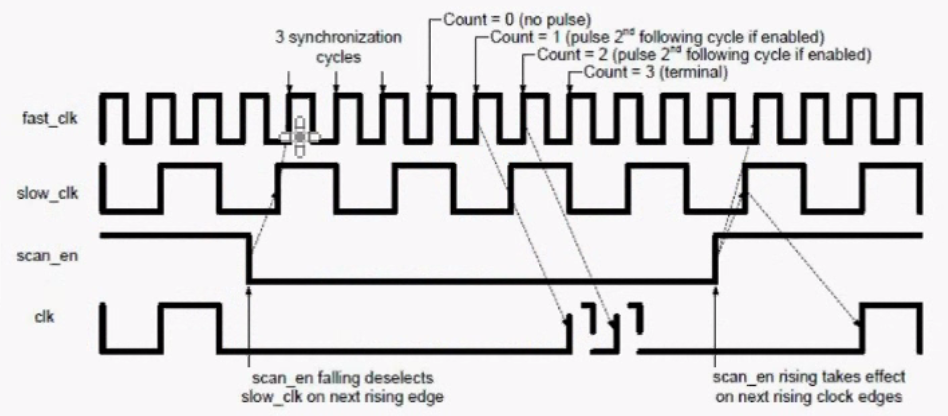

②clock selection circuit

DFT_clk_mux I/O ports

| port name | direction | function |

| reset | input | 1重置控制器,0允许控制器运行 |

| test_mode | input | 1控制时钟,0无条件选择快速时钟 |

| pll_bypass | input | 1选择slow_clk,0选择clock switch-over操作 |

| scan_en | input | 调解clock switch-over操作 |

| clk_enable[m:0] | input | 从时钟链捕获脉冲控制 |

| fast_clk[n:0] | input | PLL的快速时钟 |

| slow_clk | input | ATE时钟 |

| clk[n:0] | output | 扫描触发器output clock |

2.2 OCC脚本示例:

Reference clock ==> ref_clk

ATE clock ==> ate_clk

PLL clock (output of pll) ==> pll/out

External clock ==> ext_clk

#test_default period is 100 set test_default_period 100、 # specify the reference clock with proper period and timing (only one command for reference clock) set_dft_signal -yiew exist -type refclock -period 73 -timing { 40 50} -port ref_clk # specify the pll clock (output from PLL), as type oscillator set_dft_signal -view exist -type oscillator -hookup_pin pll/out #Specify the ATE clock,as type oscillator and scanclock both set_dft_signal -view exist -type oscillator -port ate_clk set_dft_signal -view exist-type scanclock -tining {50 80} -port ate_clk #specify the external clock (if any) set_dft_signal -view exist -type scanclock -timing {50 80} -port ext_clk

#test_default period is 100 set test_default period 100 # specify the reference clock (as type refclock and Masterclock ) set_dft_signal -view exist -type MasterClock -timing {50 80} -port ref_clk set_dft_signal -view exist -type refclock -period 100 -timing {50 80) -port ref_clk #specify the pll clock (output from PLL),as type oscillator set_dft_signal -view exist -type oscillator -hookup_pin pll/out #Specify the ATE clock,as type oscillator and scanclock both set_dft_signal -view exist -type oscillator -port ate_clk set_dft_signal -view exist -type scanclock -timing {50 80} -port ate_clk #specify the external clock(if any) set_dft_signal -view exist -type scanclock -timing (50 80} -port ext_clk

注意:

OCC控制器使用的ATE时钟也不能用作为扫描单元提供时钟的外部时钟。 这些时钟必须分别驱动。(使用ATE时钟为扫描单元提供时钟将导致TetraMAX中C39违规以及随后的仿真失败 )

插入DFT的OCC控制器要求ATE时钟必须是定义为振荡器时钟的自由运行时钟。

不要在内部和外部时钟之间执行域间测试。内部时钟与外部时钟和ATE时钟异步,因此它们的相对时序是不可预测的。

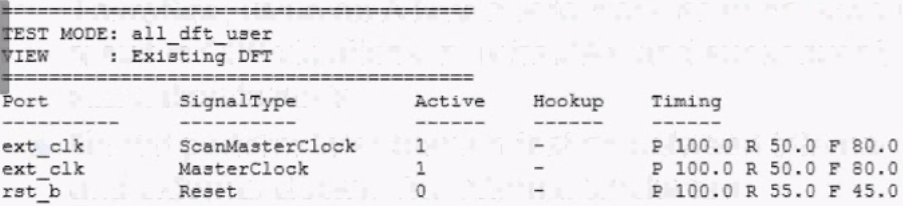

3.scanmasterclock & masterclock

对于多路复用触发器(Mux-D),ScanClock的信号“type”是用于指定ScanMasterClock(扫描移位时钟)和MasterClock(捕获时钟)。 用于Mux-D扫描设计,同一时钟通常用于移位和捕获。 当定义了Scanclock并report_dft_signal,将同时看到ScanMasterClock和MasterClock属性。

set_dft_signal -view existing_dft -type scanclock -port ext_clk -timing {50 80}

report_dft_signal -view existing dft