Scan and ATPG (Tessent)----1.基础概念

1、测试的目的

筛选出有错误的芯片。

2、测试的类型

功能测试——验证电路的功能。

制造测试——验证设计有没有制造缺陷

制造试验类型:

扫描测试、扫描压缩测试、BIST(Memory test、Logic test)

3、什么是scan test

使内部电路可控、可观测。

4、制造缺陷

短路、断路、桥接等,port短路到0/1、逻辑单元翻转转速度不正常、路径延迟不正常等

5、测试中使用的常见故障模型

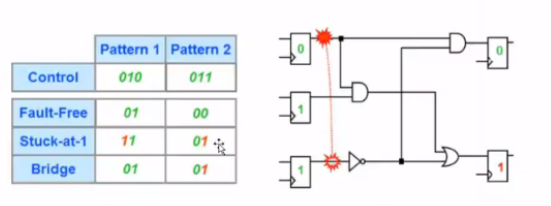

Stuck-at(最常见):

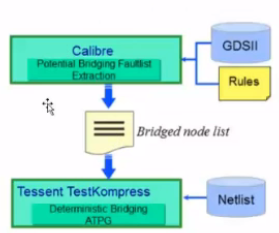

Layout--Aware Bridge Fault Model

主要用于非常高的质量要求才使用,基于物理属性

Bridge Fault: Multiple Detection

默认情况下,一旦检测到故障,就不再针对该故障进行再次检测。

故障针对用户指定的次数(“n”)可多次检测,每次检测增加检测桥接的统计机会。

set_multiple_detection -guaranteed_atpg_detections < n >。指定每个可测试错误所需的检测数量

桥梁覆盖估计(BCE)报告了多重检测在统计上检测桥梁缺陷的能力。

At-Speed Fault Models: Transition

At-Speed Fault Models: Path Delay

User-Defined Fault Models (UDFM)/Cell-Aware UDFM

IDDQ Fault Model

在稳定状态下测量静止电源电流

6、ATPG过程

选择故障-->pattern产生-->故障仿真-->删除故障-->存储pattern

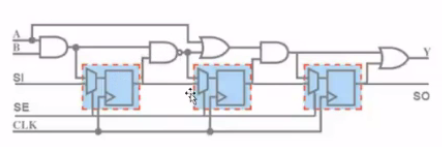

7、scan test

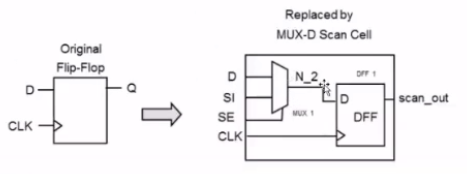

通过扫描单元替换普通触发器来创建控制点和观察点。将扫描触发器连接在一起以创建扫描链。利用这些扫描链,生成测试pattern,在特定节点设置特定值,传播可测量的结果。

scan flip-flops/scan cells

多路复用器选择数据输入: D普通模式、scan_in(SI)扫描模式。

Scan_enable(SE)选择操作模式。

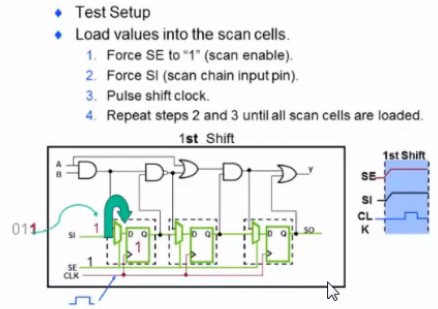

Basis scan test

Test setup优化设计并设置条件以进入测试模式(仅限开始测试)

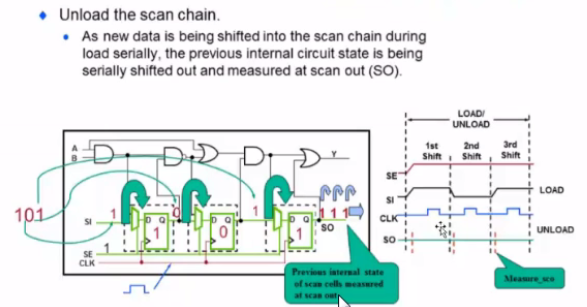

Load/unload- shift连续地将已知值转换为扫描链,将测试结果移出。

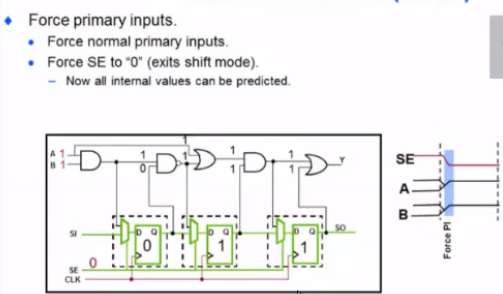

Capture应用由已知值(扫描和Pl)定义的激励,允许组合电路在功能模式下工作,测量输出(PO),将测试结果存入扫描链。

Repeat load/unload重复加载/卸载-移位/捕获,直到测试完成。

Basic scan test contain the following events:

1. Load scan chain (many cycles)

2. Force primary inputs(PI)

3. Measure primary outputs(PO)

4. Pulse capture clock

5. Unload values from scan cells

- Load next pattern

load

capture

unload

8、tessent工具

-Tessent FastScan 不带压缩 -Tessent TestKompress 有EDT压缩模块

-Tessent Scan 做scan insertion -Tessent Diagnosis 定位错误点

-Tessent MemoryBIST(Shell) -Tessent LogicBIST(Shell)

- Tessent Scan / ScanPro

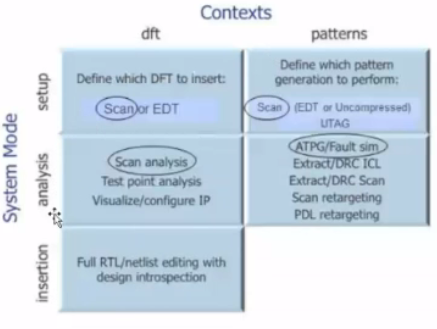

启动命令:tessent - shell (默认启动模式:setup)

3个模式模式: setup——定义当前上下文并指定/加载设计信息。

analysis——用于执行设计分析、pattern生成、PDL重定位和模拟。

insertion——用于执行设计编辑和插入。

两个contexts: dft、pattern

设置context命令, 如:set_context patterns -scan

常见context:

| dft: | 用于编辑门级、rtl级 |

| dft -edt | 用于EDT模块的产生和插入 |

| dft -scan | 用于扫描分析和扫描链插入。 |

| patterns -scan | 用于生成pattern |

| patterns -ijtag | 针对IJTAG的PDL命令重定向和icl网络提取的设计。 |

| patterns -scan_diagnosis | 测试故障诊断,以确定缺陷的失效机制和位置。 |

查看帮助:tessent -manual help read_c* help read_c* -all

在tessent里运行linux命令: system [unix command]