STM32架构相关

整理了一下STM32相关的底层结构,有助于消化理解

先上几张图片(主要参照STM3210x系列)

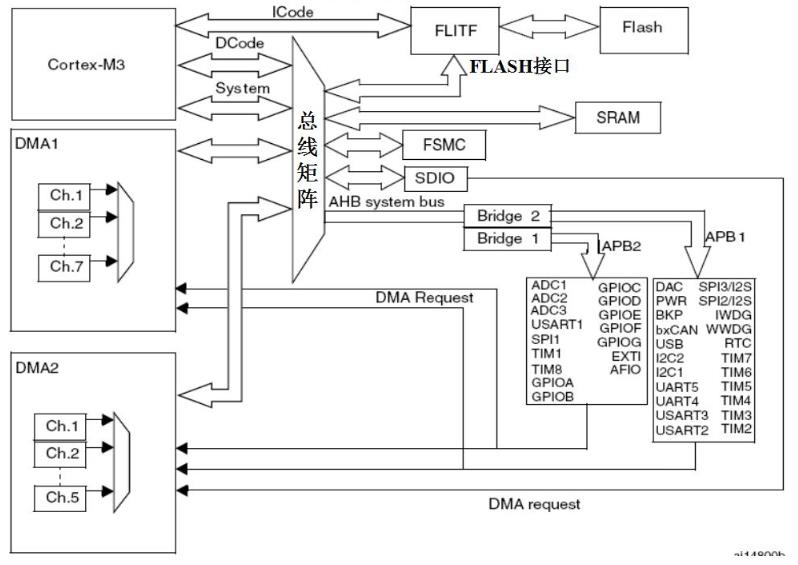

1.芯片结构组成图:

2.STM32内部结构:

3.Cortex-M3模块结构图:

4.STM3210X内部结构:

桥:

四个主动单元 :

M3内核的ICode总线(I-bus)、DCode总线(D-bus)、 系统总线(S-bus)、DMA(DMA1、DMA2、以太网DMA)

四个被动单元 :

内部SRAM、内部闪存、FSMC、AHB到APB桥

ICode总线 :

将M3内核的指令总线与FLASH指令接口相连,用于指令预取

DCode总线:

将M3内核的数据总线与FLASH数据接口相连,常量加载和调试

系统总线 :

将M3内核的系统总线与总线矩阵相连,协调内核与DMA访问

DMA总线:

将DMA的AHB主控接口与总线矩阵相连,协调CPU的DCode和DMA到SRAM、闪存、外设的访问

总线矩阵:

协调内核系统总线和DMA主控总线间的访问仲裁,仲裁采用轮换算法

包含DCode、系统总线、DMA1和DMA2总线、被动单元

AHB到APB桥 :

两个AHB/APB桥在AHB和两个APB总线间提供同步连接

APB1速度限于36MHz,APB2全速最高72MHz

一、时钟结构(时钟和复位模块,如参考上半部分所示)

系统复位后,所有外设全部关闭,但 SRAM 和 FLASH接口(FLITF)除外。

使用外设之前需打开该外设时钟,设置 RCC——AHBENR 寄存器 。

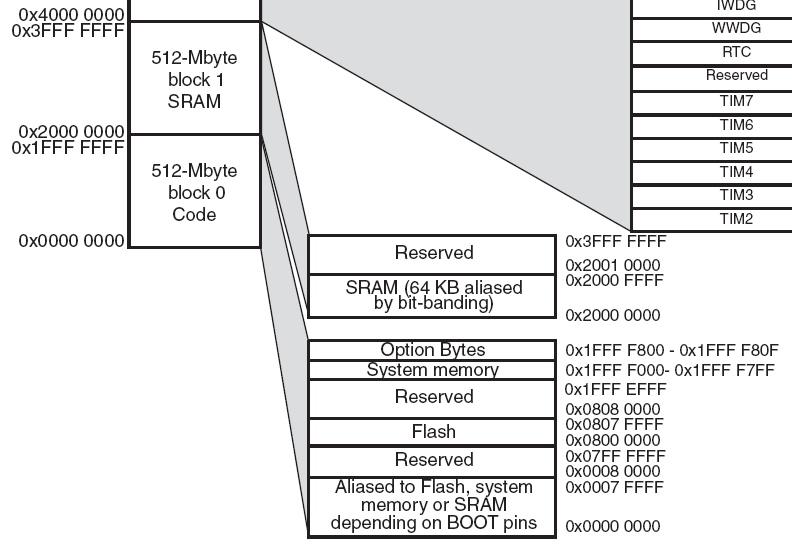

二、存储结构 :(参考上半部分)

*存储组织:

Cortex-M3的存储系统采用统一编址方式,小端方式 4GB 的线性地址空间内,

寻址空间被分成 8 个主块 block0-block7 ,每块512MB。

片内Flash: 从 0x00000000开始(严格来讲是从0x08000000开始,到0x0800x xxxx结束,程序就烧到里面。)

片内SRAM:从 0x20000000开始(用来保存程序运行时产生的临时数据的随机存储器,运行时变量,堆栈的存放的地方)

包括:

代码空间

数据空间

位段、位段别名

寄存器

片上外设

外部存储器

外部外设

拓展延伸:e2prom ,存储掉电需要保存的数据;fsmc总线还可以扩展nor 和nand;

*FLASH:

由 Main Block 和 Information Block组成

Main Block:

存放用户程序,最高512KB地址范围:0x0800 0000 – 0x0807 FFFF小容量:16K-32K,最大4Kx64bit,共32x1K页中容量:64K-128K,最大16Kx64bit,共128x1K页大容量:256K-512K,最大64Kx64bit,共256x2K页小容量:16K-32K,最大4Kx64bit,共32x1K页互联型:最大32Kx64bit,共128x2K页

Information Block:

System Memory 2KB:0x1FFF F000 – 0x1FFF F7FF ISP Bootloader程序Option Bytes 16B:0x1FFF F800 – 0x1FFF F80F

*SRAM:

最大64KB

地址范围:0x2000 0000 – 0x2000 FFFF

*片上外设地址映射:

*位段(bit-band)、位段别名 :

M3存储空间中包括两个位段区,该区域即可字操作,又可位操作

SRAM最低1MB空间: 0x2000 0000 – 0x200F FFFF

外设最低1MB空间:0x4000 0000 – 0x400F FFFF

a.为方便位段区的操作,安排了两个32M的位段别名区

b.位段区中每一位 映射 位段别名区中的一个字

c.通过对别名区中某个字的读写操作,可以实现对位段区中某一位的读写操作

别名区,2个32MB:

SRAM:0x2200 0000 – 0x21FF FFFF

外设:0x4200 0000 – 0x41FF FFFF

位段别名区中的字与位段区的位映射公式:

bit_word_addr = bit_band_base + (byte_offset x 32) + bit_number x 4

例如:SRAM位段区中地址0x20000300字节中位2

0x22006008 = 0x22000000 + (0x300 x 32) + (2 x 4)

对别名区中某个字进行写操作:该字的第 0 位将影响位段区中对应的位

对别名区中某个字进行读操作:若位段区中对应的位为 0 则读的结果为 0x0 ,若位段区中对应的位为 1 则读的结果为 0x1

PS: 对别名区的读写可以实现对位段区中每一位的原子操作,而且仅只需要一条指令即可实现

*启动模式 :

STM32系统启动区:0x0000 0000 – 0x0007 FFFF,512KB

系统启动之后: CPU从位于0x0000 0000地址处的启动区开始执行代码

该区实际既无FLASH,也无SRAM,通过引导配置后,将实际引导区映射到启动区

系统复位后,在SYSCLK第4个上升沿,BOOT管脚的状态被保存,用户通过设置BOOT1,BOOT0的引脚状态选择启动模式

CPU从位于0x0000 0000地址处的启动区开始执行代码

0x0000 0000 实际是SP

0x0000 0004 是执行代码的地址

即使被映射到启动区,仍然可以在原存储空间访问相关存储器

从待机模式退出后,BOOT引脚状态被重新保存,待机时,BOOT管脚需保持

STM32F10x通过配置 BOOT[1:0]引脚选择三种不同启动模式

三、片上外设

STM32F10x外设

STM32F103xx增强型大容量外设

四、GPIO结构

共?(5) x 16个I/O口:

- PA0 ~ PA15

- PB0 ~ PB15

- PC0 ~ PC15

- PD0 ~ PD15

- PE0 ~ PE15

3.3V与5V兼容:

- PA8 ~ PA15

- PB2 ~ PB4、 PB6 ~PB15

- PC6 ~ PC12

- PD0 ~ PD15

- PE0 ~ PE15

仅支持3.3V:

- PA0 ~ PA7,兼做 ADC_IN0 ~ ADC_IN7

- PB0 ~ PB1,兼做 ADC_IN8 ~ ADC_IN9

- PB5

- PC0 ~ PC5,兼做 ADC_IN10 ~ ADC_IN15

- PC13 ~ PC15

引脚 (48 64 ...)

开发工具

STM32系列的优点

先进的内核结构,STM32系列使用了ARM最新的、先进架构Cortex-M3内核

优秀的功耗控制,STM32处理器具有三种低功耗模式

运行模式时使用高效的动态耗电机制,在Flash中以72MHz全速运行时,如果开启外部时钟,处理器仅耗电27mA

待机状态时极低耗电,典型值2uA

电池供电时,提供低电压2.0~3.6V工作能力

灵活的时钟控制机制,用户可以根据自己所需的耗电/性能要求进行合理优化

RTC可独立供电,外接纽扣电池供电

性能出众而且功能创新的片上外设

STM32 处理器片上外设的优势来源于双 APB 总线结构

其中有一个高速 APB,速度可达CPU 的运行频率,连接到该总线上的外设能以更高的速度运行

USB: 12Mbit/s

USART: 4.5Mbit/s

PI: 18Mbit/s

IIC: 400kHz

GPIO: 18MHz翻转

PWM: 定时器72MHz输入

针对 MCU 应用中最常见的电机控制,STM32 对片上外围设备进行一些功能创新

内嵌适合三相无刷电机控制的定时器和ADC

高级PWM定时器提供:

6路PWM输出 -> 死去产生 -> 边沿对齐和中心对齐波形

编码器输入 -> 霍尔传感器 -> 完整的向量控制环 紧急故障停机、

可与2路ADC同步、与其它定时器同步 可编程防范机制可用于防止对寄存器的非法写入

双通道ADC采样/保持,12位1uS,连续/独立模式,多触发源

等等

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 从 HTTP 原因短语缺失研究 HTTP/2 和 HTTP/3 的设计差异

· AI与.NET技术实操系列:向量存储与相似性搜索在 .NET 中的实现

· 基于Microsoft.Extensions.AI核心库实现RAG应用

· Linux系列:如何用heaptrack跟踪.NET程序的非托管内存泄露

· 开发者必知的日志记录最佳实践

· winform 绘制太阳,地球,月球 运作规律

· 超详细:普通电脑也行Windows部署deepseek R1训练数据并当服务器共享给他人

· 上周热点回顾(3.3-3.9)

· AI 智能体引爆开源社区「GitHub 热点速览」

· 写一个简单的SQL生成工具