quartus使用串口IP模块

在quartus平台中使用串口模块的IP,需要使用到platform designer软件来实现。

1、在quartus界面调出IP Catalog界面。

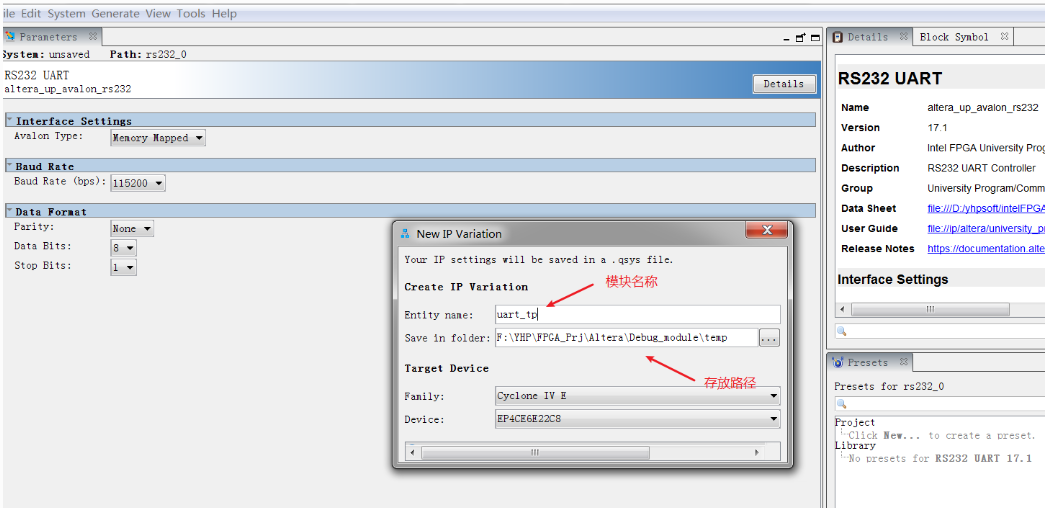

2、在IP catalog中搜索UART,找到RS2323模块,并双击打开,选择合适的路径和存放。

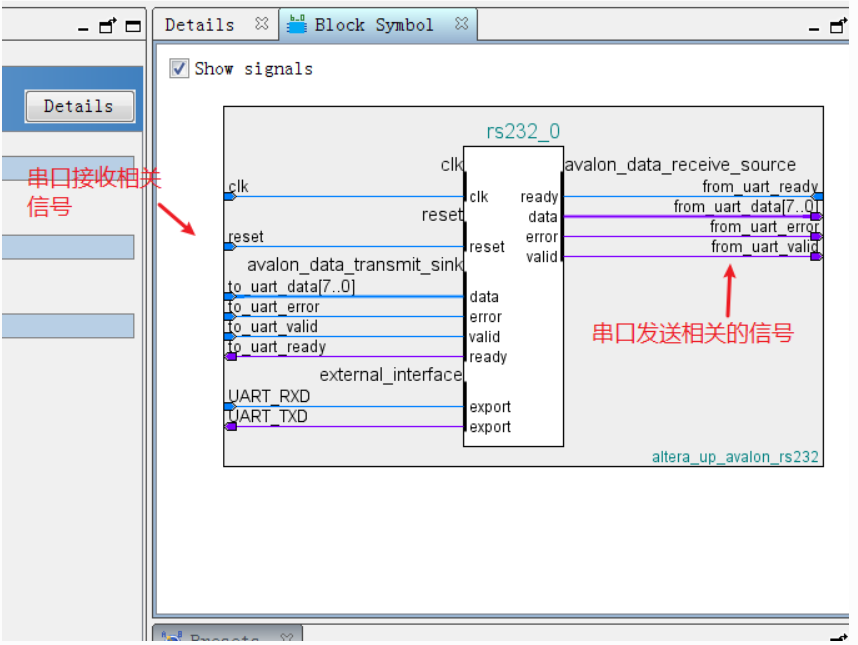

3、使用该模块若不搭建nios软核,则使用streaming。

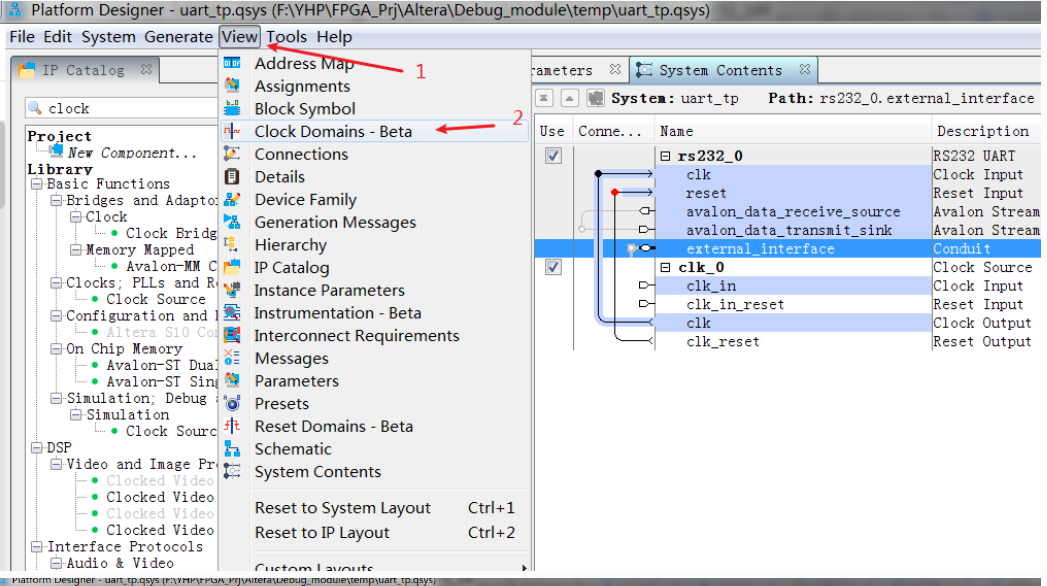

在右上角电机Block Symbol或者在菜单选择View->Block Symbol打开模块符号。

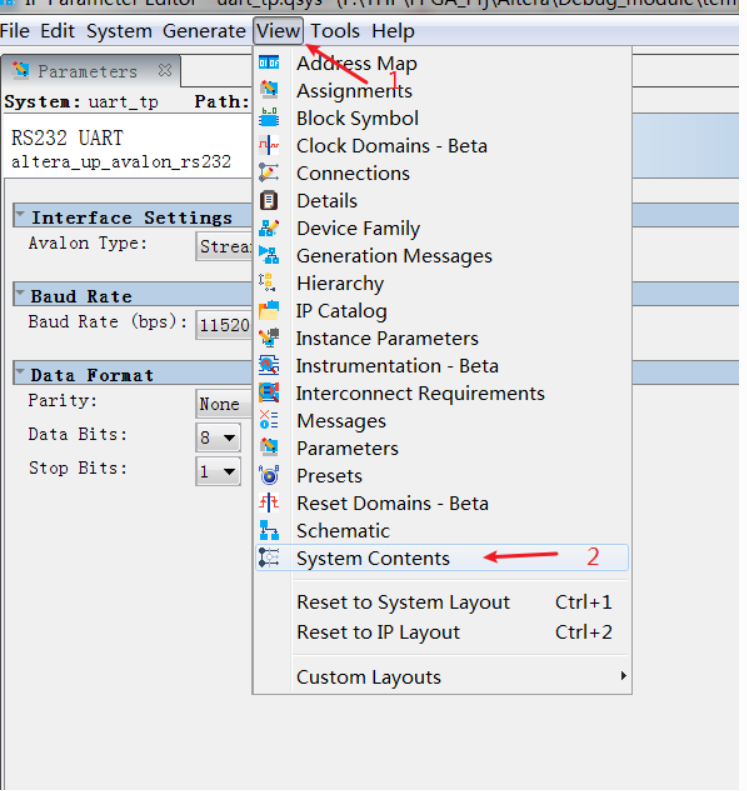

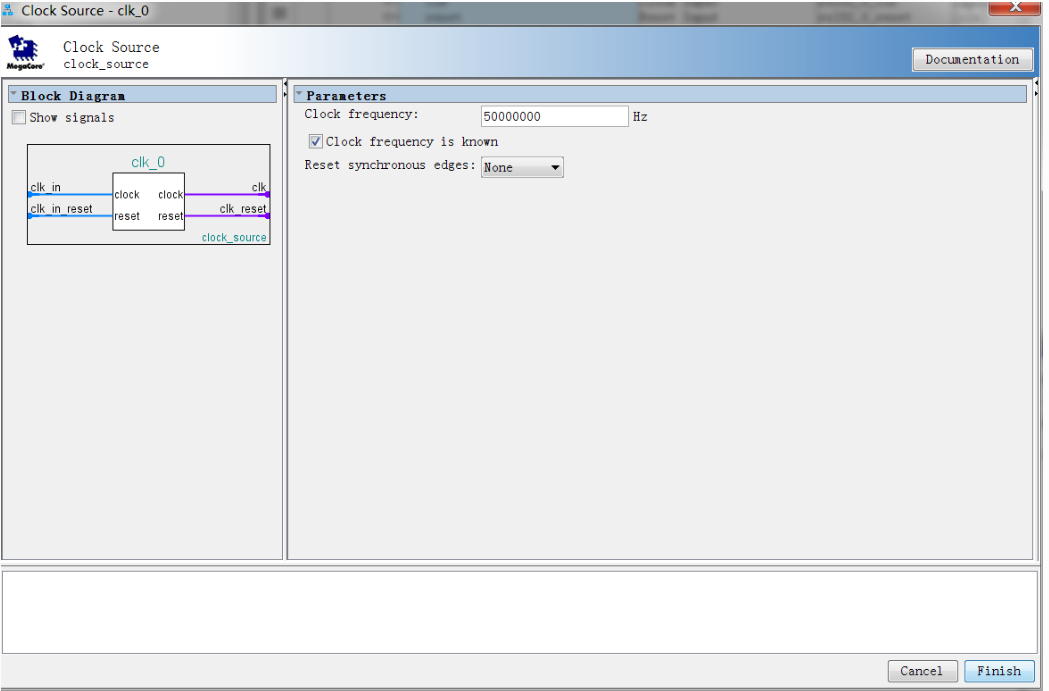

4、串口配置了波特率,其自动配置的参数与时钟有关,因此需要加入时钟模块,告知系统输入时钟为多少。

操作如下:

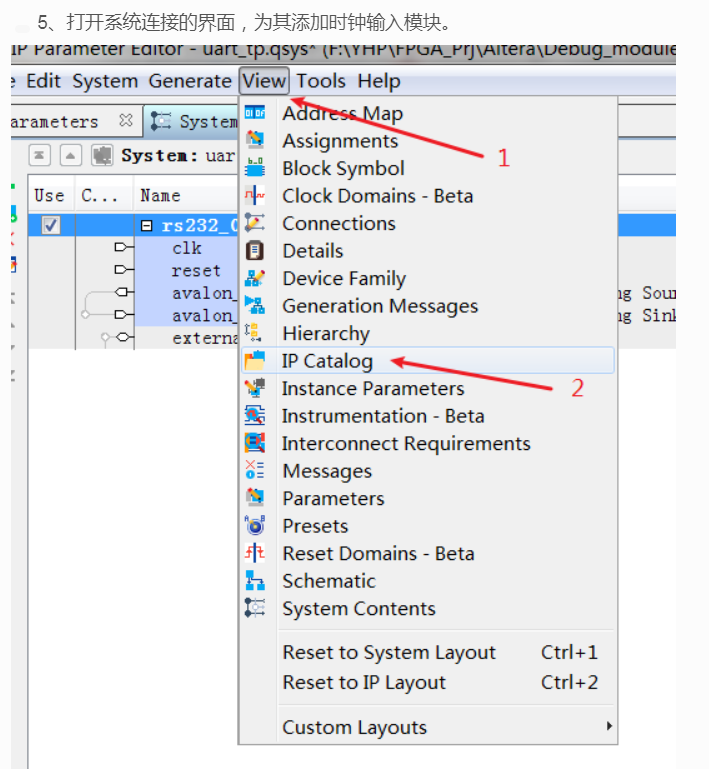

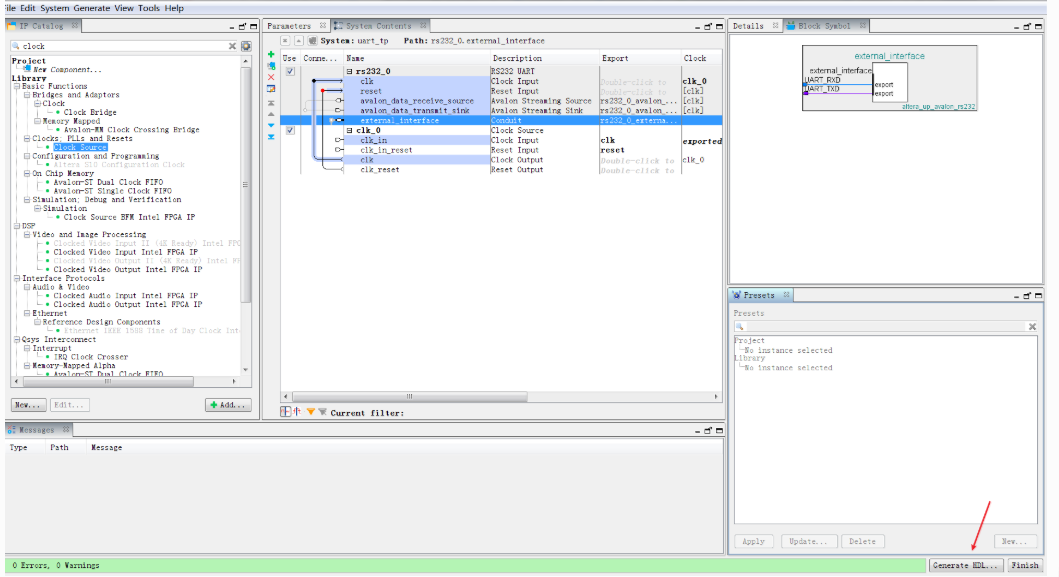

5、打开系统连接的界面,为其添加时钟输入模块。

6、在IP搜索栏搜索clock,双击选择的模块添加时钟模块,输入模块。

7、根据板载资源,设置时钟的参考时钟。

8、连接时钟模块和串口模块的clk和reset。

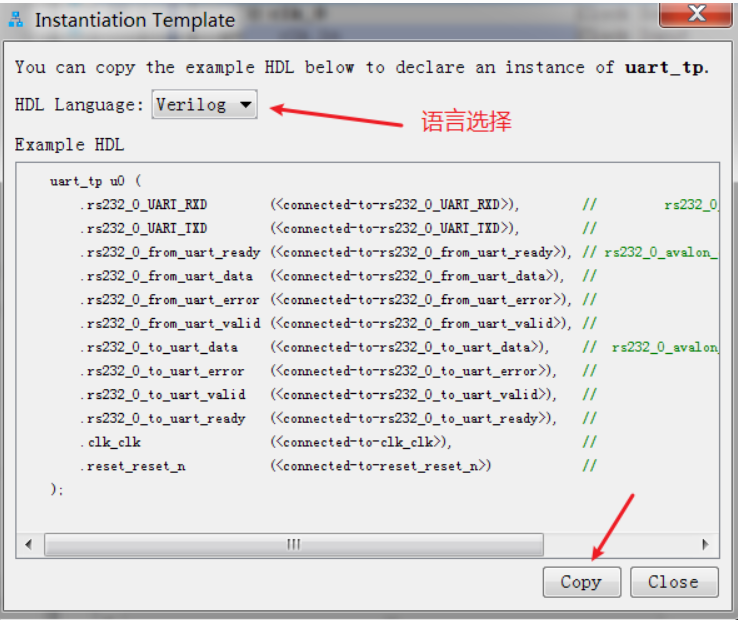

9、点击Generate HDL生成模块。

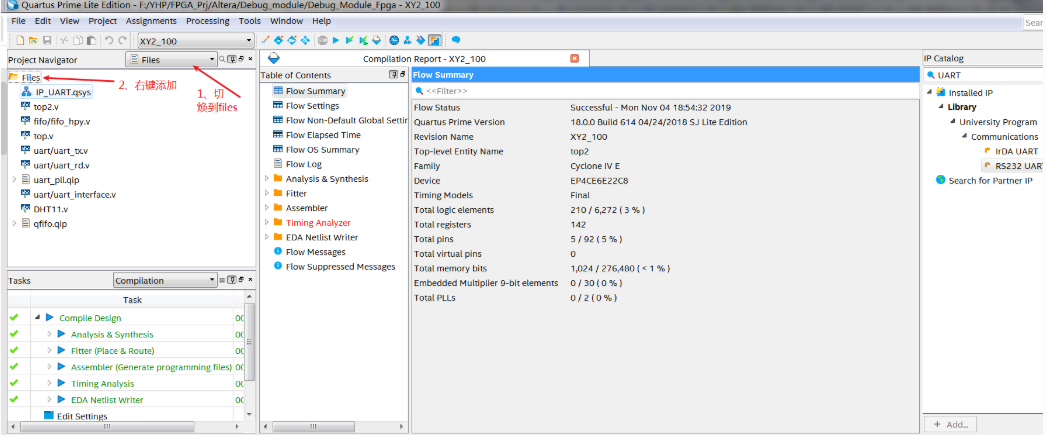

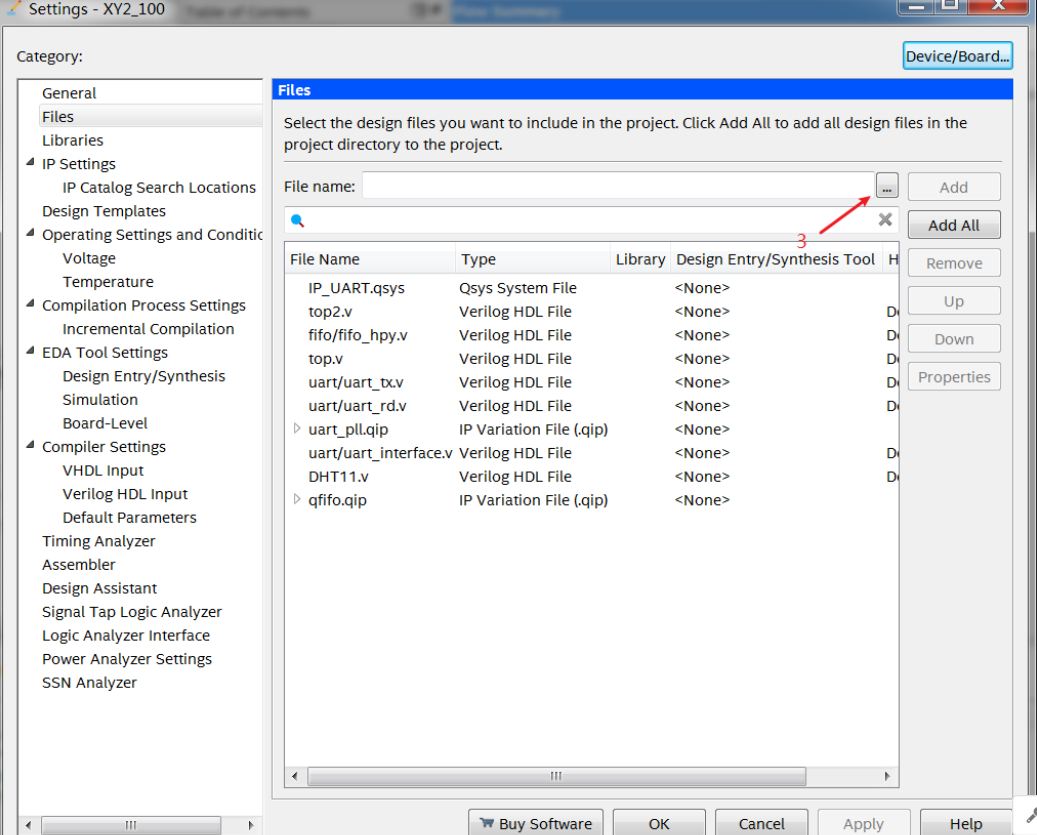

10、在quartus中添加生成的sys系统。

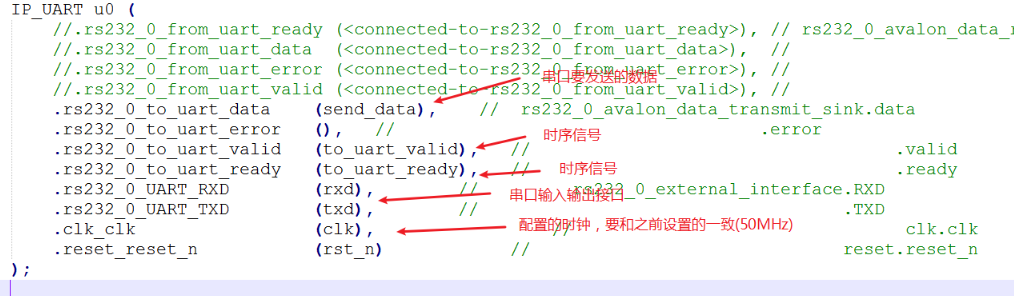

11、从platform designer生成模块实例将实例拷贝到添加到quartus的顶层文件中,添加写数据和读数据的时序。

修改说明:rs232_0_UART_RXD信号为输出信号,指示uart模块是否就绪!

这里只测试一下串口发送数据的功能,接收数据的操作基本是一样的。

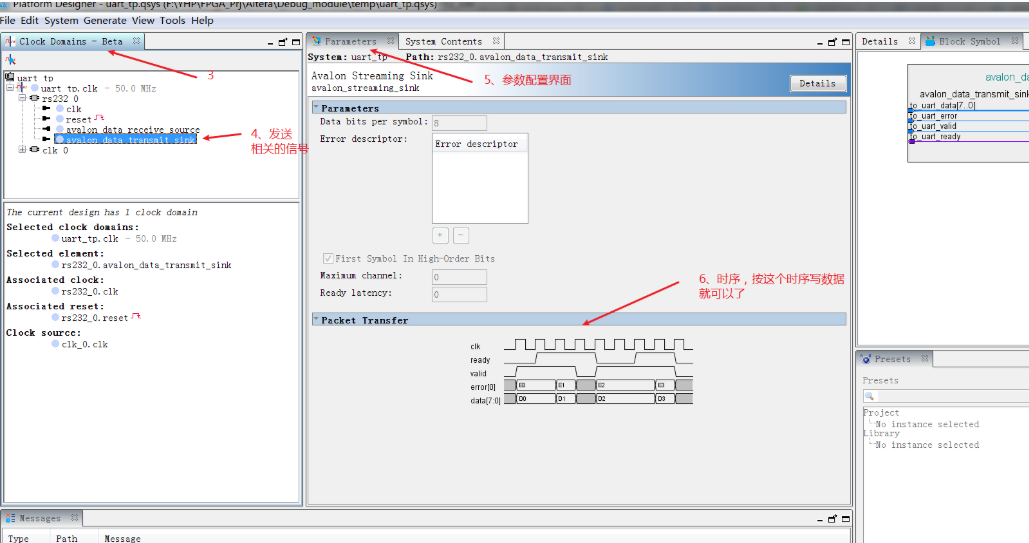

12、在platform designer查看串口模块发送数据的时序。

同理在这里一样可以查看到接收数据的时序。需要注意的是,时序中的数据其实是在to_uart_valid信号为1时,数据会被写入。下面是测试串口发送数据的顶层文件。

module top2(

input wire clk,//50MHz时钟

//rst,//

output reg led, //用于指示

input wire rxd,

output wire txd,

inout dht_io

);

//*********************************PROCESS**************************************

// 复位模块

//******************************************************************************

reg rst_n ;

reg [15:0]delay_cnt;

always@(posedge clk)

begin

if(delay_cnt>=16'd35530)begin

delay_cnt <= delay_cnt;

rst_n <= 1'b1;

end

else begin

rst_n <= 1'b0;

delay_cnt <= delay_cnt + 1'b1;

end

end

//指示灯

//assign txd = led;

reg [31:0]cnt;

reg led_f1,tx_flag;

always@(posedge clk)

begin

led_f1 <= led;

tx_flag <= led &(~led_f1);

if(cnt >= 32'd25000000 - 1)

begin

cnt <= 0;

led <=~led;

end

else begin

cnt <= cnt + 1'b1 ;

end

end

//--------------------------------------------

localparam s_s1=0;

localparam s_s2=1;

localparam s_s3=2;

localparam s_s4=3;

reg [7:0]send_data;

reg to_uart_valid ;

wire uart_ready;

reg [2:0]send_st;

reg [7:0]data_cnt;

always@(posedge clk)

begin

if(!rst_n)begin

to_uart_valid <= 1'b0;

send_data <= 8'd0;

send_st<= s_s1;

data_cnt <= 8'd0;

end

else begin

case(send_st)

s_s1:begin//待机

if(tx_flag)begin

send_st <= s_s2;

to_uart_valid <= 1'b0;

data_cnt <= 8'd0;

send_data <= 9;

end

else begin

to_uart_valid <= 1'b0;

end

end

s_s2:begin

if(data_cnt <= 8'd8-1'b1 && uart_ready )begin

to_uart_valid <= 1'b1;

send_data <= data_cnt+1;

data_cnt <= data_cnt + 1'b1;

send_st <= (data_cnt >= 8'd5-1)?s_s3:s_s2;

end

end

s_s3:begin

to_uart_valid <= 1'b0;

send_st <= s_s1;

data_cnt<=8'd0;

end

default :send_st <= s_s1;

endcase

end

end

IP_UART u0 (

//.rs232_0_from_uart_ready (<connected-to-rs232_0_from_uart_ready>), // rs232_0_avalon_data_receive_source.ready

//.rs232_0_from_uart_data (<connected-to-rs232_0_from_uart_data>), // .data

//.rs232_0_from_uart_error (<connected-to-rs232_0_from_uart_error>), // .error

//.rs232_0_from_uart_valid (<connected-to-rs232_0_from_uart_valid>), // .valid

.rs232_0_to_uart_data (send_data), // rs232_0_avalon_data_transmit_sink.data

.rs232_0_to_uart_error (), // .error

.rs232_0_to_uart_valid (to_uart_valid ), // .valid

.rs232_0_to_uart_ready (uart_ready), // 这是输出信号, 用于指示uart是知否就绪 .ready

.rs232_0_UART_RXD (rxd), // rs232_0_external_interface.RXD

.rs232_0_UART_TXD (txd), // .TXD

.clk_clk (clk), // clk.clk

.reset_reset_n (rst_n) // reset.reset_n

);

endmodule