转载来自:http://blog.csdn.net/shanghaiqianlun/article/details/6976804

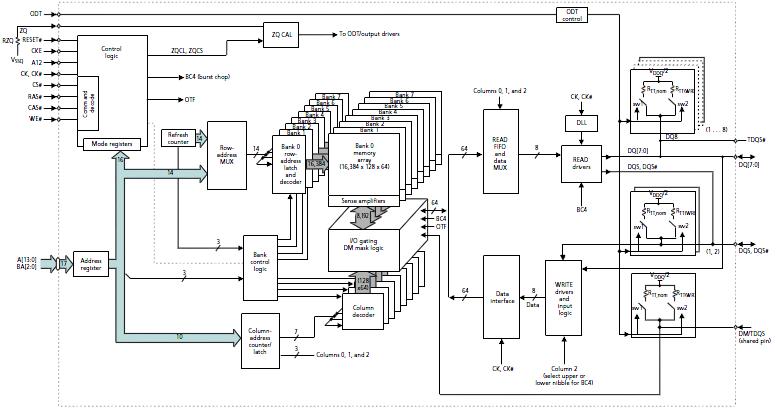

1.结构框图:

2.管脚功能描述

|

管脚符号 |

类型 |

描述 |

|

A0-A9,A10/AP,A11,A12/BC#,A13 |

Input |

地址输入。为ACTIVATE命令提供行地址,和为READ/WRITE命令的列地址和自动预充电位(A10),以便从某个bank的内存阵列里选出一个位置。A10在PRECHARGE命令期间被采样,以确定PRECHARGE是否应有于某个bank:A10为低,这个bank由BA[2:0]来选择,或者A10为高,对所有bank。在LOAD MODE命令期间,地址输入提供了一个操作码。地址输入的参考是VREFCA。A12/BC#:在模式寄存器(MR)使能的时候,A12在READ和WRITE命令期间被采样,以决定burst chop(on-the-fly)是否会被执行(HIGH=BL8执行burst chop),或者LOW-BC4不进行burst chop。 |

|

BA0,BA1,BA2 |

Input |

Bank地址输入。定义ACTIVATE、READ、WRITE或PRECHARGE命令是对那一个bank操作的。BA[2:0]定义在LOAD MODE命令期间哪个模式(MR0、MR1、MR2)被装载,BA[2:0] 的参考是VREFCA |

|

CK,CK# |

Input |

时钟。差分时钟输入,所有控制和地址输入信号在CK上升沿和CK#的下降沿交叉处被采样,输出数据选通(DQS、DQS#)参考与CK和CK#的交叉点。 |

|

CKE |

Input |

时钟使能。使能(高)和禁止(低)内部电路和DRAM上的时钟。由DDR3 SDRAM配置和操作模式决定特定电路被使能和禁止。CKE为低,提供PRECHARGE POWER-DOWN和SELF REFRESH操作(所有Bank都处于空闲),或者有效掉电(在任何bank里的行有效)。CKE与掉电状态的进入退出以及自刷新的进入同步。CKE与自刷新的退出异步,输入Buffer(除了CK、CK#、RESET#和ODT)在POWER-DOWN期间被禁止。输入Buffer(除了CKE和RESET#)在SELF REFRESH期间被禁止。CKE的参考是VREFCA。 |

|

CS# |

Input |

片选。使能(低)和禁止(高)命令译码,当CS#为高的时候,所有的命令被屏蔽,CS#提供了多RANK系统的RANK选择功能,CS#是命令代码的一部分,CS#的参考是VREFCA。 |

|

DM |

Input |

数据输入屏蔽。DM是写数据的输入屏蔽信号,在写期间,当伴随输入数据的DM信号被采样为高的时候,输入数据被屏蔽。虽然DM仅作为输入脚,但是,DM负载被设计成与DQ和DQS脚负载相匹配。DM的参考是VREFCA。DM可选作为TDQS |

|

ODT |

Input |

片上终端使能。ODT使能(高)和禁止(低)片内终端电阻。在正常操作使能的时候,ODT仅对下面的管脚有效:DQ[7:0],DQS,DQS#和DM。如果通过LOAD MODE命令禁止,ODT输入被忽略。ODT的参考是VREFCA |

|

RAS#,CAS#,WE# |

Input |

命令输入,这三个信号,连同CS#,定义一个命令,其参考是VREFCA |

|

RESET# |

Input |

复位,低有效,参考是VSS,复位的断言是异步的。 |

|

DQ0-DQ7 |

I/O |

数据输入/输出。双向数据,DQ[7:0]参考VREFDQ |

|

DQS,DQS# |

I/O |

数据选通。读时是输出,边缘与读出的数据对齐。写时是输入,中心与写数据对齐。 |

|

TDQS,TDQS# |

Output |

终端数据选通。当TDQS使能时,DM禁止,TDQS和TDDS提供终端电阻。 |

|

VDD |

Supply |

电源电压,1.5V+/-0.075V |

|

VDDQ |

Supply |

DQ电源,1.5V+/-0.075V。为了降低噪声,在芯片上进行了隔离 |

|

VREFCA |

Supply |

控制、命令、地址的参考电压。VREFCA在所有时刻(包括自刷新)都必须保持规定的电压 |

|

VREFDQ |

Supply |

数据的参考电压。VREFDQ在所有时刻(除了自刷新)都必须保持规定的电压 |

|

VSS |

Supply |

地 |

|

VSSQ |

Supply |

DQ地,为了降低噪声,在芯片上进行了隔离。 |

|

ZQ |

Reference |

输出驱动校准的外部参考。这个脚应该连接240ohm电阻到VSSQ |

3.状态图:

ACT = ACTIVATE PREA = PRECHARGE ALL SRX = 自刷新推出

MPR = 多用处寄存器 READ = RD,RDS4,RDS8 WRITE=WR,WRS4,WRS8

MRS=模式寄存器集 READ AP=RDAP,RDAPS4,RDAPS8 WRITE=WRAP,WRAPS4,WRAPS8

PDE=掉电进入 REF=REFRESH ZQCL=ZQ LONG CALIBRATION

PDX=掉电推出 RESET=启动复位过程 ZACS=ZA SHORT CALIBTATION

PRE=预充电 SRE=自刷新进入

4. 基本功能

DDR3 SDRAM是高速动态随机存取存储器,内部配置有8个BANK。DDR3 SDRAM使用8n预取结构,以获得高速操作。8n预取结构同接口组合起来以完成在I/O脚上每个时钟两个数据字的传输。DDR3 SDRAM的一个单次读或写操作由两部分组成:一是在内部DRAM核中进行的8n位宽四个时钟数据传输,另一个是在I/O脚上进行的两个对应n位宽、半时钟周期的数据传输。

对DDR3 SDRAM的读写操作是有方向性的突发操作,从一个选择的位置开始,突发长度是8或者是一个以编程序列的长度为4的Chopped突发方式。操作开始于Active命令,随后是一个Read/Write命令。Active命令同时并发含带地址位,以选择Bank和Row地址(BA0-BA2选择BANK、A0-A15选择Row)。而Read/Write命令并发含带突发操作的起始Column地址,并确定是否发布自动预充电命令(通过A10)和选择BC4或BL8模式(通过A12)(如果模式寄存器使能)。

在正常操作之前,DDR3 SDRAM必要以预先定义的方式上电和初始化。