异步复位同步释放

简介

在实际的工程中选择复位策略之前必须考虑许多设计方面的问题,如使用同步复位或者异步复位或者异步复位同步释放(Asynchronous Reset Synchronous Release或者Synchronized Asynchronous Reset),以及是否每一个触发器都需要进行复位。复位的基本目的是使器件进入到可以稳定工作的确定状态,这避免了器件在上电后进入到随机状态导致跑飞了。在实际设计过程中,设计者必须选择最适合于设计本身的复位方式。

同步复位

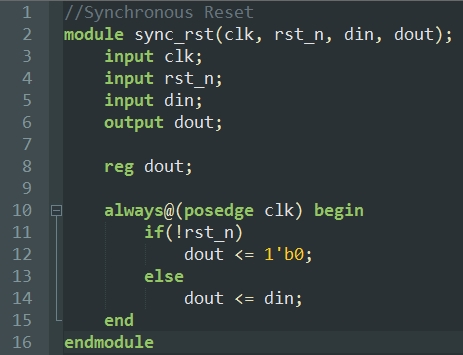

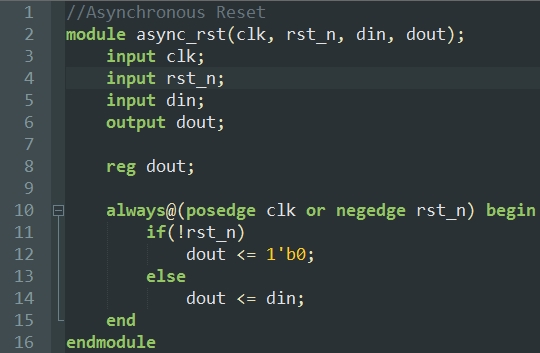

同步复位就是指复位信号只有在时钟上升沿到来时,才能有效。同步复位RTL代码:

综合后的RTL图如下:

异步复位

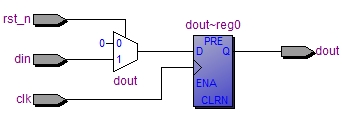

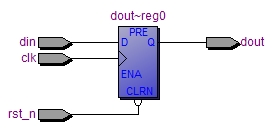

异步复位是指无论时钟沿是否到来,只要复位信号有效,就对系统进行复位。异步复位RTL代码:

综合后的RTL图如下:

对比两者综合后的RTL视图,发现同步复位会多使用一些逻辑单元,这是因为Altera的元件库中的触发器带有异步复位端。

同步复位与异步复位的优缺点

同步复位的优点:

- 一般能够确保电路是百分之百同步的。

- 确保复位只发生在有效时钟沿,可以作为过滤掉毛刺的手段。

同步复位的缺点:

- 复位信号的有效时长必须大于时钟周期,才能真正被系统识别并完成复位。同时还要考虑如:时钟偏移、组合逻辑路径延时、复位延时等因素。

- 由于大多数的厂商目标库内的触发器都只有异步复位端口,采用同步复位的话,就会耗费较多的逻辑资源。

异步复位优点:

- 异步复位信号识别方便,而且可以很方便的使用全局复位。

- 由于大多数的厂商目标库内的触发器都有异步复位端口,可以节约逻辑资源。

异步复位缺点:

- 复位信号容易受到毛刺的影响。

- 复位结束时刻恰在亚稳态窗口内时,无法决定现在的复位状态是1还是0,会导致亚稳态。

异步复位同步释放

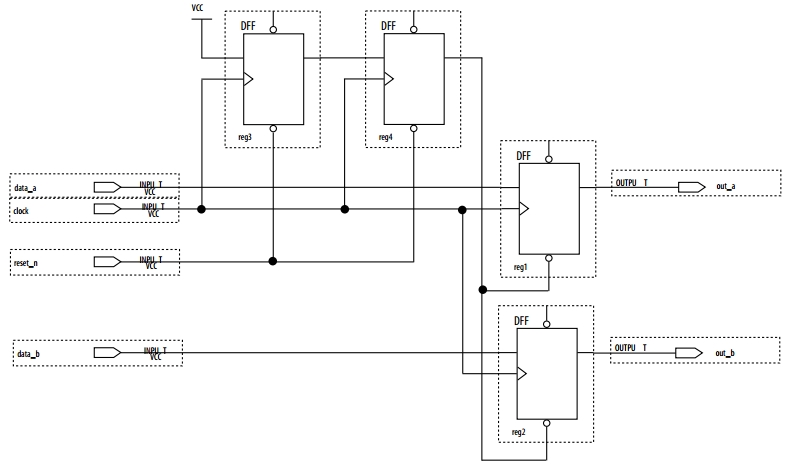

使用异步复位同步释放就可以消除上述缺点。所谓异步复位,同步释放就是在复位信号到来的时候不受时钟信号的同步,而是在复位信号释放的时候受到时钟信号的同步。异步复位同步释放的原理图和代码如下:

1 //Synchronized Asynchronous Reset 2 module sync_async_reset ( 3 input clock, 4 input reset_n, 5 input data_a, 6 input data_b, 7 output out_a, 8 output out_b); 9 10 reg reg1, reg2; 11 reg reg3, reg4; 12 assign out_a = reg1; 13 assign out_b = reg2; 14 assign rst_n = reg4; 15 always @ (posedge clock, negedge reset_n) begin 16 if (!reset_n) begin 17 reg3 <= 1'b0; 18 reg4 <= 1'b0; 19 end 20 else begin 21 reg3 <= 1'b1; 22 reg4 <= reg3; 23 end 24 end 25 26 always @ (posedge clock, negedge rst_n) begin 27 if (!rst_n) begin 28 reg1 <= 1'b0; 29 reg2 <= 1'b0; 30 end 31 else begin 32 reg1 <= data_a; 33 reg2 <= data_b; 34 end 35 end 36 endmodule // sync_async_reset