Altera FFT核使用详解

简介

快速傅里叶变换(Fast Fourier Transform)最为一种高效的算法,被广泛的用于信号处理与数据分析等领域。对于设计工程师来讲,自己动手采样可编程语言来实现一个FFT/IFFT模块,不知要花费多少心血。所幸的是Altera和Xilinx两大巨头都提供了自己FFT核,本文将详细讲解如何使用Altera的FFT核。

Altera FFT核

FFT IP core的总体架构分析:FFT分为fixed transform size architectture 和 variable streaming architecture。variable streaming architecture下又分为radix 2 和radix 4两种运算结构,而内部数据运算表达方式可分为fixed point ,floating point 和block floating point三种。

IO数据流支持流(Streaming)、可变流(Variable Streaming)、缓存突发(Buffered Burst)和突发(Burst)等I/O数据流结构。流FFT结构可以连续处理输入的数据和输出连续的复数数据流,不需要在FFT快内或模块外暂停数据流。突发缓存结构和突发结构的FFT比流FFT结构所需资源更少,但代价是平均块吞吐量下降。

指定FFT复数乘法的实现结构,可包括4 Mults/2 Adders 和 3 Mults/5 Adders。前者使用DSP块结构最小化逻辑资源的使用,但最大化DSP块的使用,这种结构能够提高FFT的最大频率;后者要求的DSP块较少,但需要更多的逻辑资源,得到的FFT的最大频率也相对低些。如果勾选Implement appropriate logic function in RAM则表示使用内嵌的RAM块实现内部逻辑功能,例如FFT中的抽头延迟线,该选项可以减少逻辑资源的使用。

Quartus II提供GUI界面来配置参数,按照以下步骤操作,进可完成功能仿真。

- 建立工程,根据GUI界面完成FFT核配置参数

- 设置好仿真工具(在Quartus工具栏Options下选择EDA Tools Options),编译。

- 执行工程目录下的Tcl文件,然后启动仿真

当完成功能仿真后,会发现得到数据和Matlab仿真的结果相差比较大,因为功能仿真的结果需要按照公式

案例

实际工程中,需要我们编写逻辑来控制FFT核。IFFT是OFDM基带发送部分的关键,下面给出怎么实现IFFT变换。配置参数为:点数N为64、流水线结构、输入输出位宽16bit、输入输出为自然顺序、Quad Output(4 输出)。

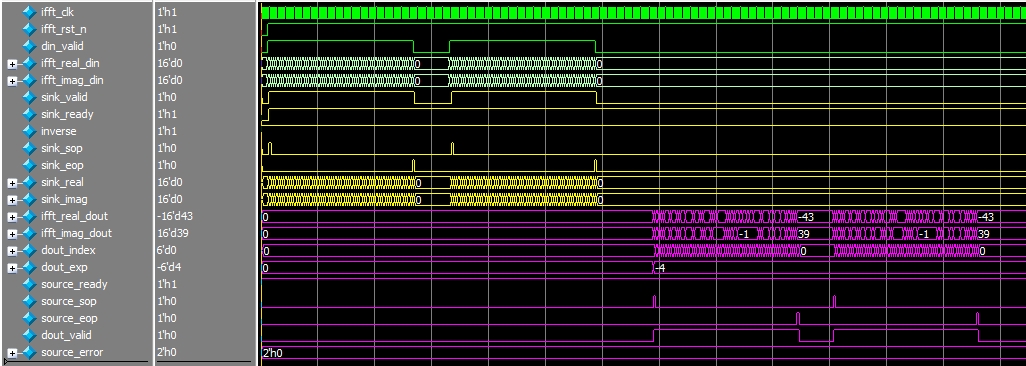

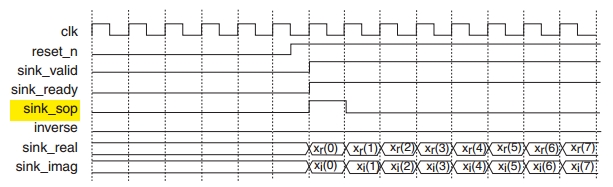

上图是流水线结构的输入时序。在reset信号无效后,将sink_valide置为高有效,表示输入端至少有N个复数据样点可以输入。当sink_ready(FFT核输出的)信号为高电平,表明有能力接收这些输入数据。同时将sink_sop(start)信号置为高电平,表示输入一帧数据(64)的开始,当最后一个数据输入后,sink_eop 被置为高电平 ,表示完成这一帧数据的传输。一定要控制好sink_valid、sink_sop、sink_eop三个信号的时序,否则会导致没有输出或者输出数据出错(笔者曾遇到过)。下图为功能仿真波形图: