Modelsim与Simulink协同仿真

当使用硬件描述语言(HDL)完成电路设计时,往往需要编写Testbench对所设计的电路进行仿真验证,测试设计电路的功能是否与预期的目标相符。而编写Testbench难度之大,这时可以借助交互式图形化环境Simulink来产生模拟激励,并且可以观察测试模块的输出响应。

首先,用Verilog描述一个反相器,代码如下:

module inverter(clk,sin,sout);input clk ;input [7:0] sin ;output [7:0] sout ;reg [7:0] sout;always@(posedge clk)sout <= ~ sin;endmodule

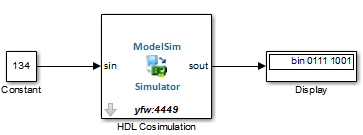

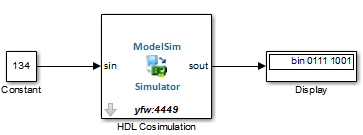

在modelsim分别输入命令vlib work;vmap work work;vlog interver.v 编译成功后,启动Simulink建立模型,模型如下。注意Matlab和Modelsim的工作路径要保持一致。

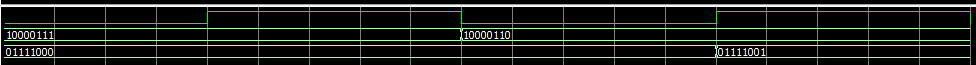

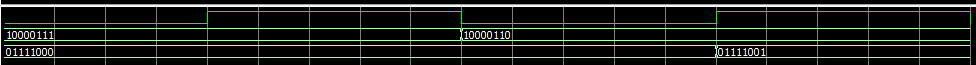

模块HDL Cosimulation位于HDL Verifier库中For use with Mentor Graphics Modelsim子库中。双击HDL Cosimulation进行相关参数设置,并对Simulink模块进行仿真参数设置。点击Simulation--Start开始仿真。Modelsim多次仿真结果如下

另外,Simulink还提供了比较直观的cosimWizard命令来配置协同仿真。具体使用说明参见HDL Cosimulation Wizard Tutorials(doc cosimWizard)

参考资料及工程文件见:http://pan.baidu.com/s/1i3jdigp 提取码8zyf