[ Layout ] 闩锁效应(Latch-up)产生机制和版图优化方法

https://www.cnblogs.com/yeungchie/

前置知识

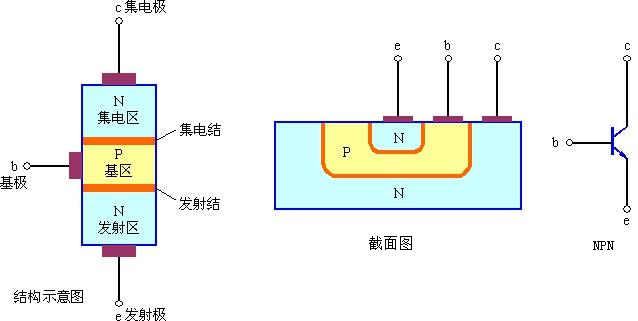

BJT

双极结型晶体管(Bipolar Junction Transistor)

BJT为三端器件,包括:基极(Base)、集电极(Collector)和发射极(Emitter),工作时多子和少子都参与运行,因此成为双极型晶体管。

其中集电区和基区之间有集电结,发射区和基区之间有发射结。在制造工艺上,发射区掺杂浓度最高,用于发射载流子;基区很薄,而且掺杂浓度最低,用于传送和控制载流子;集电区掺杂浓度低于发射区,且面积大,用于收集载流子。

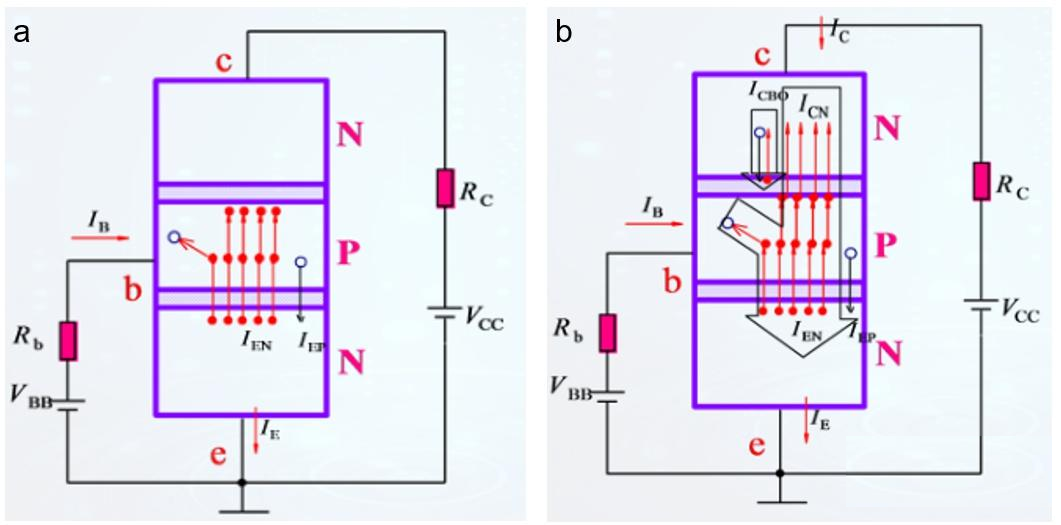

BJT 是电流放大器件,实现用很小的 基极 电流 (\(I_b\)),控制较大的 集电极 电流 (\(I_c\))。放大状态下,发射结正偏,集电结反偏。此时载流子动态过程如下:

-

因为发射结正偏,所以发射区向基区注入电子,形成扩散电流 \(I_{EN}\) 。同时从基区向发射区也有空穴的扩散运动,形成电流 \(I_{EP}\)(这是因为发射区的掺杂浓度远大于基区的掺杂浓度)。但其数量小,可忽略。所以发射极电流 \(I_{E} \approx I_{EN}\)(图a)

-

发射区的电子注入基区后,变成少数载流子。少部分遇到空穴复合掉,形成 \(I_{BN}\)。所以基极电流 \(I_{B} \approx I_{BN}\)。大部分到达了集电极的边缘。

-

因为集电极反偏,收集扩散到集电区边缘的电子,形成电流 \(I_{CN}\)。另外,集电结区的少子会形成漂移电流 \(I_{CBO}\)。

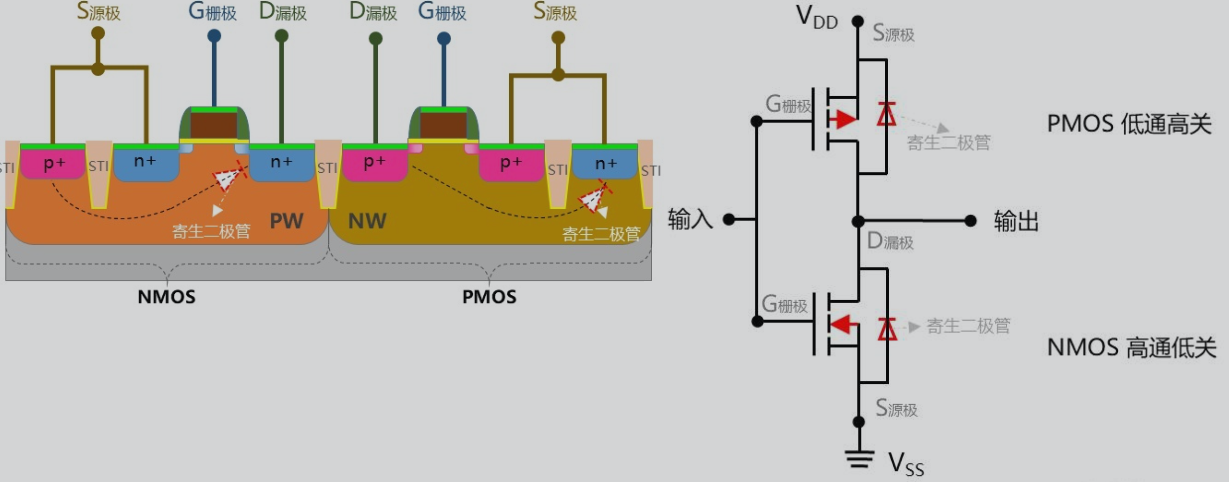

CMOS

Latch-up 原理

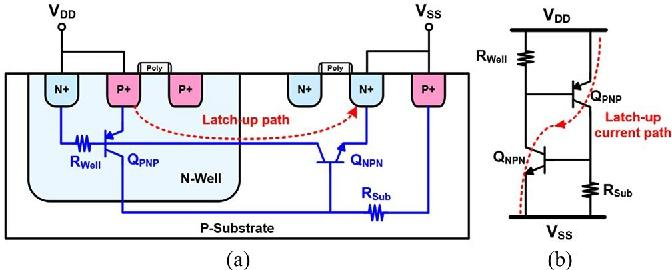

Latch-up 是指 CMOS 芯片中, 在电源 Power(VDD) 和地线 Ground(VSS) 之间由于寄生的 PNP 和 NPN 双极性 BJT 相互影响而产生的一低阻抗通路, 它的存在会使 VDD 和 VSS 之间产生大电流。

Latch-up 最易产生在易受外部干扰的 I/O 电路处, 也偶尔发生在内部电路。

发生条件

-

当两个 BJT 都导通,在 VDD 和 GND 之间产生低阻抗通路

-

两个晶体管反馈回路(feedback loop)增益的乘积大于1( \(\beta_{1} \times \beta_{2} \geqslant 1\))

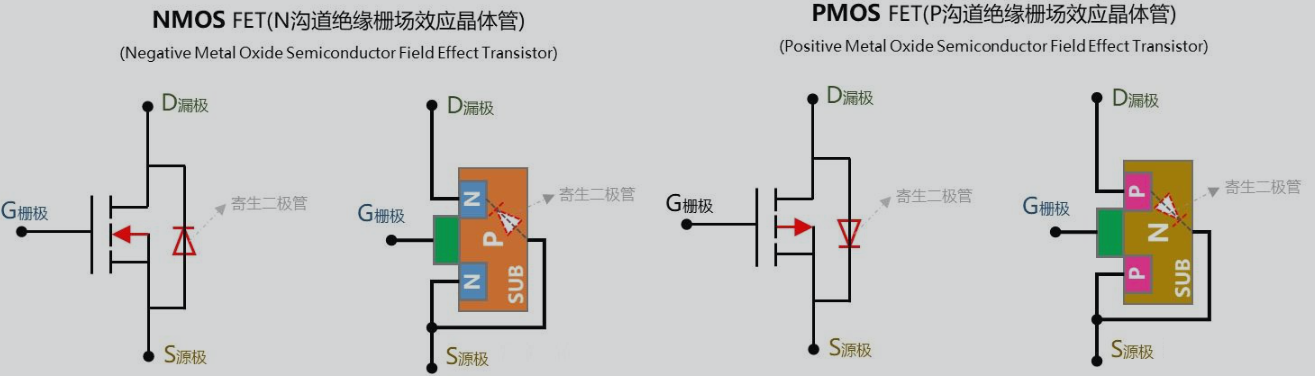

- QPNP 为一垂直式 PNP BJT, 基极是 Nwell, 基极到集电极的电流增益 \(\beta_{1}\) 可达数百倍

- QNPN 是一侧面式的 NPN BJT,基极是 Psub,基极到集电极的电流增益 \(\beta_{2}\) 可达数十倍

- \(R_{Well}\) 是 Nwell 的寄生电阻,其值可以到 \(20k\Omega\)

- \(R_{Sub}\) 是 Psub 电阻,其值从几 \(\Omega\) 到数百 \(\Omega\)

- QPNP 和 QNPN 形成 NPNP 结构,构成可控硅(SCR)电路

当无外界干扰未引起触发时,两个 BJT 处于截止状态,集电极电流是 C-B 的反向漏电流构成,电流增益非常小,此时 Latch-up 不会产生。

当其中一个 BJT 的集电极电流受外部干扰突然增加到一定值时,此时 BJT 的发射结正偏,电流反馈到另一个 BJT,最终的反馈回路引起的电流需要乘以增益 \(\beta_{1} \times \beta_{2}\),此时为 SCR 的触发。从而使两个 BJT 因触发而导通,VDD 至 VSS 间形成低抗通路,Latch-up 由此而产生。

如果 \(\beta_{1} \times \beta_{2} \geqslant 1\) 满足,两个 BJT 将会持续产生高饱和电流,甚至在没有触发条件的时候。

产生机制

-

输入或输出电压(I/O 的信号)高于 VDD 电压,芯片产生大电流,导致 Latch-up

-

ESD 静电加压,可能会从保护电路中引入少量带电载流子到阱或衬底中,导致 Latch-up

解决方法

版图的解决方式

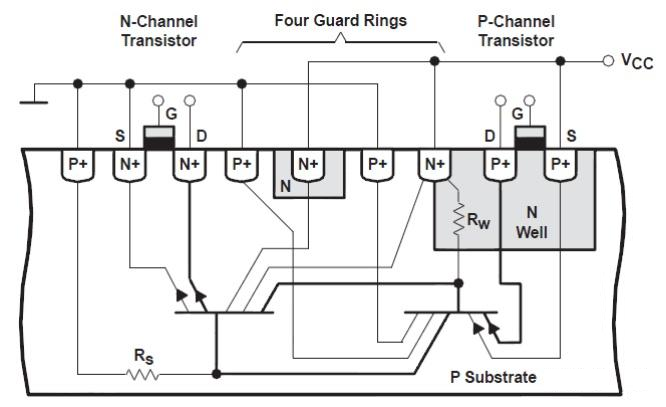

- 增加衬底接触,降低寄生电阻 \(R_{Well}\) 和 \(R_{Psub}\)。

- 增大 NMOS 和 PMOS 有源区间距,使环路增益小于 1,并加入隔离环,双环隔离。

工艺上的解决方法

- 使用重掺杂衬底,降低 PSUB 寄生电阻,减小反馈环路的增益。

- 使用轻掺杂外延层,阻隔 PMOS 区域的寄生 PNP 流向衬底的通路。

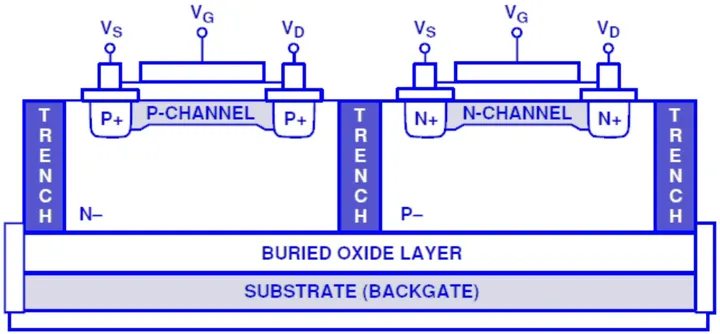

- 使用 SOI 工艺,改变寄生结构,完全解决闩锁问题。

浙公网安备 33010602011771号

浙公网安备 33010602011771号