MSP430G2ET时钟系统

时钟系统

概述

MSP430G2系列单片机主打低功耗,但同时需要满足其他外设的时钟需求,因此内部有多个时钟源可供使用者选择,若要实现低功耗,便可选择低频率,如需要满足高速的外设,便可选择高频率。

时钟源

MSP430G2553共有三大时钟源,三大时钟信号。

时钟源:内部低频时钟源LFXT1 、内部数字控制RC振荡器DCO、外部低频振荡器(需要焊上晶振)

时钟信号:主时钟MCLK;辅助时钟ACLK;子系统时钟SMCLK

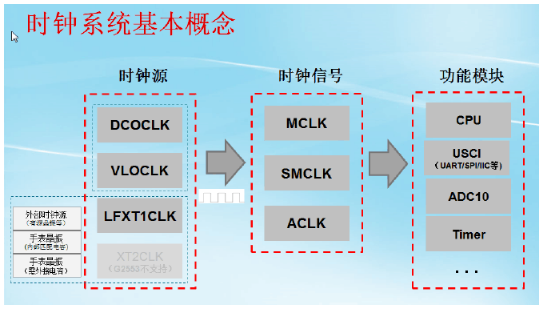

时钟源和时钟信号、外设关系如图所示:

从图中可以看出,所有的时钟均来自时钟源,时钟源经过分频提供时钟信号,时钟信号位CPU、外设提供时钟。

时钟配置

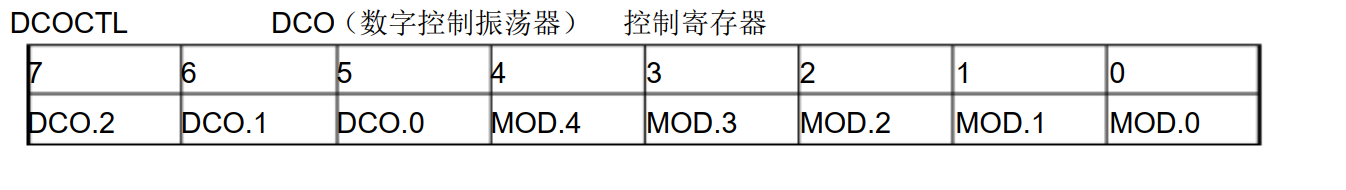

时钟配置主要有两种寄存器完成,即DCOCTL--DCO控制寄存器、BCSCTLx-基本时钟控制寄存器x。

DCO(数字控制振荡器)控制寄存器

DCO.0-DCO.2:定义 8 种频率之一, 可以分段调节 DCOCLK频率,相邻两种频率相差10% ,而频率由注入直流发生器的电流定义;

MOD.0-MOD.4:定义在 32 个 DCO 周期中插入的 Fdco+1 周期个数, 而在下的 DCO周期中为 Fdco 周期,控制改换 DCO和 DCO+1 选择的两种频率。如果 DCO常数为 7,表示已经选择最高频率,此时不能利用 MOD.0-MOD.4 进行频率调整。

DCO频率与标签

| 频率 | 1MHZ | 8MHZ | 12MHZ | 16MHZ |

|---|---|---|---|---|

| 语句 | CALBC1_1MHZ CALDCO_1MHZ | CALBC1_8MHZ CALDCO_8MHZ | CALBC1_12MHZ CALDCO_12MHZ | CALBC1_16MHZ CALDCO_16MHZ |

DCO配置

DCOCTL = 0; // 选择最低 DCOx 和 MODx 设置

BCSCTL1=CALBC1_1MHZ; // 为 1MHZ BCSCTL1 校准数据

DCOCTL=CALDCO_1MHZ; // 为 1MHZ DCOCTL 校准数据,这两句同时使用就使 DCO 设置为 1MHZ

CALBC1_1MHZ==0xFF ; // 校准常数抹去

__bis_SR_register(SCG1 + SCG0) ; // 不用 DCO

Set_DCO(DELTA_1MHZ) ; // 设置 DCO 和获得常量

//BCSCTL1 基本时钟系统控制寄存器 1

//DCOCTL DCO 时钟频率控制寄存器

//CALBC1_1MHZ 这是为 1MHZ BCSCTL1 校准数据时所采用的标签

//CALDCO_1MHZ 这是为 1MHZ DCOCTL 校准数据时所采用的标签

DCO控制寄存器的作用是设置DCO相关参数;BCSCTLx-基本时钟控制寄存器共有三个;

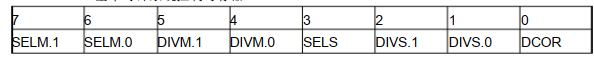

BCSCTL2-基本时钟控制寄存器2

SELM.1 SELM.0 选择 MCLK 时钟源

0 时钟源为 DCOCLK(默认)

1 时钟源为 DCOCLK

2 时钟源为 LFXT1CLK (对于 MSP430F11/12X ) , 时钟源为 XT2CLK(对于 MSP430F13/14/15/16X )

3 时钟源为 LFTXTICLK

DIVM.1 DIVM.0 选择 MCLK 分频

0 1 分频(默认)

1 2 分频2 4 分频

3 8 分频

SELS 选择 SMCLK 时钟源

0 时钟源为 DCOCLK(默认)

1 时钟源为 LFXT1CLK (对于 MSP430F11/12X ) , 时钟源为 XT2CLK(对于 MSP430F13/14/15/16X )

DIVS.1 DIVS.0 选择

分频。

0 1 分频

1 2 分频

2 4 分频

4 8 分频

DCOR 选择 DCO 电阻

0 内部电阻

1 外部电阻

PUC 信号之后, DCOCLK 被自动选择 MCLK 时钟信号,根据需要, MCLK 的时钟源可以另外设置为 LFXT1 或者 XT2

设置顺序如下:

[1] 复位 OscOff

[2] 清除 OFIFG

[3] 延时等待至少 50us

[4] 再次检查 OFIFG,如果仍然置位,则重复 [3] 、 [4] 步骤,直到 OFIFG=0 为止。

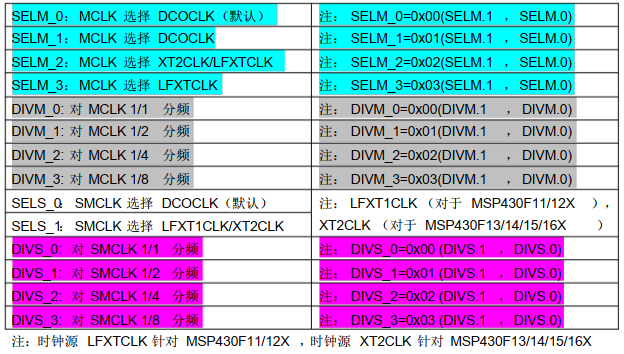

标签对应关系

配置语句

BCSCTL2|=SELM_0+DIVM_0; // 选择 DCOCLK 为 MCLK 的时钟源并且对 MCLK

的时钟源进行 1/1 分频

BCSCTL2|=DIVS_0; // 对 SMCLK 的时钟源进行 1/1 分频

//BCSCTL2 基本时钟系统控制寄存器 2

//SELM_0 BCSCTL2 的第 6、 7 位,对 MCLK 的时钟源进行选择

//DIVM_0 BCSCTL2 的第 4、 5 位,对 MCLK 的时钟源进行分频

//DIVS_0 BCSCTL2 的第 1、 2 位,对 SMCLK 的时钟源进行分频

辅助时钟就不在此陈述。

总的来说,MSP430G2553的时钟系统较为简单,需要注意寄存器的使用。

浙公网安备 33010602011771号

浙公网安备 33010602011771号