F1C100S-ARM926EJ-S一些细节

在2022年使用ARM9开发,很容易和ARM Cortex-A的一些特性搞混,因为ARM9实在是有点老旧,有很多特性并没有,这里记录下ARM926需要注意的地方。

- ARM9采用改进型哈佛结构,指令和数据分属不同的总线,可以并行处理。

- 五级流水线,PC = 当前执行地址 + 8

- 32bit定点RISC处理器,增强性乘法器设计,支持ARM/Thumb指令混合编程(通过BLX指令跳转到thumb代码,前提是cp15-c1[15]:L4标记位需要置0)。

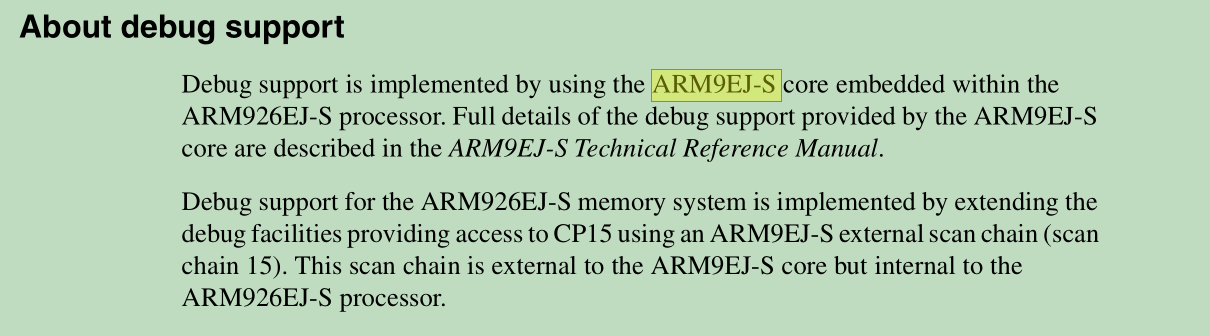

- 支持嵌入式跟踪宏单元,支持实时跟踪指令和数据,实际上是内嵌了个ARM9EJ-S核心,但只支持2个硬件断点。

- 内核中并没有分支预测技术,使得其在运行分支指令时需要清空流水线。

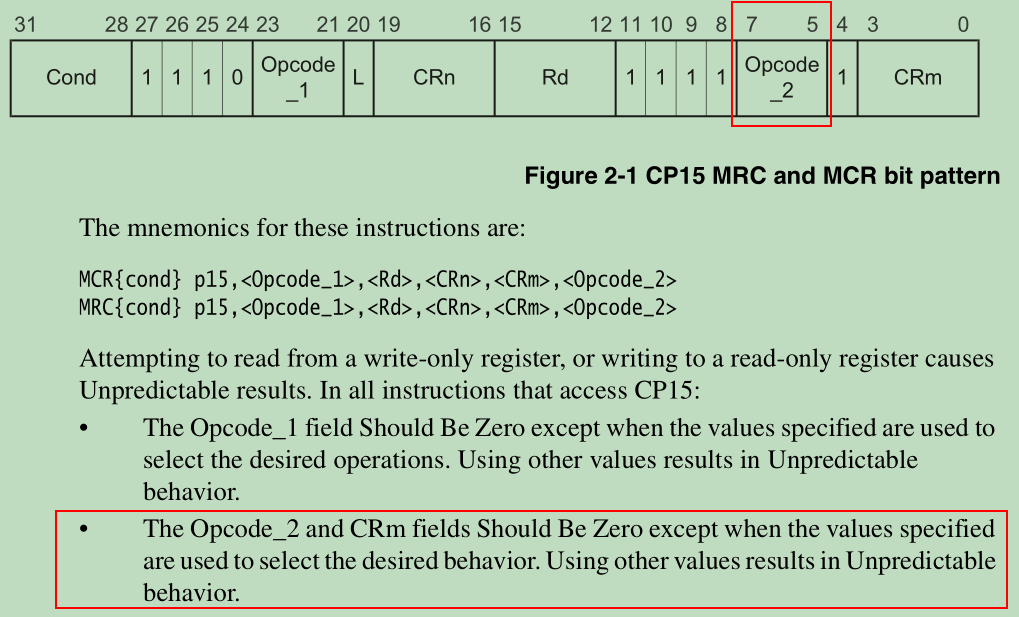

- 在操作CP15协处理器时不能照搬Cortex-A的汇编代码,有相当多的

Opcode_2条件在ARM9中是未定义的。

- ICache: 32kB (4x256x32), DCache: 16kB (4x128x32)

- Cache索引方式为virtual index,virtual tag,切换页表时需要失效整个TLB缓存,代价比较大。

- F1C100S没有配置FPU,编译参数需要填

-msoft-float或-mfloat-abi=soft - ARM926不支持非对齐访问。

- ARMv5t指令集不支持

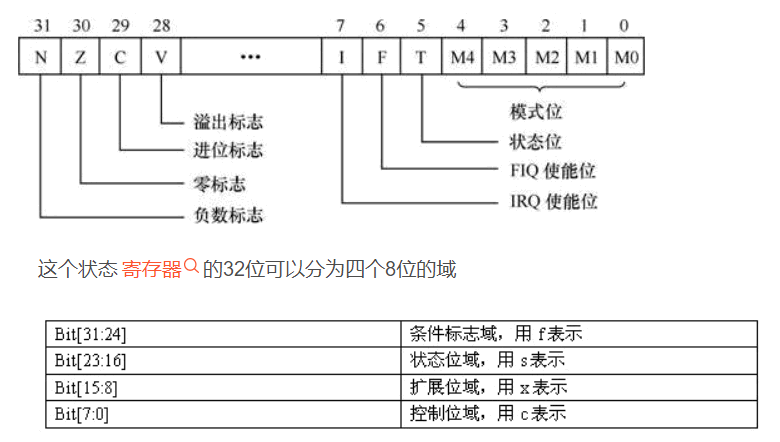

cps指令快速切换处理器状态(armv6及以上支持),沿用armv4的cpsr寄存器分成了4个域,cpsr_c cpsr_x cpsr_s cpsr_f,可以用msr指令加立即数的方式切换,例如msr cpsr_c, #MODE_SVC将处理器切换成SVC模式。