操作系统-进程(6)管程

管程试图抽象相关并发进程对共享变量访问,以提供一个友善的并发程序设计开发环境

管程是由若干公共变量及其说明和所有访问这些变量的过程所组成

管程把分散在各个进程中互斥地访问公共变量的那些临界区集中起来管理,管程的局部变量只能由该管程的过程存取

进程只能互斥地调用管程中的过程

条件变量(condition variables):当调用管程过程的进程无法运行时,用于阻塞进程的信号量

阻塞原语wait:当一个管程过程发现无法继续时(如发现没有可用资源时),它在某些条件变量上执行wait,这个动作引起调用进程阻塞

释放原语signal:用于释放在条件变量上阻塞的进程

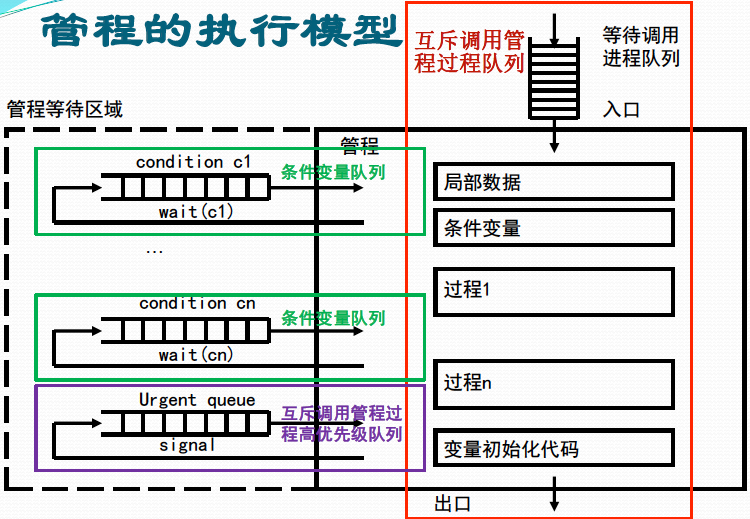

如图,管程过程必须被互斥调用,等待调用管程过程的进程队列必须在互斥调用管程过程队列排队

每个条件变量都对应一个条件变量队列。调用管程过程的进程执行不下去的时候,进入对应条件变量队列等待,并开放管程。

当使用signal释放一个等待进程时,可能出现两个进程同时停留在管程内。解决方法:

(1)执行signal的进程等待,直到被释放进程退出管程或等待另一个条件

(2)被释放进程等待,直到执行signal的进程退出管程或等待另一个条件

被释放的进程在互斥调用管程过程高优先级队列,等待调用管程过程。

霍尔采用了第一种办法;汉森选择了两者的折衷,规定管程过程所执行的signal操作是过程体的最后一个操作,但该方法增加了程序设计的难度

霍尔管程

霍尔管程基于PV操作原语实现:wait和signal可以是程序过程,不需要是原语

可以用语言机制(如通过操作系统程序库或高级程序设计语言在基础的操作系统的PV操作原语上)实现霍尔管程,而不需要扩展操作系统内核

用于管程中过程互斥调用的信号量mutex,初值为1

挂起发出signal()操作的进程的信号量next和计数器next_count

挂起等待资源的进程的信号量x_sem和计数器x_count(假设只有一个共享变量)

霍尔管程实现哲学家就餐问题:

当且仅当哲学家的两个邻座state[(i-1)%5]和state[(i+1)%5]均不为eating时才建立状态state[i]=eating

引入条件变量semaphore self[5],当哲学家i饥饿但又不能获得两把叉子时,进入其信号量等待队列

想吃时调用过程pickup,吃完调用过程putdown。

霍尔管程解决生产者-消费者问题:

霍尔管程解决读者-写者问题:

__EOF__

本文作者:扬羽流风

本文链接:https://www.cnblogs.com/yangyuliufeng/p/9609419.html

关于博主:评论和私信会在第一时间回复。或者直接私信我。

版权声明:本博客所有文章除特别声明外,均采用 BY-NC-SA 许可协议。转载请注明出处!

声援博主:如果您觉得文章对您有帮助,可以点击文章右下角【推荐】一下。您的鼓励是博主的最大动力!

本文链接:https://www.cnblogs.com/yangyuliufeng/p/9609419.html

关于博主:评论和私信会在第一时间回复。或者直接私信我。

版权声明:本博客所有文章除特别声明外,均采用 BY-NC-SA 许可协议。转载请注明出处!

声援博主:如果您觉得文章对您有帮助,可以点击文章右下角【推荐】一下。您的鼓励是博主的最大动力!

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 开发者必知的日志记录最佳实践

· SQL Server 2025 AI相关能力初探

· Linux系列:如何用 C#调用 C方法造成内存泄露

· AI与.NET技术实操系列(二):开始使用ML.NET

· 记一次.NET内存居高不下排查解决与启示

· 被坑几百块钱后,我竟然真的恢复了删除的微信聊天记录!

· 没有Manus邀请码?试试免邀请码的MGX或者开源的OpenManus吧

· 【自荐】一款简洁、开源的在线白板工具 Drawnix

· 园子的第一款AI主题卫衣上架——"HELLO! HOW CAN I ASSIST YOU TODAY

· Docker 太简单,K8s 太复杂?w7panel 让容器管理更轻松!