计算机体系结构

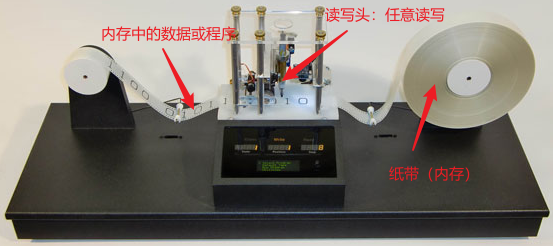

图灵机(Turing Machine)

读写头上有⼀些部件,⽐如存储单元、控制单元以及运算单元:

1、存储单元 ⽤于存放数据;

2、控制单元 ⽤于识别字符是数据还是指令,以及控制程序的流程等;

3、运算单元 ⽤于执⾏运算指令。

不同的架构CPU,指令集不同,支持运行的及其指令也不同,但是有一条是相同的,那就是:

每一种CPU只能支持有限个指令,任何复杂的运算最终都可以分解成有限个基本指令来完成:加、减、乘、除、与、或、非、位移运算或逻辑运算。在计算机上玩游戏、听音乐、看奥运会视频等,这些复杂多变的应用程序,最终都可以分解成CPU所支持的有限个基本指令。

计算机体系结构

指令和数据都需保存,根据保存的方式不同,计算机可以分为两种不同的架构:冯·诺依曼架构 和 哈弗架构

冯·诺依曼架构

冯·诺依曼架构也称为普林斯顿结构。

- 指令和数据存储方式:程序中的指令和数据混合存储,存储在同一块存储器的不同物理地址上

- 特点:结构简单,工程上容易实现,所以现代很多处理器都采用这种架构,如X86、ARM7等。

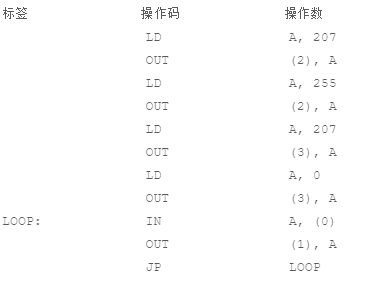

汇编语言的语法由 由 操作码(指令) 和 操作数(指令的对象) 构成

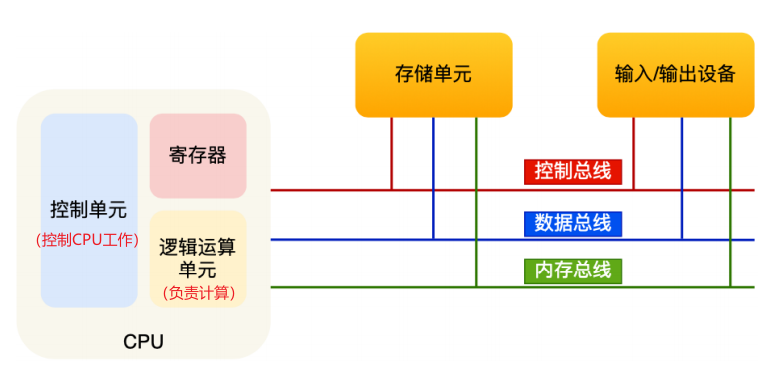

根据上图,可以定义计算机的5个基本部分:中央处理器(CPU)、内存、输入设备、输出设备、总线,这5个部分也被称为冯·诺依曼模型。

-

内存

- 程序和数据都存储在内存,存储的区域是线性的。是由一组动态随机存取存储器(DRAM)组成。

- 数据存储单位是一个二进制位(bit),即0或1。最小的存储单位是字节(byte),1byte=8bit

- 内存地址从0自增,因为有地址的缘故,内存读写任何一个数据速度都是一样的。

-

中央处理器(CPU)

- 32位和64位CPU主要区别在于一次能计算多少字节:

32位CPU一次可以计算4个字节:4字节×8位=32位CPU

64位CPU一次可以计算8个字节:8字节×8位=64位CPU

这里32位和64位通常是指CPU的位宽 - 为什么有了内存还需要寄存器?

因为,一方面,一些寄存器有特殊的作用,例如计数记录地址等,另一方面,内存离CPU太远了,而寄存器就在CPU里面,计算时候速度快些。 - 常见的寄存器种类:

通用寄存器:用来存放需要进行运算的数据,比如需要进行加和运算的两个数据

程序计数器:⽤来存储 CPU 要执⾏下⼀条指令「所在的内存地址」,注意不是存储了下⼀条要执⾏的指令,此时指令还在内存中,程序计数器只是存储了下⼀条指令的地址

指令寄存器:⽤来存放程序计数器指向的指令,也就是指令本身,指令被执⾏完成之前,指令都存储在这⾥。

- 32位和64位CPU主要区别在于一次能计算多少字节:

-

总线

- 贯穿整个系统的是一组电子管道,称作总线,它携带信息字节并负责在各个部件间传递。

通常总线被设计成传送定长的字节块,也就是宇 (word) 。

字中的字节数(即字长)是一个基本的系统参数,各个系统中都不尽相同。

现在的大多数机器字长要么是4个字节 (32位),要么是8个字节 (64 位)。 - 总线用于CPU和内存及其他设备之间的通信,总线可分为3种:

地址总线:用于指定CPU将要操作的地址。

数据总线:用于读写内存的数据。

控制总线:⽤于发送和接收信号,⽐如中断、设备复位等信号,CPU 收到信号后⾃然进⾏响应,这时也需要控制总线。

- 贯穿整个系统的是一组电子管道,称作总线,它携带信息字节并负责在各个部件间传递。

-

输入输出设备

- 一般最常见就是键盘输入、屏幕输出。

哈弗架构

哈弗架构是相对于冯·诺依曼架构的。

- 指令和数据存储方式:程序中的指令和数据分开存储,分别存储在程序存储器和数据存储器

- 特点:每个存储器都独立编址,独立访问,而且指令和数据可以在一个时钟周期内并行访问,所以使用哈弗架构的处理器运行效率更高,8051系列的单片机采用的就是哈弗架构

混合架构

随着科技的发展,现在内存RAM的工作频率跟不上CPU了,往往CPU和内存之间传输数据,CPU执行完了,内存可能刚开始没多久,比如CPU执行一条指令仅需要零点几纳秒,而RAM则需要30纳秒。读写一次RAM的时间,CPU都可以执行几百条指令了,为此,为了减少内存瓶颈(速度更不上CPU)带来的影响,CPU引入了Cache机制:指令Cache和数据Cache,用来缓存指令和数据,以此提高计算机效率。

现代的ARM SoC芯片架构如下

SOC芯片内部采用了哈弗架构,集成了指令Cache和数据Cache。

当CPU到RAM中读取数据时,一次缓存一块地址连续的数据到Cache中,等下次CPU再去取指令和数据的时候,可以先到两个Cache中查找,如果找不到,再去内存中读取;当CPU写数据的时候,也是先把数据暂时存放在Cache中,等待时机一次性刷新到内存中。因此,Cache缓存机制可以大幅提高CPU的访问效率。

SOC芯片外部采用了冯·诺依曼架构,工程实现简单。

参考:

[1]嵌入式C语言自我修养:从芯片、编译器到操作系统/王利涛编著.——北京:电子工业出版社,2021.4

[2]《图解系统》小林coding

[3]深入理解计算机系统(原书第3版)/(美)兰德尔.E.布莱恩特(Randal E.Bryant)等著;龚奕利,贺莲译.——北京:机械工业出版社,2016.7

[4]计算机是怎么跑起来的/(日)矢泽久雄;胡屹译.——北京:人民邮电出版社,2021.4

浙公网安备 33010602011771号

浙公网安备 33010602011771号