最近在使用CycloneII的开发板,但是高版本的Quartus不支持II系列的开发,于是只能用Q11了。好久没玩FPGA了,新建工程的过程中遇到了一些问题,这里把这些问题记下了以便以后查看。

Quartus11.0新建工程项目

1 建立一个空项目

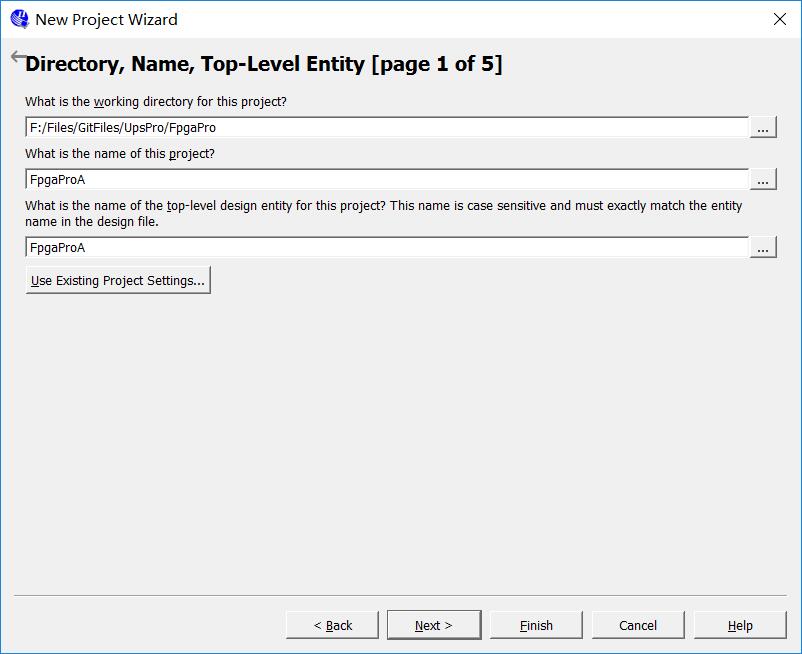

- 依次点击File->New Project Wizard这是采用向导的方式建立一个新的工程项目。当然也可以直接使用File->New,在菜单中选择New QuartusII Project来新建一个项目。采用向导的方式建立项目会一步步引导选择文件夹和芯片等,因此这里建议使用向导的方式建立项目。

- 在点击下一步之后,会出现设置文件夹和项目名称和顶级实体名称的设置界面。这里建议将工程项目名默认和顶层实体名相同。工程的顶层实体名称必须要和设计中的相同不然会报错。

- 下一步选择已有的文件添加到当前工程中,如果没有则直接下一步就行。

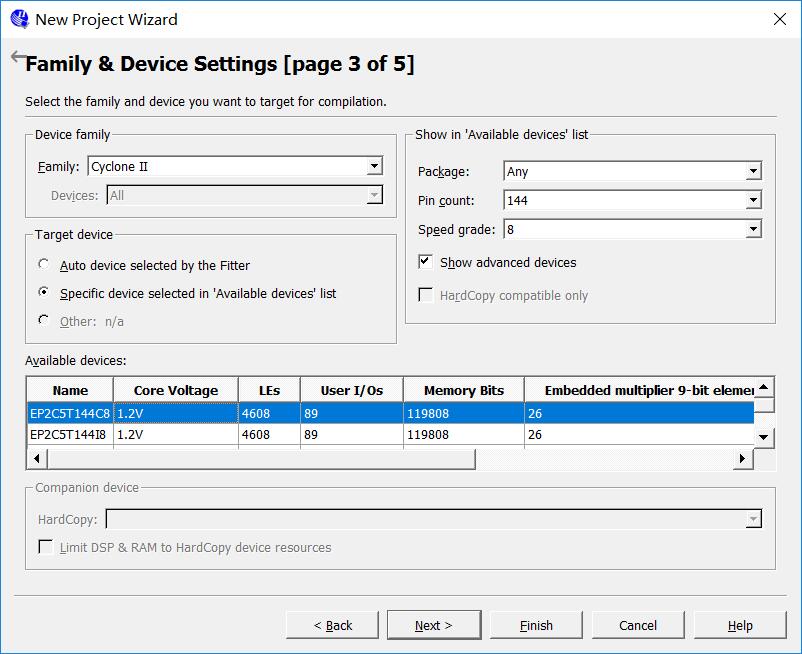

- 选择器件,在选择器件的界面提供了很多的筛选器,比如芯片系列(Device family),封装(Package),引脚数(Pin count)和速度等级(Speed grade).当然也可以不适用筛选器,在已安装中的器件中选择。建议在安装Quartus的时候只安装自己需要使用的器件。

- 选择EDA设计工具,如仿真(simulation),时序分析(Timing Analysis)等。一般我们使用独立的ModelSim进行仿真,这里也直接跳过。

- 最后一般进行确认,如果觉得有问题可以选择上一步(Back)进行调整,如果没有问题直接点击完成(Finish)。

2 新建一个verilog文件并编写输入输出信号

- 选择文件(File)->新建(New),或者使用快捷键(Ctrl+N).选择Verilog HDL File.新建的Verilog文件中的实体(Entity)必须要和在向导中设置的一致否则会报错。默认顶层实体(Top-level entity)和项目名称一致。如果自己修改了而又忘了,可以在Assigments->Settings中General选项卡中查看。

- 定义实体的输入输出如下:

module FpgaProA(

// input

input YULIU , //开关检测,0 -> 整流开关合上

input Q2_ON , //逆变开关输入信号,0 -> 逆变器工作

input BP_ON , //0 -> 需要转旁路

input WG1 , //0 -> 温度过高

input CLK0 , //CLK0

input CLK4 , //CLK4

input [6:1] PWM , //PWM输入

input [3:0] XA , //XA地址总线

input XZCS7n , //DSP片选

...

);

endmodule

需要注意的是,上面是一种推荐的定义输入输出信号的方法。在以前定义输入输出信号还有另外一种形式如下:

module cpld_QQ2812(DSP_Add,DSP_Data,WR,RD,CS1,BUZZER,Key,LED,E,RS,LCD_Data,

PA0,PA1,SLOE,PATEND,SLCS,IFCLK,CLKOUT,SLRD,SLWR,FIFO_PROG,FIFO_FULL,FIFO_EMPTY,

SPI_CS,ACICS,SIDIN,SICLK,IN,OUT,INT1,NMI,EXINT,NMI1,NMI2,TXB,TXB1,RXB,CANRX,CANTX,CANRX_1,CANTX_1);

/*CPLD输入信号的定义*/

input [5:0] DSP_Add; //DSP对CPLD的地址定义

input WR,RD,CS1; //读写和CPLD片选定义

input [7:0] Key; //8个按键定义

input PA0,PA1;

input IFCLK,CLKOUT,FIFO_PROG,FIFO_FULL,FIFO_EMPTY; //USB控制信号定义

input [15:0] IN; //外扩16个IO输入定义

input [4:0] EXINT; //5个外中断定义

...

endmodule

上面这种定义输入输出信号的形式并不推荐,建议使用第一种将信号定义和输入输出类型放在一起的方式。

另外一个需要注意的是,在Quartus11中文件的编码格式为ANSI且不可选,而在高版本的Quartus中编码格式为UTF-8无BOM.因此往往在Quartus11中的中文注释在用其他的文件编辑器中打开往往乱码。这里建议使用Notepad++编写.v文件,因为Notepad++中文件的格式是可选的。如果你已经用Quartus11修改了文件并保存了,可以用Notepad++打开.v文件,改成对应的编码格式即可。

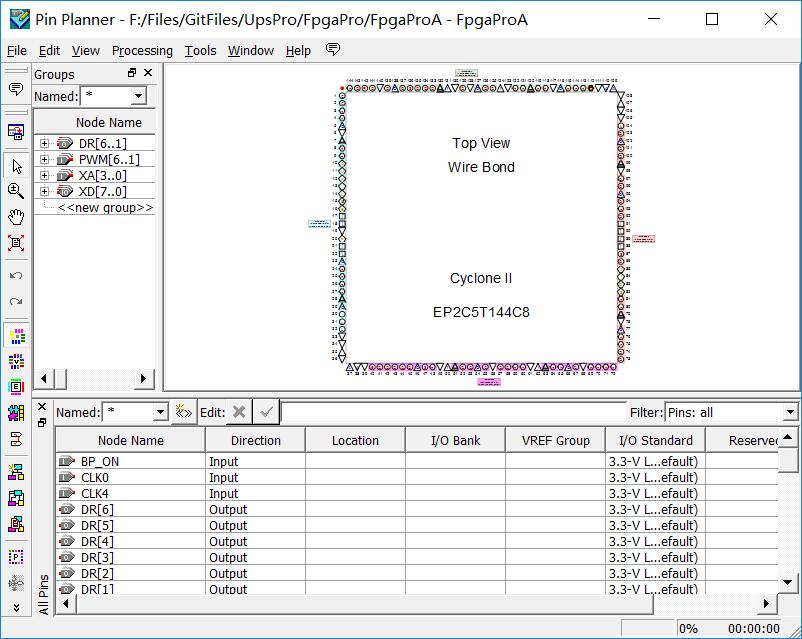

3 分配引脚

在分配引脚之前,首先编译一下程序。此时选择Assigments -> Pin Planner打开引脚配置界面。如果之前没有编译过程序,下面不会出现定义引脚的相关信息。

根据硬件设计将相应的引脚进行配置。

如果你之前已经有相似的工程了,也可以直接使用Assigments -> Import Assigments导入已有的引脚文件。如果项目中需要分配的引脚数较多,建议采用这种方式分配引脚。下面具体介绍几种引脚分配方法。

当然也可以直接使用文本编辑器编辑已有的.pin文件。

3.1.txt文件导入

首先编辑一个.txt文件,格式如下所示:

To,Location

//input

YULIU, PIN_112

Q2_ON, PIN_113

BP_ON, PIN_114

...

然后是由Assigments -> Import Assigments,导入引脚即可。 这种方法简单暴力,强烈推荐。

3.2导入.tcl文件

.tcl文件可以自己用文本编辑器写,也可以首先使用quartus生成一个空白的.tcl文件,然后根据生成的格式编辑,最后在使用上面的方法导入.tcl文件即可。生成空白的.tcl文件方法如下:Assigments -> Pin Planner -> File -> Expert.然后选择文件的格式为.tcl格式即可。

package require ::quartus::project

# 注释

set_location_assignment PIN_112 -to YULIU

set_location_assignment PIN_113 -to Q2_ON

set_location_assignment PIN_114 -to BP_ON

需要注意的是.tcl文件的注释以#开头。然后根据上面的格式继续输入需要编辑的引脚,最后在使用上面的方法导入即可。

3.3导入.csv文件

.csv的文件导入和.tcl文件的导入一样,只是生成空的模板时选择,文件的后缀为.csv即可。这种方法最不推荐。

4 总结及其他注意事项

上面三个步骤完成之后,基本已经建立好模块的框架了,只需添加代码即可。此时编译会出现许多的警告,这些警告大部分都不用理会。如果有兴趣可以在网上进行相应的搜索来解决。这里就不进行相应的介绍了。

浙公网安备 33010602011771号

浙公网安备 33010602011771号