数字IC设计流程与工具

主要内容:

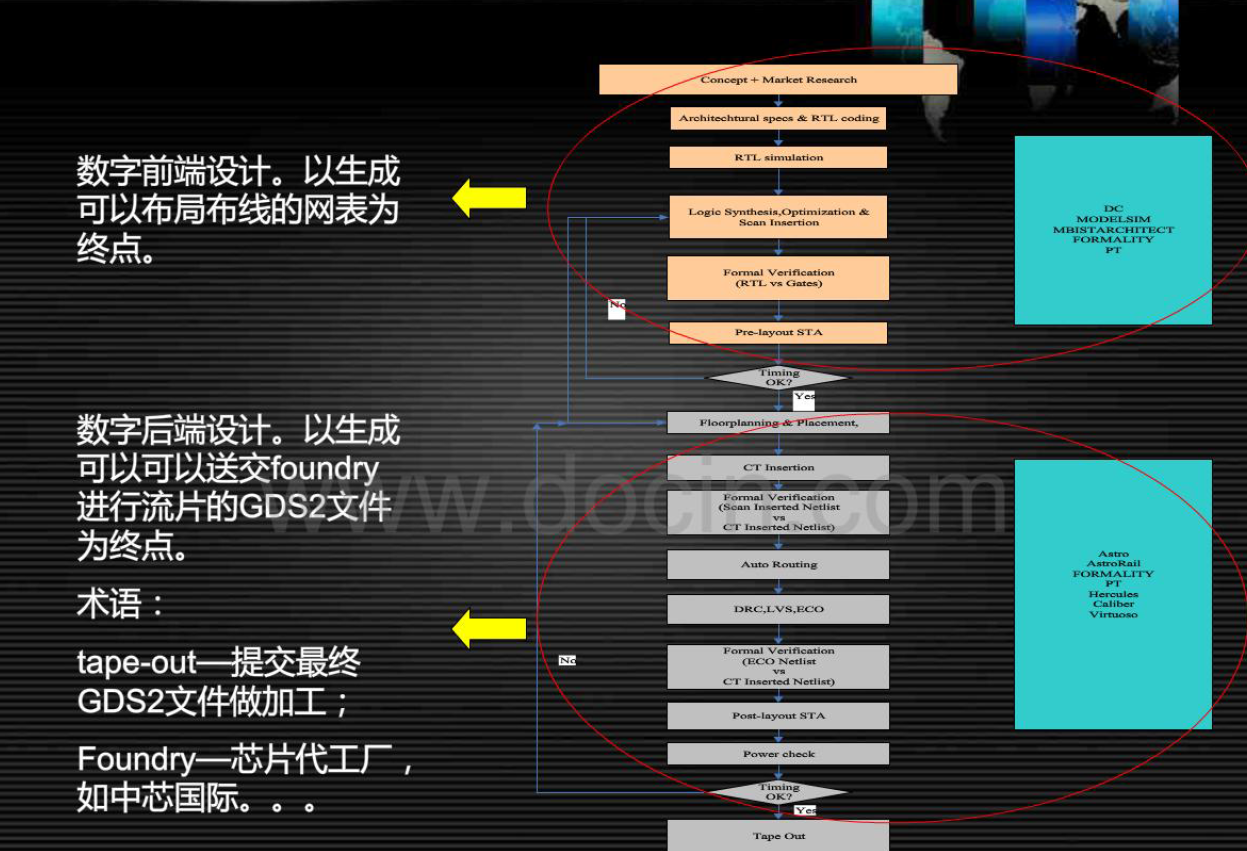

基于标准单元的ASIC设计流程

数字前端设计

数字后端设计

基于Standcell的ASIC设计流程

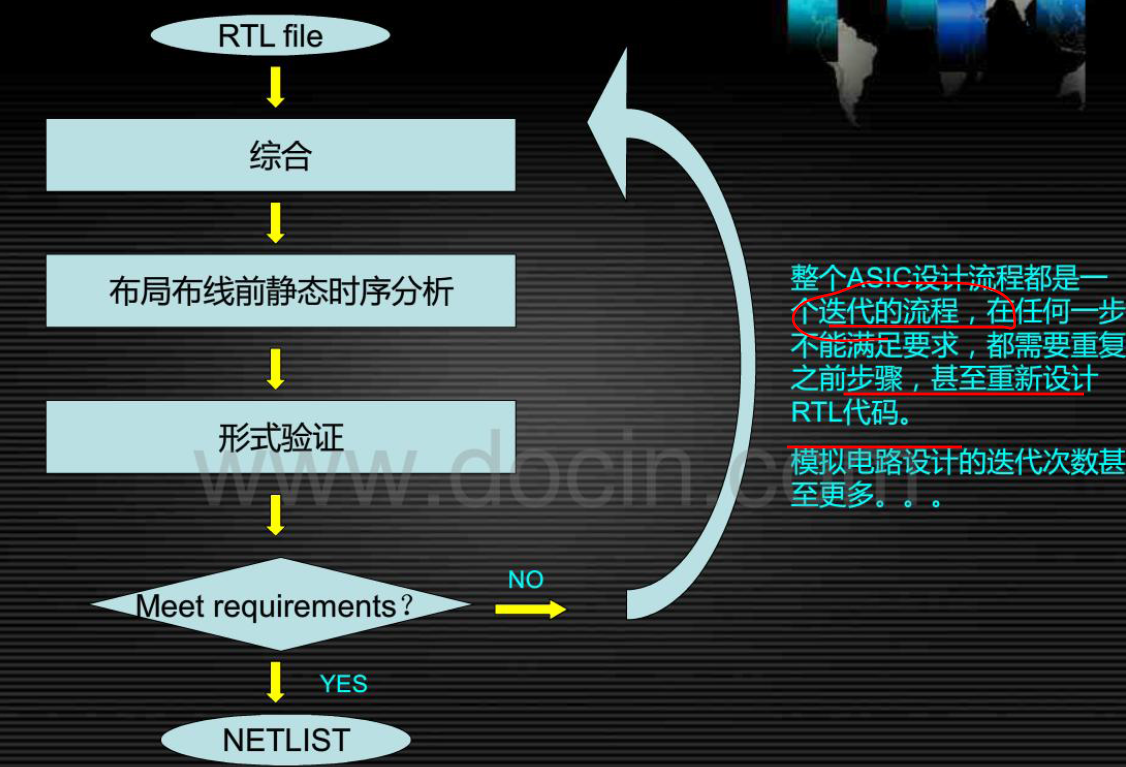

前端设计流程

怎样保证网表的正确性?

1.动态仿真--时间长且覆盖率相对较低

2.形式验证+静态仿真。仿真时间短,覆盖率高

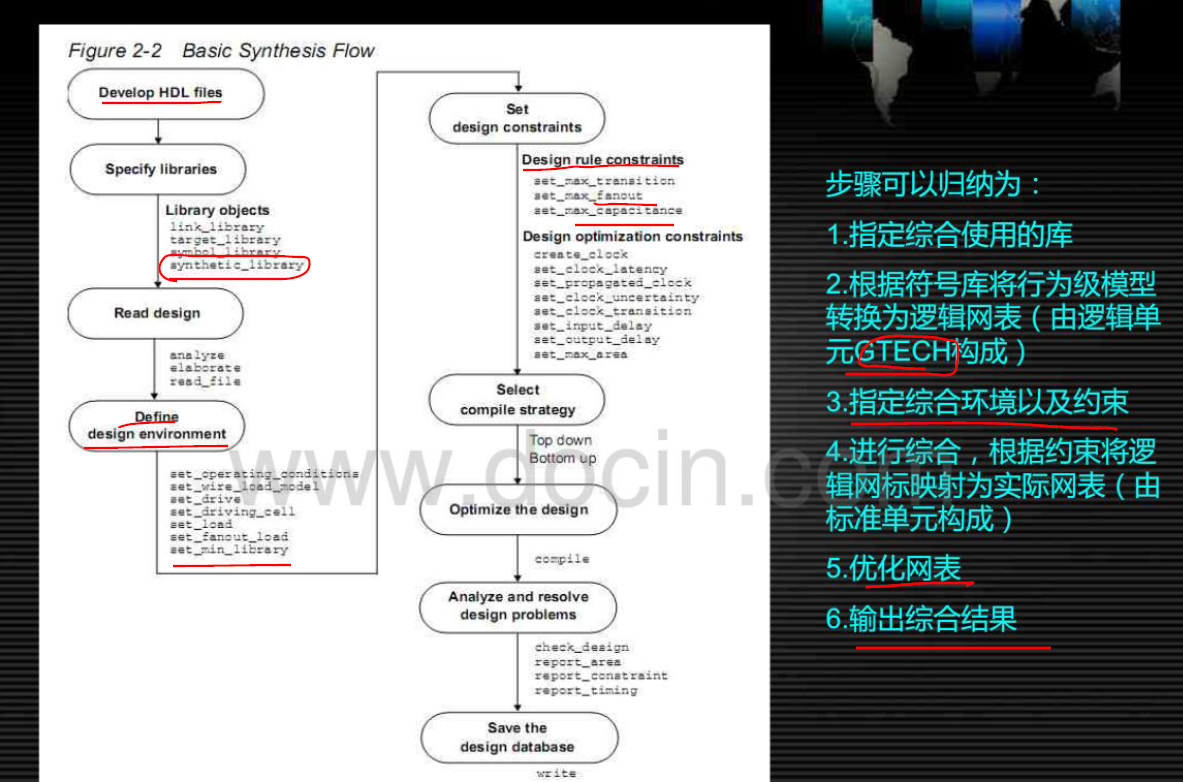

综合流程

Library_objects:

target_librara:工艺库--是综合后电路网表最终映射到的库

link_library:链接库--设置模块或单元电路的引用

symbol_library:符号库--定义了单元电路显示的库

synthetic_library:综合库

Difine design environment:

Define design constrains:定义设计约束

定义规则约束

定义优化约束

在ASIC流程中对于电路进行任何修改过后都应该使用STA工具检查时序。

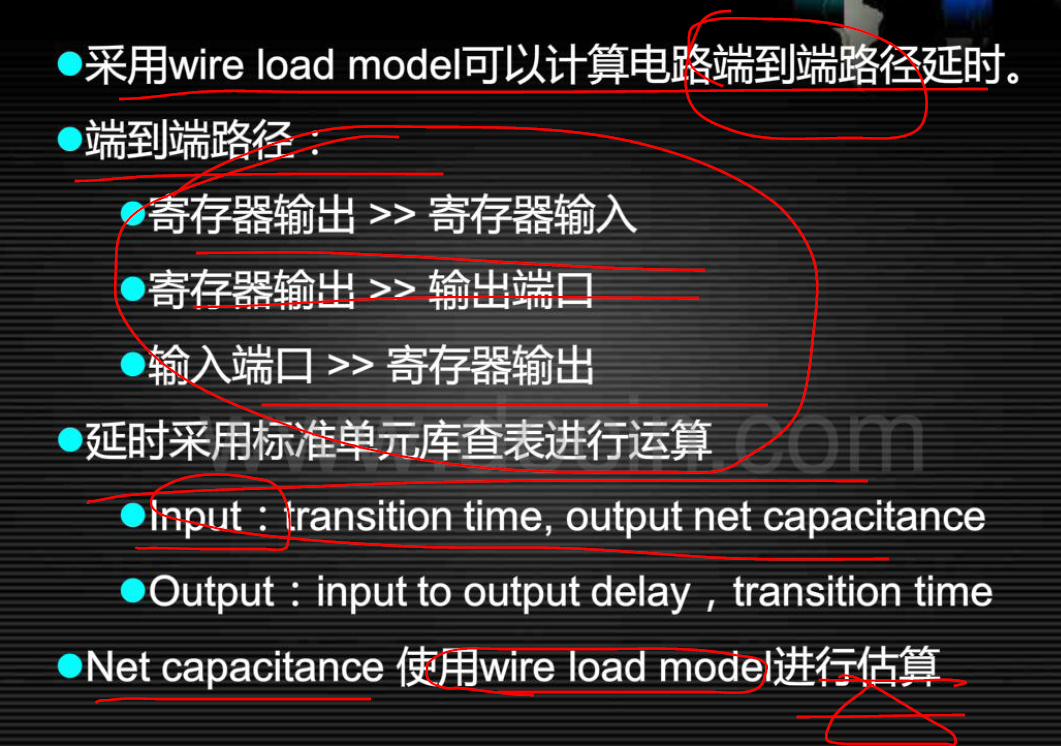

延时计算:

静态时序分析检查了电路时序上是否满足要求,而形式验证检查了电路功能的正确性。形式验证的本质是一个比较器,其功能就是比较两个电路功能是否完全一致。由于在综合过程中电路节点名称可能改变,因此可以使用形式验证工具找到RTL代码中节点在网表中对应的节点。

数字后端设计流程

APR(自动布局布线)工具Synopsys的ASTRO

APR需要完成:

1.芯片布图

2..标准单元的布局

3.时钟树和复合树综合

4.布线

5.DRC

6.LVS

7.DFM