组合逻辑电路

组合逻辑的特点

组合逻辑电路中,任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。

逻辑功能的描述

从理论上来讲,逻辑图本身就是逻辑功能的一种表达方式。然而在许多情况下,用逻辑图所表示的逻辑功能不够直观,往往还需要把它转换成逻辑函数式或者真值表的形式,以使电路的逻辑功能更加直观、明显。

组合逻辑电路的分析方法与设计方法

组合逻辑的分析方法

通常采用的分析方法就是从电路的输入到输出逐级写出逻辑函数式,最后得到表示输出与输入关系的逻辑函数式。然后使用公式法或者卡诺图化简的方法将所得的函数式化简或变换,使逻辑关系更加明显。

组合逻辑电路的设计方法

1.进行逻辑抽象

a.分析事件的因果关系,确定输入变量与输出变量。

b.定义逻辑状态的含义

c.根据给定的因果关系列出逻辑真值表

2.写出逻辑函数式

3.选定器件类型(与门、或门。。。)

4.将逻辑函数化简或变换成适当的形式

5.根据化简或变换后的逻辑函数式,画出逻辑电路的连接图

6.工艺设计

常用的组合逻辑电路

1.编码器

普通编码器、优先编码器

2.译码器

二进制译码器、显示译码器

3.数据选择器

4.加法器

1 半加器(无进位)

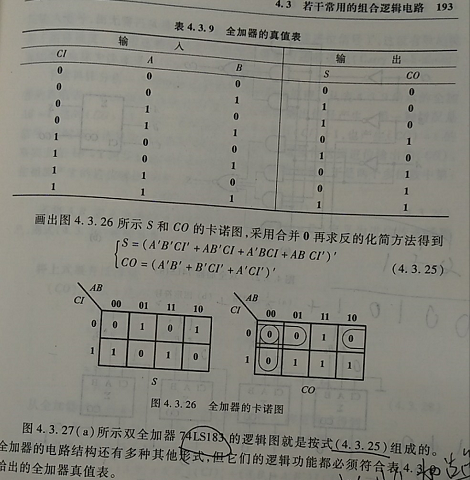

2.全加器

A,B,Cl取异或,进位端两两取反

2.多位加法器

1.串行进位加法器,上一级的进位输出当下一级的进位输入,运算速度慢。

2.超前进位加法器

为了提高运算速度,必须设法减小由于进位信号逐级传递所耗费的时间。

展平逻辑,将每位的输出推导到当前输入值与低位输入值的关系,从而减小不同位之间的等待传递时间。

提到运算速度的同时,电路面积大大增加。

越高位的逻辑越复杂

5.数值比较器

竞争与冒险

两个输入电平同时往相反的方向跳变称为竞争;

由于竞争使得输出上产生了毛刺的现象称为竞争--冒险

检查竞争冒险的方法:代数法、卡诺图法、实验法

消除竞争--冒险的方法:接入滤波电容,引入选通逻辑,修改逻辑设计(增加冗余项)